(5) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОбРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU920716A2 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU883897A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Устройство для вычисления корня пятой степени | 1976 |

|

SU691848A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

I

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной реализации операции вычисления квадратных корней из аргумента и его куба в различных устройствах и системах автоматики, телемеханики и телеизмерения и контроля, автоматического управления и т.д.

Известно цифровое устройство для вычисления квадратного корня, содержащее -сумматоры, регистры З

Однако устройство не предназначено для одновременного вычисления квадратного корня также из куба аргумента .

Наиболее близким По технической сущности к предлагаемому является устройство для вычисления элементарных функций, содержащее четыре од- норазрядных сумматора-вычитателя., четыре регистра (четвертый регистр является блоком сдвига) блок памяти, блок анализа анака.и блок управленйя, первые выходы первого, второго и третьего регистров соединены соответственно с первыми входами первого, второго и четвертого сумматоров-вычитателей, выходы которых соединены соответственно с первыми входами этих регистров, второй выход первого регистра соединен с первым входом блока анализа,на второй вход которого подсоединен второй выход третьего регистра, второй выход второго регистра соединен с входом четвертого сдвигающего регистра, лервый выход блока памяти соединен с вт( входами первого

1S и Второго сумматоров-вычитателей, второй выход блока памяти соединен с первым входом третьего сумматора-вычитателя, на второй вход которого подсоединен выход четвертого

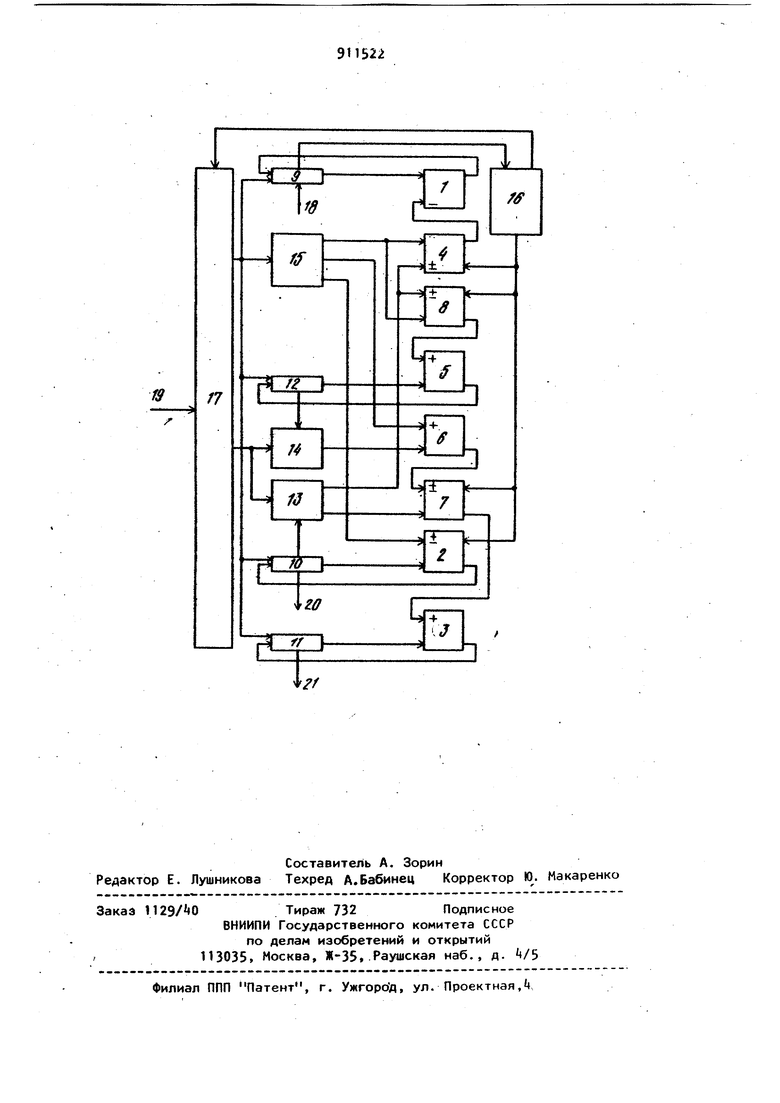

20 сдвигающего регистра,на управляющие входы первого, второго и третьего сумматоров-вычитателей подсоединен первый выход блока анализа, второй выход которого соединен с управляющим входом четвертого сумматора-вычитателя, выход третьего сумматоравычитателя соединен с вторым входом четвертого сумматора-вычитателя, выходы блока управления соединены соответственно с управляющими входа ми всех регистров и входом блока па мяти 2. Устррйство предназначено для вычисления либо квадрата аргумента X, либо для вычисления квадратного корня из аргумента X. Недостатком этого устройства является его ограниченные функциональ ные возможности, поскольку оно не предназначено для вычисления квадра ного корня из аргумента в третьей с пени . Цель изобретения - расширение класса решаемых задач за счет возможности вы числения как функции у X, так и функции у УЗГ Поставленная цель достигается тем, что е преобразователь, содержащий три регистра, четыре сумматора-вычитателя, блок памяти, блок синхронизации, дешифратор нуля и первый блок сдвига, причём выходы первого, второго и третьего сумматоров-вычитателей соединены соответственно с входами первого, второго и третьего регистров, выходы младшего разряда каждого из которых соединены с первыми входами соответствующих сумматоров-вычитателей,первый выход блока памяти соединен с первым входом четвертого сумматоравычитателя, выход которого соединен со втар««м входом первого сумматоравычитателя, второй выход блока памяти соединен со вторым входом второго сумматора-вычитателя, выходы разрядов первого регистра соединены с вхо дами дешифратора нуля, первый тактовый выход блока синхронизации соединен с управляющими входами первого, второго, третьего регистров,блок памяти, первый выход первого блока сдвига соединен со вторым входом чет вертого сумма тора-еыч14тателя, дополнительно введены четыре сумматоравычитателя, второй блок CRBtftra и четвертый регистр, выход младшёУо разряда которого соединен с первым в}(одом пятого сумматора-вычитателя, выход которого соединен с входом чет вертого регистра, 1Выход разрядов которого соединен с входом второго бло ка сдвига, выход которого соединен с первым входом шестого сумматоравычитателя, второй вход которого подключен к третьему выходу блока памяти, второй выход первого блока сдвига соединен с первым входом седьмого сумматора-вычитателя, второй вход которого соединен с выходом шестого сумматора-вычитателя, выход седьмого суммагора-вычитателя соединен со вторым входом третьего сумматора-вычитателя, первый выход блока памяти соединен с первым входом восьмого сумматора-вычитателя, первый выход первого блока сдвига соединен со вторым входом восьмого сумматоравычитателя, выход которого соединен со вторым входом пятого сумматора-вычитателя, первый выход дешифратора нуля соединен с входами управления седьмого и восьмого сумматоров-вычитателей, а второй - с входом останова блока синхронизации, первый и второй тактовые выходы которого соединены с управляющими входами четвертого регистра и второго блока сдвига соответственно. На чертеже представлена блок-схема преобразователя. Преобразователь содержит сумматоры-вычитатели 1-8,регистры 9-12,блоки 13 и И сдвига, блок 15 памяти, дешифратор 16 нуля, блок 1/ синхронизации, вход 18 аргумента, вход 19 запуска, выходы 20 и 21. Сумматоры-вычитатели 1-8 могут быть реализованы в виде одноразрядной комбинационной схемы сложения-вычитания. Блоки сдвига ТЗ и И могут быть реализованы в виде матричных сдвигателей либо в виде сдвигающих регистров и сумматора. Блок 15 памяти выполнен в виде одностороннего запоминающего устройства, причем по одному адресу (номеру итерации i) записаны три слова: константа вида .(первый выход), константа вида 2 (второй выход) и константа вида 2--VI (третий выход) , а выборка их производится одновременно каждым тактовым импульсом поразрядно. Дешифратор 16 нуля предназначен для определения оператора q и сигнала остановки процесса вычисления при равенстве нулю коди в регистре 9Он имеет три выхода (содержание регистра 9 больше, меньше или равно нУлю), которые через элементы И (на

591

вторые входы которых подается импульс конца итерации) соответственно соединены с триггером (выход которого является первым выходом дешифратора 16) и со вторым выходом дешифратора 16. Блок 17 предназначен для синхронизации работы всех блоков устройства и может быть реализован в виде схемы, содержащей управляющий генератор тактовых импульсов, элементы И и ИЛИ, cчetчики, дешифраторы, триггеры и элементы задержки. Блок 17 имеет два выхода, первый из которых

isYv v-nY- -7 -7 J V

iVi i , .. t iJ

q,j sig n y

Zj + q.X.-2-2-:+ Vx

Zo 0; Z.,v X Vr

,, ,- + + q|2 ;

Uo- O; U.,V - U

Цикл вычисления состоит из i итераций, максимальное число которых равно п, где n - число разрядов аргумента. Все соотношения алгоритма вычисляются параллельно. Каждое соотношение алгоритма в одной итерации вычисляется последовательно за

тактов, где m Iog,,n { - чис- зо 15 выдается последовательность такло дополнительных защитных разрядов для компенсации погрешности усечения чисел при сдвиге. Значение у- вычисляется в cy waTopax-вычитателях 1 и . Логическое условие YJ О определяется в дешифраторе 16 нуля. Значение Z вычисляется е сумматорахвычитателях 5 и 8; значение Х- - в сумматоре-вычитателе 2; значение Щ в сумматорах-выуитателях 3,.6 и 7; значения Щ22 и Х.-32 получаются в блоке 13 сдвига (первый и второй выходы..соответственно); знам,ение Zj32 - в блоке 14 сдвига Цифровой преобразователь работает следующим образом. Первовчально все регистры 9-12 .устанавливаются а нулевое состояние. По входу 18 на регистр 9 подается код аргумента X, по входу 19 - стартовый импульс, который запускает управляемый генератор тактовых импульсов в блоке 17 синхронизации, и с выходов последнего на регистры 9-12, блоки 13 и 14 сдвига и бдок 15 памяти начинают поступать тактовые импульсы В любой i-ой итерации на блоки 13 и 14 сдвига и блок 15 памяти выда15226

соединен с входом блока 15 памяти и управляющими входами регистров 912, а второй - с вх одами блоков 13 и 1 сдвига, на которые подается импульс

S конца итерации для сдвига предыдущего содержания.

Процесс вычисления квадратного корня из аргумента и его куба осуществляется следующим образом.

10 Процесс вычисления основан на одновременное решении в итерационном процессе систе «й разностных рекуррентных cootнoшeний

+1 при yi О

, i - 0,1,2,... ,п

, 1-1 при у О

ется импульс сдвига, который определяет величину сдвига и адрес констант 2S в данной итерации. В первой итерации сдвиг в блоках 13 и 1 сдвигу не выполняется. Сдвиг в блоках 13 и 14 производится за один такт. Затем на .регистры 9-12, блоки 13 и 1 и блок товых импульсов для продвижения содержаний названных блоков на сумматоры-вычитатели 1-7. Результаты операций каждой итерации поступают с выходов сумматоров-вычитателей 1-3 и 5 младшими разрядами вперед в освобождающиеся старшие разряды при продвижении содержаний регистров 9-12.и продвигаются к началу (в сторону младших разрядов) этих регистров. После выполнения n + m тактов в регистрах 9-2 содержатся результаты i-ой итерации. С регистра 9 на вход дешифратора 16 поступает значение у-, которое сравнивается с нулем. На первом выходе дешифратора 16 формируется-значение цифры оператора О для следующей итерации При у 0 значение q +1, У; О значение -1. Эти чения определяют режим работы сумматоров-вычитателей 2,4,7 и 8. При q- 4-1 сумматоры-вычитатели работают в режиме сложения, при о: -1 их режим меняется на вычитание.Сумматор-вычитатель 1 работает только в режиме вычитания, а сумматоры-вычитатели и 6 работают только в режиме сложения. При выполнении условия у О (т.е. при нулевом содержании в регистре 9) в дешифраторе 16 нуля формируется сигнал останова (на втором выходе) и блок 7 прекрашает выдгеать тактовые импульсы, поскольку, процесс вычисления закончен. При этом в регистре 10. (на выходе 20) со держится значение функции yiT, , а в регистре 11 (на выходе 21) содержит ся значение функции -/Т Для больотнства значений аргумента X требуе мое количество итераций значительно меньше п. Для получения точности меньше половины последнего разряда П только для одного значения.X требуется выполнить итерацию.Основ ное число итерамий равно 6-10 для П 12. Достоинством предложенного преобразователя по отношени к известному является то, что он позволяет сократить число итераций в одном цикле вычисления для большинства значений аргументов X, что повыша т производительность вычислений. Все схемотехнические решения данного преобразователя являются ст дартными в цифровой вычислительной технике и выпускаются промышленностью в интегральном исполнении. Данный преобразователь может быть изготовлен в виде одной {iHC. Формула изобретения Цифровой функциональный преобразователь, содержаи(ий три регистра, четыре сумматора-вычитателя, блок памяти, блок синхронизации, дешифратор нуля и первый блок сдвига,при чем выходы первого, второго и треть го сумматоров-вычитателей соединены соответственно с входами первого, второго и третьего регистров выходы младшего разряда каждого из которых соединены с первыми входами соответ ствующих сумматоров-вычитателей, первый выход блока памяти соединен с первым входом четвертого сумматор вычитателя, выход которого соединен со вторым входом первого сумматоравычитателя, второй выход блока памя ти соединен со вторым входом второг 9 - 8 сумматора-вычитателя, выходы разрядов первого регистра соединены с входами дешифратора нуля, первый тактовый выход блока синхронизации соединен с управляющими входами первого, второго, третьего регистров, блока памяти, первый выход первого блока сдвига соединен со вторым входом четвертого сумматора-вычитателя, отличающийся тем, что, с. целью расширения класса решаемых задач за счет возмо))а4ости вычисления как Дункции у X , так и функции у «Vx, в него введены четыре сумматора-вымитателя, второй блок сдвига и четвертый регистр, выход младшего разряда которого соединен с первым входом пятого сумматора-вычитателй, выход которого соединен с входом четвертого регистра, выход разрядов которого соединен с входом второго блока сдвига, выход которого соединен с первым входом шестого сумматора-вычитателя, второй вход которого подключен к третьему выходу блока памяти, второй выход первого блока сдвига соединен с первым Входом седьмого сумматора-вычитателя, второй вход которого соединен с выходом шестого сумматора-вычитателя, выход седьмого сумматора-оычитателя соединен со вторым входом третьего сумматора-вычитателя.первый выход блока памяти соединен с первым входом восьмого сумматора-вычитателя, первый выход первого блока сдвига соединен со вторым входом восьмого сумматора-вычитателя, выход которого соединен со вторым входом пятого сумматора-вычитателя, первый выход дешифратора нуля соединен с входами управления седьмого и восьмого сумматоров-вычитателей, а второй выход - с входом останова блока синхронизации, первый и второй тактовые выходы которого соединены с управляющими входами четвертого регистра и второго блока сдвига соответственно. Источники информации, принятые во внимание при экспертизе 1.IEEE Transon Conputers. 1972, V 21, tf 8, p. 837-8«7. 2.Авторское свидетел эство СССР tP 553612, кл. G Об F 7/38, 1975 (прототип).

Авторы

Даты

1982-03-07—Публикация

1980-04-10—Подача