(Л

С

Изобретение относится к вычислительной технике, может быть использовано в комбинированном запоминающем устройстве (электрически программируемом и технологически программируемом). Целью изобретения является увеличение информационной емкости матричного накопителя. Устройство содержит адресные шины, разрядные шины, стирающие шины, в перекрестиях которых размещены ячейки памяти. Каждая из ячеек памяти состоит из запоминающего транзистора, адресного МДП-транзистора. накопительного конденсатора. Изобретение может быть использовано не только для накопителей с виртуальным подключением разрядных шин, но и с постоянным заземления шину нулевого потенциала. 1 з.п. ф-лы, 2 ил.

Изобретение относится к области вычислительной техники. Оно может быть использовано в комбинированном постоянном запоминающем устройстве (электрически программируемом и технологически программируемом).

Целью изобретения является увеличение информационной емкости матричного накопителя.

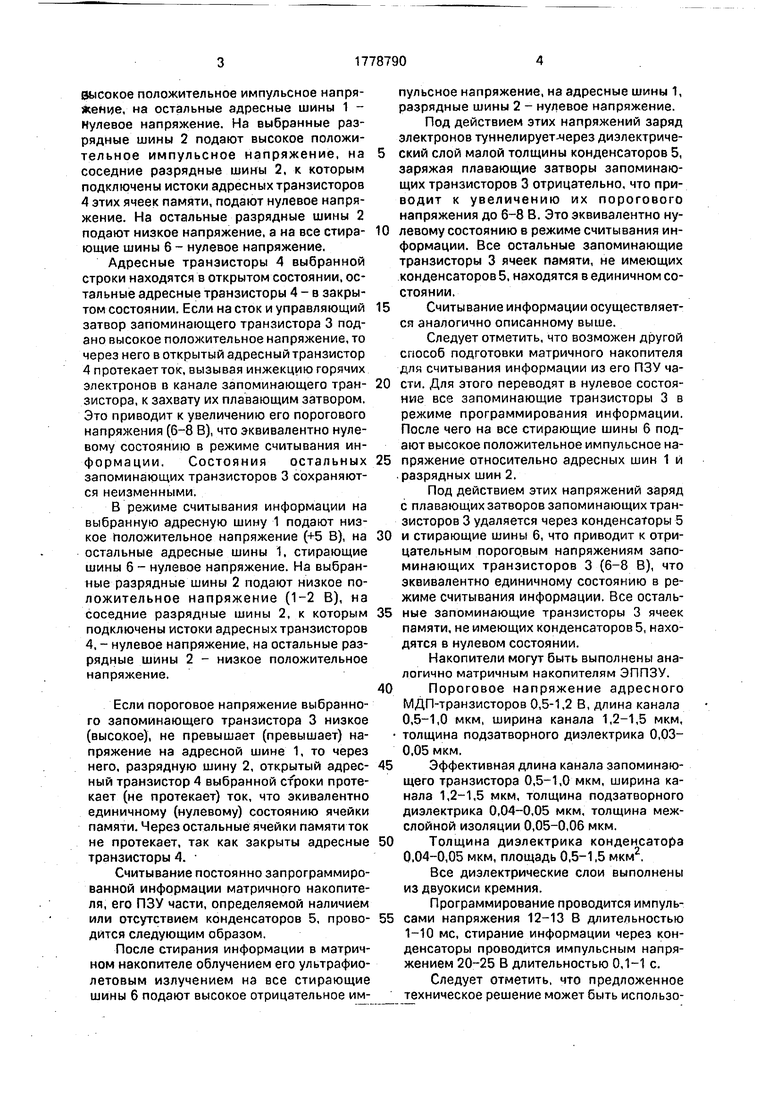

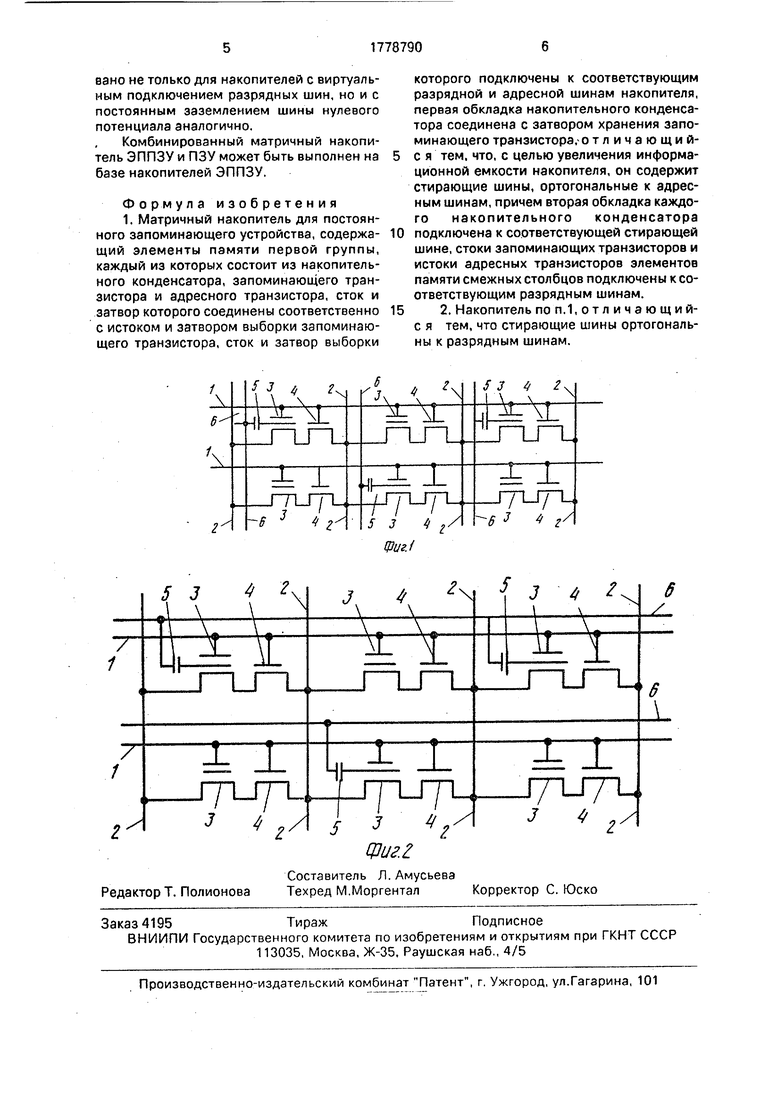

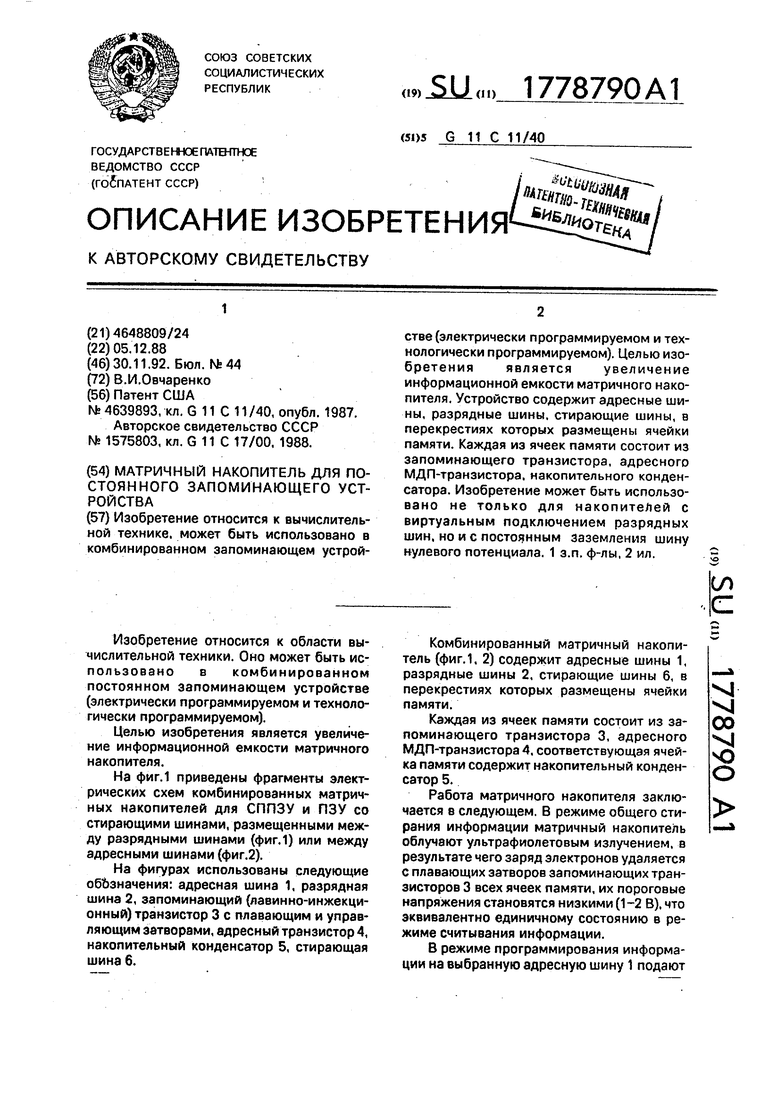

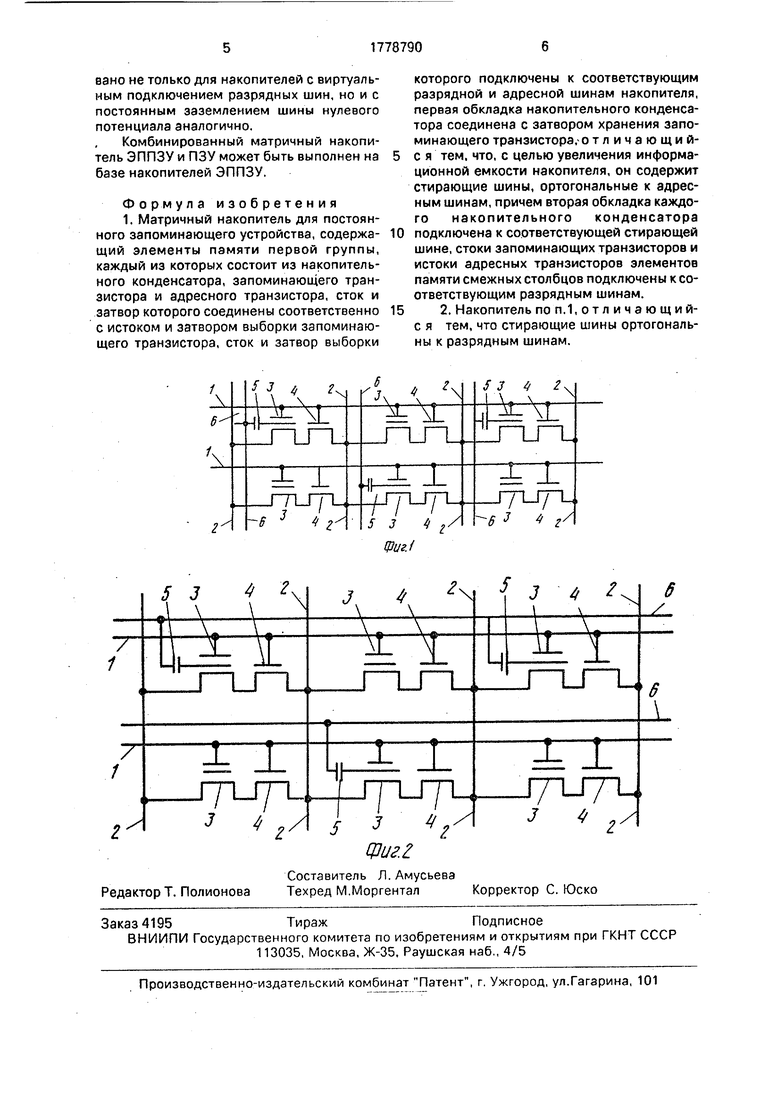

На фиг.1 приведены фрагменты электрических схем комбинированных матричных накопителей для СППЗУ и ПЗУ со стирающими шинами, размещенными между разрядными шинами (фиг.1) или между адресными шинами (фиг.2).

На фигурах использованы следующие обозначения: адресная шина 1, разрядная шина 2, запоминающий (лавинно-инжекци- онный) транзистор 3 с плавающим и управляющим затворами, адресный транзистор 4, накопительный конденсатор 5, стирающая шина 6.

Комбинированный матричный накопитель (фиг.1. 2) содержит адресные шины 1, разрядные шины 2, стирающие шины 6, в перекрестиях которых размещены ячейки памяти.

Каждая из ячеек памяти состоит из запоминающего транзистора 3, адресного МДП-транзистора 4, соответствующая ячейка памяти содержит накопительный конденсатор 5.

Работа матричного накопителя заключается в следующем. В режиме общего стирания информации матричный накопитель облучают ультрафиолетовым излучением, в результате чего заряд электронов удаляется с плавающих затворов запоминающих транзисторов 3 всех ячеек памяти, их пороговые напряжения становятся низкими (1-2 В), что эквивалентно единичному состоянию в режиме считывания информации.

В режиме программирования информации на выбранную адресную шину 1 подают

VJ ч| 00 Ю О

Высокое положительное импульсное напряжение, на остальные адресные шины 1 - Нулевое напряжение. На выбранные разрядные шины 2 подают высокое положительное импульсное напряжение, на соседние разрядные шины 2, к которым подключены истоки адресных транзисторов А этих ячеек памяти, подают нулевое напряжение. На остальные разрядные шины 2 подают низкое напряжение, а на все стирающие шины 6 - нулевое напряжение.

Адресные транзисторы 4 выбранной строки находятся в открытом состоянии, остальные адресные транзисторы 4-е закрытом состоянии. Если на сток и управляющий затвор запоминающего транзистора 3 подано высокое положительное напряжение, то через него в открытый адресный транзистор 4 протекает ток, вызывая инжекцию горячих электронов в канале запоминающего транзистора, к захвату их плавающим затвором, Это приводит к увеличению его порогового напряжения (6-8 В), что эквивалентно нулевому состоянию в режиме считывания ин- формации. Состояния остальных запоминающих транзисторов 3 сохраняются неизменными.

В режиме считывания информации на выбранную адресную шину 1 подают низкое положительное напряжение (+5 В), на остальные адресные шины 1, стирающие шины 6 - нулевое напряжение. На выбранные разрядные шины 2 подают низкое положительное напряжение (1-2 В), на соседние разрядные шины 2, к которым подключены истоки адресных транзисторов 4, - нулевое напряжение, на остальные разрядные шины 2 - низкое положительное напряжение.

Если пороговое напряжение выбранного запоминающего транзистора 3 низкое (высокое), не превышает (превышает) напряжение на адресной шине 1, то через него, разрядную шину 2, открытый адресный транзистор 4 выбранной строки протекает (не протекает) ток, что экивалентно единичному (нулевому) состоянию ячейки памяти. Через остальные ячейки памяти ток не протекает, так как закрыты адресные транзисторы 4.

Считывание постоянно запрограммированной информации матричного накопителя, его ПЗУ части, определяемой наличием или отсутствием конденсаторов 5, проводится следующим образом.

После стирания информации в матричном накопителе облучением его ультрафиолетовым излучением на все стирающие шины 6 подают высокое отрицательное импульсное напряжение, на адресные шины 1, разрядные шины 2 - нулевое напряжение.

Под действием этих напряжений заряд электронов туннелирует-через диэлектрический слой малой толщины конденсаторов 5, заряжая плавающие затворы запоминающих транзисторов 3 отрицательно, что приводит к увеличению их порогового напряжения до 6-8 В. Это эквивалентно ну0 левому состоянию в режиме считывания информации. Все остальные запоминающие транзисторы 3 ячеек памяти, не имеющих конденсаторов 5, находятся в единичном состоянии.

5 Считывание информации осуществляется аналогично описанному выше.

Следует отметить, что возможен другой способ подготовки матричного накопителя для считывания информации из его ПЗУ ча0 сти. Для этого переводят в нулевое состояние все запоминающие транзисторы 3 в режиме программирования информации. После чего на все стирающие шины 6 подают высокое положительное импульсное на5 пряжение относительно адресных шин 1 и разрядных шин 2.

Под действием этих напряжений заряд с плавающих затворов запоминающих транзисторов 3 удаляется через конденсаторы 5

0 и стирающие шины 6, что приводит к отрицательным пороговым напряжениям запоминающих транзисторов 3 (6-8 В), что эквивалентно единичному состоянию в режиме считывания информации. Все осталь5 ные запоминающие транзисторы 3 ячеек памяти, не имеющих конденсаторов 5, находятся в нулевом состоянии.

Накопители могут быть выполнены аналогично матричным накопителям ЭППЗУ.

0 Пороговое напряжение адресного МДП-транзисторов 0,5-1,2 В, длина канала 0,5-1,0 мкм, ширина канала 1,2-1,5 мкм, толщина подзатворного диэлектрика 0,03- 0,05 мкм.

5 Эффективная длина канала запоминающего транзистора 0,5-1,0 мкм, ширина канала 1,2-1,5 мкм, толщина подзатворного диэлектрика 0,04-0,05 мкм, толщина меж- слойной изоляции 0,05-0,06 мкм.

0 Толщина диэлектрика конденсатора 0.04-0,05 мкм, площадь 0,5-1,5 мкм2.

Все диэлектрические слои выполнены из двуокиси кремния.

Программирование проводится импуль5 сами напряжения 12-13 В длительностью 1-10 мс, стирание информации через конденсаторы проводится импульсным напряжением 20-25 В длительностью 0,1-1 с.

Следует отметить, что предложенное техническое решение может быть использовано не только для накопителей с виртуальным подключением разрядных шин, но и с постоянным заземлением шины нулевого потенциала аналогично.

Комбинированный матричный накопитель ЭППЗУ и ПЗУ может быть выполнен на базе накопителей ЭППЗУ.

Формула изобретения 1. Матричный накопитель для постоянного запоминающего устройства, содержащий элементы памяти первой группы, каждый из которых состоит из накопительного конденсатора, запоминающего транзистора и адресного транзистора, сток и затвор которого соединены соответственно с истоком и затвором выборки запоминающего транзистора, сток и затвор выборки

0

5

которого подключены к соответствующим разрядной и адресной шинам накопителя, первая обкладка накопительного конденсатора соединена с затвором хранения запоминающего транзистора,-о т личающий- с я тем, что, с целью увеличения информационной емкости накопителя, он содержит стирающие шины, ортогональные к адресным шинам, причем вторая обкладка каждого накопительного конденсатора подключена к соответствующей стирающей шине, стоки запоминающих транзисторов и истоки адресных транзисторов элементов памяти смежных столбцов подключены к соответствующим разрядным шинам.

| Патент США №4639893, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Авторское свидетельство СССР № 1575803, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-11-30—Публикация

1988-12-05—Подача