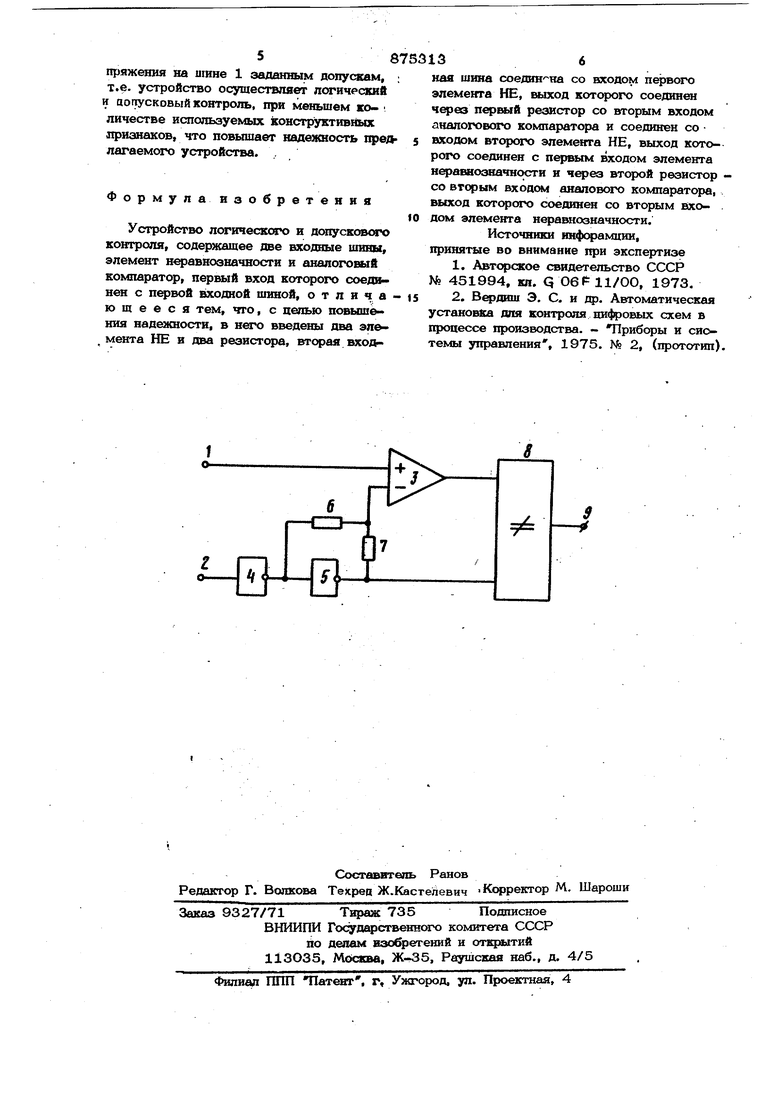

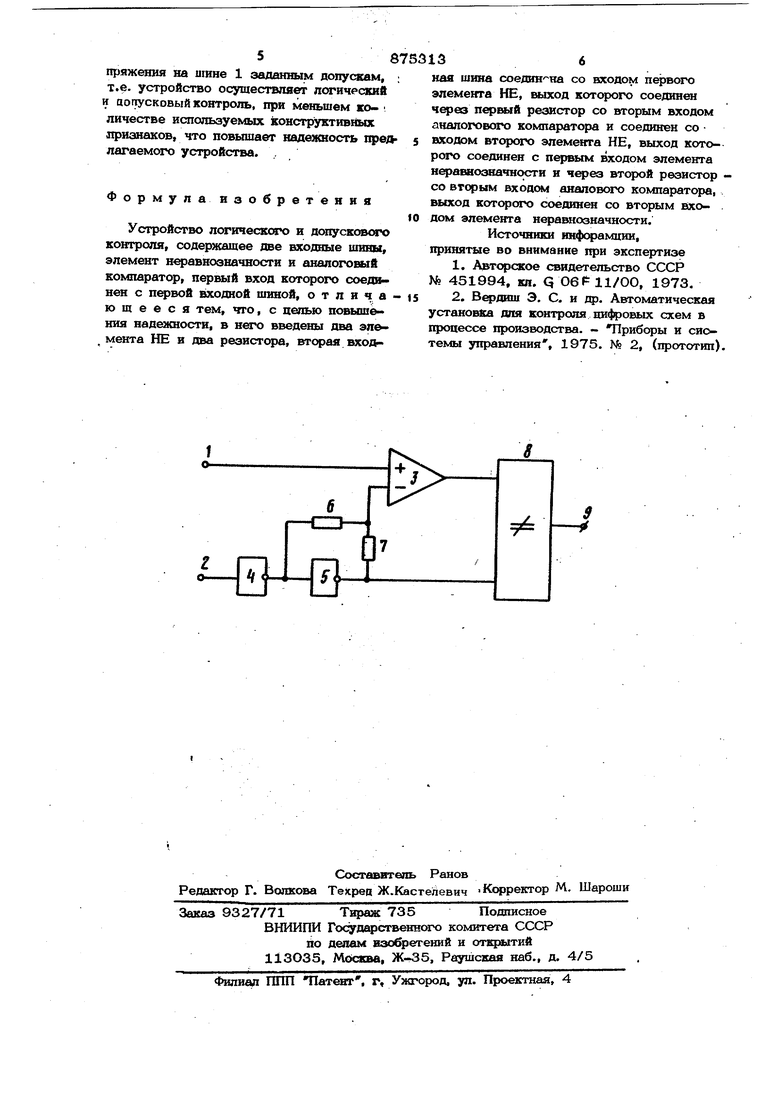

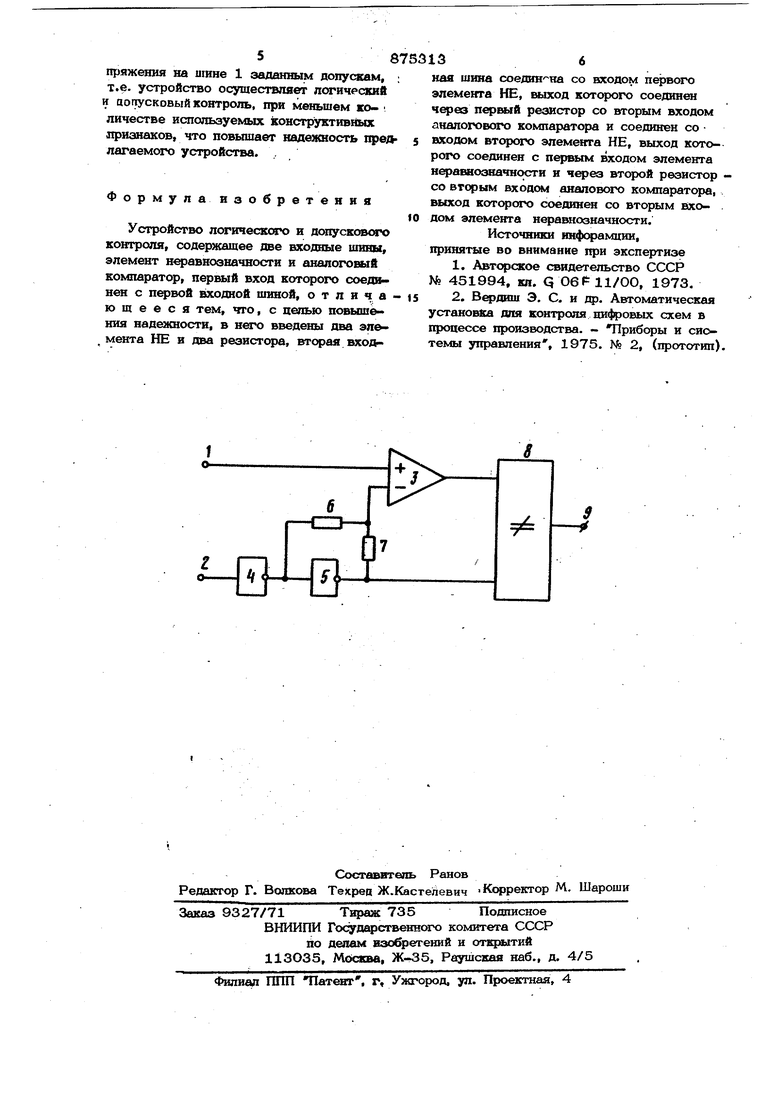

Изобретение относится к технической диагностике и может быть использовано в устройствах для проверки логичесЕЗОс ,схем , Известно устройство логического и до пускового контроля, содержащее ок к еж тропя уровней, преобразователь урошей и цифровой компаратор I . Недостатком известного устройсугва является его относительная сложность. Известно также усгройство логическог и допускового контроля, содержащее .две входные шины, элемент неравнозначности два аналоговых компаратора, элемент . ИЛИ, первая входная шина соединена с первым входом элемента неравнозначноети и с первыми входами аналоговых компараторов Г2Д . Недостатком известного устройства 1тляется его относительная сложность, гго 1ФНВОДИТ к уменьшению надехшости. Цепь изобретения - повыш ше иадеж-) ностн. Поставденная цель достигается тем, что в устройство логического и допуско-i во1ч контроля, содержащее две входные шины, элемент неравнозначности и аналоговый компаратор, первый вход которого соединен с первой входной шиной, введены два элемента НЕ и два резистора, вторая входная шива соединена со входом первого элемента НЕ, выход которого соединен через первый резистор со вторым входом аналового компаратора и соединен со входом второго элемента НЕ, выход которого соединен с первым входом элемента неравнозначности и через второй резистор со вторым входом аналового компаратора, выход соединен со вторым входом элемента неравнозначности. На чертеже схематично представлено устройство логического и допускового контроля. Устройство содержит первую и вторую входЕ ые шины 1 и 2, аналоговый компаратор 3, .элементы 4 и 5 НЕ, резисторы 38 б и 7, элемент 8 неравнозначности и входную шину 9, Входная шина 1 соединена с первым входом аналового компаратора 3, ,вход ная шина 2 соединена со входом элемен та 4 НЕ, выход которого соединен qejjea резистор 6 со вторым входом aнaлoвoгq компаратора 3 и соединен со входом элемента 5 НЕ, выход которого соединен с первым входом элемента 8 неравнознач ности и соединен через резистор 7 со вторым входом аналового компаратора 3, выход которого соединен. со вторым входом элемента 8 неравнозначности, выход которого соединен с выходной шиной 9. Устройство предназначено преимущественно для проверки логических схем с вы сокоомными входами и низкоомными выходами, например К/МСЯП - микросхем, и логических блоков, вьшолненных на таких микросхемах, поэтому для определенности будем рассматривать работу схемы сравнения при подключении к ее входным шинам 1 и 2 выводов К/МОП - микросхем. Устройство работает следукшшм образом. На шину 1 подается логический сигнал с выхода проверяемой микросхемы, а на шину 2 - с одноименного выхода эталонной (заведомо исправной) микросхемы то го же типа, что и проверяемая микросхем причем предполагается, что на эти микро схемы поданы совпадающие наборы воздей ствий (логических сип1алов), номинальны выходные напр11жения этих микросхем соответствуют номинальным напряжени5Ш логических уровнЫ шсодного сигнала элемента 4 НЕ, а проверяемая, эталонная микросхема, элементы НЕ и элемент 8 неравнозначности подключены к общим шинам питания. Характерным для К/МОП-микросхем является то, что установленные техническими условиями допускаемые отклонения напряжений шлходных уровней О и от их номинальных значений, принятых равными напряжениям на общей шине и на шине питания соответственно, по .абсолютной величине ссоападают. Номинал ные сопротивления резисторов 6 и 7 выбраны такими, что они удовлетворяют соотношениюRa f, Е гдеЙ,р|21 - номинальные сопротивления резисторов б и 7 соответственно;Е - номинальное значение напряжения на шине питания; 3 i - абсолютная величина установленного техническими условиями на проверяемую микросхему допускаемого отклонения напряжений выходных уровней от их номинальных значений. Поскольку эталонная микросхема считается исправной, то сигнал на шине 2 всегда принимает значение либо О, либо 1 и приводит в соответствующее действие элемент 4 НЕ. При сигнале О на шине 2 на выходах элементов 4 и 5 НЕ имеют место сигналы и СГ соогветственно с напряжениями, почти точно равными нулю и Е соответственно, при этом на инвергируюший вход компаратора 3 с точки соединения резисторов 6 и 7 поступает напряжение, почти точно равное Л , Если напряжение на шине 1 не привышает величины Д , т.е. находится в пределах, допустимых для напряжения логического О, то на выходе компаратора 3 имеет место логический сигнал О, при этом на обоих входах элемента 8 неравнозначности имеют место одинаковые логические сигналы О, поэтому он (формирует на выходе 9 логический сигнал О, в противном случае - логический сигнал 1. При сигнале I на шине 2 на выходах элементов 4 и 5 НЕ имеют место и I соответственно с насигналы О пряжениями, почти точно равными Е и нулю соответственно, при этом на инвертирующий вход компаратора 3 с точки соединения резисторов б и 7 поступает напряжение, почти точно равное (Е-д). Если напряжение на шине 1 превышает величину (Е-Д), т.е. находится в преде- лах, допустимых для напряжения логической 1, то на выходе компаратора 3 имеет место логический сигнал 1, при этом на обоих входах элемента 8 неравнозначности имеют место одинаковые , поэтому он форгические сигналы 9 логический сигнал мирует на шлходе О, в противном случае - логический сигнал 1. Таким образом, при обоих значениях логического сигнала на шине 2 устройство формирует на шине 9 логический сигнал Р при соответствии ,сигнала на шине 1 сигналу на Ш1ше 2 по логическому значению и соответствии напряжения на шине 1 заданным допускам и логический сигнал I - при несоответствии сигнала на шине 1 сигналу на,шине 2 по лог ческому значению или при несоответствии напряжения на тине 1 заданным допусжам, т.е. устройство осуществляет лсяичяский и аопусковый контроль, при меньшем ко- личестве используемых конструктивных признаков, что повышает надежность пред латаемого устройства. ,, Формула изобретения Устройство логического и допускового контроля, содерхсашее две входные шины, элемент неравнозначности и аналоговый компаратор, первый вход которого с входной шиной, о т л и ч а ю ш е е с я тем, что, с целью повыше ния надежности, в него введены два эя& мента НЕ и два резистора, вторая входная шина соедин на со входом первого элемента НЕ, клход которого соединен через первый резистор со вторым входом аналогового компаратора и соединен со входом второго элемента НЕ, выход которого соединен с первым входом элемента неравнозначности и второй резистор со вторым входом аналового компаратора, выход котсфого соединен со вторым входом элемента неравнозначности. Источники инфqpaмuшI, принятые во внимание при экспертизе 1.Авт фское свидетельство СССР № 451994, кп. Q Об Р 11/00, 1973. 2.Вердиш Э. С. и др. Автоматическая установка для контроля ш{4ровых схем в процессе производства. - Приборы и СИО темы управления , 1975. № 2, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство логического и допускового контроля | 1985 |

|

SU1298699A2 |

| Многоканальное устройство для проверки логических микросхем | 1985 |

|

SU1242864A1 |

| Устройство для контроля статических параметров микросхем | 1978 |

|

SU746441A1 |

| Устройство для проверки логических микросхем | 1985 |

|

SU1285413A1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2000 |

|

RU2190927C2 |

| Устройство для автоматического определения ориентации микросхем | 1987 |

|

SU1458984A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Формирователь сигналов сброса для блоков памяти | 1983 |

|

SU1108504A1 |

Авторы

Даты

1981-10-23—Публикация

1980-02-20—Подача