Изобретение относится к цифровой вычислительной технике и может ис- . пользоваться либо в качестве пери- . ферийного процессора для отладки программ и микропрограмм пользователя, либо в качестве вычислительного модуля в надежных вычислительных системах.

Известны микропрограммные процессоры, содержащие блок памяти микрокоманд, регистр микрокоманды, регистр адреса микрокоманды, регистр признака переходаг блок управления, арифметический блок, поиск неисправностей аппаратуры и откладка программ пользователя в которых осуществляется программными средствами tl.

Недостатком известного микропрограммного процессора являются большие затраты времени на отладку программ ft диагностику неисправностей аппаратуры.

Наиболее близким по технической сущности к предлагаемому является микропрограммный процессор, содержащий блок управления, блок индикации неисправностей, два регистра адреса микрокоманд, два регистра микрокоманд, два арифметических блока, два регистра признака перехода, две

памяти, три коммутатора, блок синхронизации 2 .

Недостатком устройства является низкая производительность при отладке программ, а также невозможность диагностики всех возможных неисправностей из-за программной недоступности.

Цель изобретения - повьлаение коэффициента использования оборудования путем автоматизации отладки программ и диагностики неисправностей микропрограммного процессора, которая приводит к уменьшению временных затрат на отладку и диагностику.

Поставленная цель достигается тем, что в микропрограммный процессор, содержащий блок управления, с первого по пятый выходы которого соединены соответственно с первыми входами блока индикации неисправностей, первого регистра признака перехода, первого регистра адреса микрокоманд, блока синхронизации и первого арифметического блока, первый и второй выходы которого соединены соответственно со вторым входом первого рюгистра адреса микрокоманд и с первым входом блока управления, второй вход которого соединен с первым выходом первого регистра микрокоманд, второй

и третий выходы которого соединены соответственно с третьим входом первого регистра адреса микрокоманд и со вторым входом первого регистра признака перехода, выход которого и первого коммутатора соединены соответственно с четвертым и пятым входами первого регистра адреса микрокоманд, выход которого через первую память соединен со входом первого регистра микрокоманд, вторую память, второй арифметический блок, входы которого соединены с первыми выходами второго и третьего коммутаторов , выход второго арифметического блока соединен с первым входом второго коммутатора, второй и третий вУходы которого соединены соответственно с первым входом второго регистра адреса микрокоманды и вторым входом блока синхронизации, выход которого соединен с первым входом третьего коммутатора, второй и третий выходы которого соединены соответственно со вторым входом второго регистра адреса микрокоманд и с первым входом второго регистра признака перехода, второй регистр микрокоманд, введен регистр режима работы, блок анализа микрокоманд, два узла задания начальных адресов и шесть коммутаторов причем выходы регистра режима работы соединены соответственно со вторым входом блока индикации неисправностей, с третьим входом блока управления и через первый узел задания начального адреса с первым входом первого коммутатора, второй вход которого соединен с выходом второго узла задания начального адреса, входы которого и четвертый вход блока упраления соединены соответств енно с первым, вторым и третьим вь1ходами блока анализа микрокоманд, четвертый выход которого соединен с первым входом второго регистра микрокоманд, выход которого соединен с первым входо четвертого коммутатора, выходы которого соединены соответственно с первым входом пятого коммутатора, третьим входом блока синхронизации, вторым входом второго регистра при- знака перехода и третьим входом второго регистра адреса микрокоманд, выход которого соединен с первым входо шестого коммутатора, первый и второй выходы которого соединены соответственно со вторым входом пятого коммутатора и входом второй памяти, выход КОТОРОЙ соединен с первым входом седьмого коммутатора, выходы которого соединены соответственно с третьи входом пятого коммутатора и вторым входом второго регистра микрокоманд, третий выход и второй вход седьмого коммутатора соединены соответственно с входом блока анализа микрокоманд и первым выходом восьмого коммутатора, вход которого соединен с третьим

выходом первого арифметического блок второй вход которого соединен с выходом пятого коммутатора, четвертый, пятый и шестой входы которого соединены соответственно с четвертым выходом третьего коммутатора, четвертым выходом второго коммутатора и первым выходом девятого коммутатора, второй выход и входы которого соединены соответственно с червертым входом второго регистра адреса микрокоманд, выходом второго регистра признака перехода и вторым выходом восьмого коммутатора, с третьего по шестой выходы которого соединены со ВТОРЫМИ входами соответственно второго, третьего, четвертого и шестого коммутаторов, а также тем, что блок ана лиза микрокоманд содержит счетчик, схему сравнения, регистр, дешифра;тор, два коммутатора, три элемента ИЛИ, три элемента И, причем вход блока соединен с входом дешифратора и первыми входами первого коммутатора и двух элементов И, первый выход дешифратора соединен со вторым входом первого коммутатора и с первым входом первого элемента ИЛИ, выход которого соединен с первыми входами счетчика и второго элемента ИЛИ, выход которого соединен с третьим входом блока, второй выход дешифратора соединен с третьим входом первого коммутатора и вторым входом первого элемента ИЛИ, выход первого коммутатора через регистр соединен с первым входом схемы сравнения, выход которой соединен со вторым входом второго элемента ИЛИ и первым входом третьего элемента И, выход которого соединен с четвертым выходом блока, третий выход дешифратора соединен с третьими входами первого и второго элементов ИЛИ, первая группа выходов дешифратора через третий элемент ИЛИ соединена со вторыми входами счетчика второго элемента И и вторым выходом блока, первый выход которого соединен с выходом второго элемента И, вторая группа выходов дешифратора через второй коммутатор соединена со вторым входом первого элемента И, выход которого соединен со вторым входбм третьего элемента И выход счетчика соединен со вторым входом схемы сравнения.

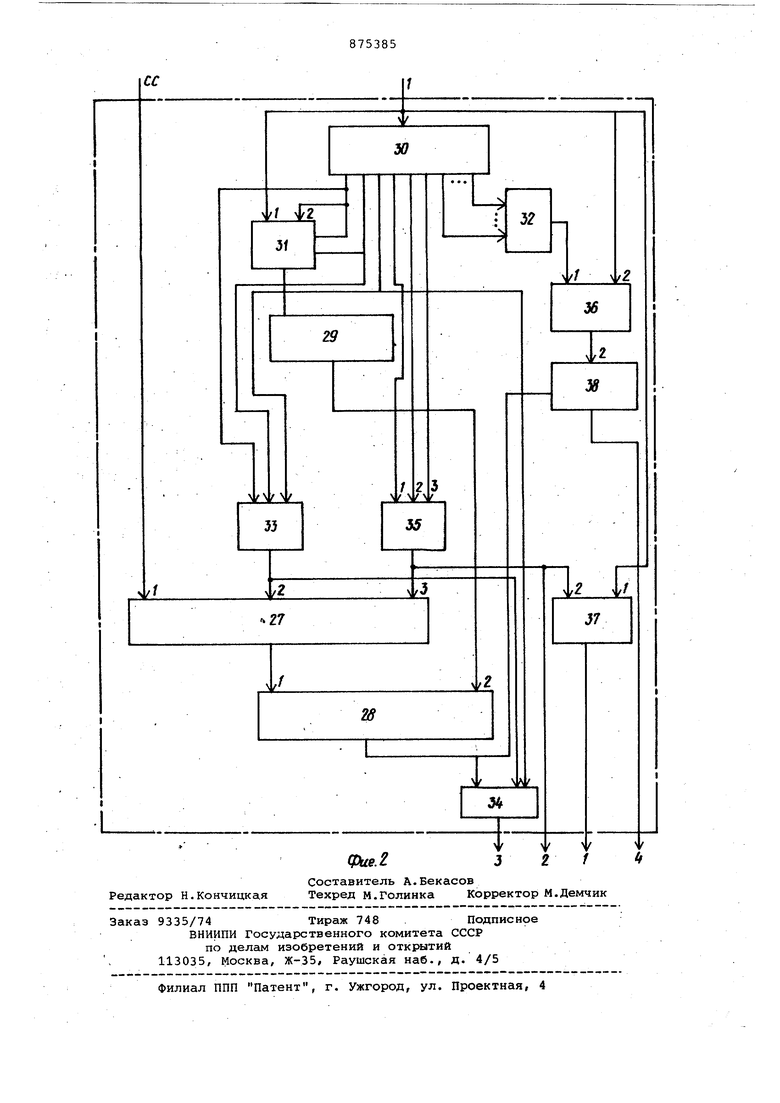

На фиг. 1 представлена блок-схема предлагаемого микропрограммного процессора; на фиг. 2 - пример одной из возможных реализаций блока анализа микрокоманд.

Микропрограммный процессор содержит блок 1 управления, блок 2 индикации неисправности, первый регистр 3 адреса микрокоманды, первый регистр 4 признака перехода, блок 5 синхронизации, первый арифметический блок б, первый регистр 7 микрокоманды, первый :коммутатор 8, первую память

9, вторую память 10, второй арифметический блок 11, второй коммутатор 12, третий коммутатор 13, второй регистр 14 адреса микрокоманды, второй регистр 15 признака перехода, второй регистр 16 микрокоманды, регистр 17 режима работы, блок 18 анализа микрокоманды, первый узел 19 задания начальных адресов, второй узел 20 задания начальных адресов, четвертый - девятый коммутаторы 2126, счетчик 27, схему 28 сравнения, регистр 29, дешифратор 30, первый коммутатор 31 блока анализа микрокоманды, второй Коммутатор 32 блока (анализа микрокоманды, три элемента ИЛИ 33-35, три элемента И 36-38, традиционный микропрограммный процессор 39, микропрограммный процессор 40 для отладки и диагностики. Блок 1 управления предназначен для выработки сигналов управления и синхронизации в режимах работы Микропрограммного процессора Отладка и Диагностика, также он используется для обработки переходов на. подпрограммы и выходов из них. Блок 2 индикации неисправностей предназначен для выдачи оператору и операционной системе сообщения о неисправности микропрограммного процессора. Первый регистр 3 адреса микрокоманды и второй регистр 14 адреса микрокоманды предназначены для выработки и хранения адреса следующей микрокоманды. Первый и второй регистры 4 и 15 признака перехода предназначены для хранения адреса перехода при выполнении условий микрокоманды. Блок 5 синхронизации предназначен для выработки сигналов управления и синхронизации для блоков 10, 11 и 14-16, по программе, записанной во второй памяти 10 в режиме работы процессора Обработка. Первый и второй арифметические блоки 6 и 11 предназначены для выполнения арифметических и логических операций, а также операций сдвига и передачи. Первый и второй регистры 7 и 16 микрокоманд предназначены для хранения микрокоманд. Девять коммутаторов 8, 12, 13 и 21-26 предназначены для коммутации информационных связей под действием управляющих сигналов блока 1 управления. Первая память 9 предназначена для хранения микропрограмм диагностики.неисправностей, отладки микропрограмм, операционной системы и обработки различных микрокоманд. Вторая память 10 предназначена для хранения микропрограмм пользователя и операционной системы. Регистр 17 режима работы предназначен для хранения кода режима работы, заносимого оператором при однопроцессорном исполнении, либо операционной системой при многопроцессорном исполнении. Блок 18 анализа микрокоманды

предназначен для анализа кода микрокоманды, выработки информационных и управляющих сигналов и настройки на определенньлй вид отладки. Первый и второй узлы 19 и 20 задания начальных адресов предназначены для формирования начальных адресов режимов Диагностика и ОтЛадка. Счетчик 27 предназначен для подсчета выполненных микрокоманд. Схема 28 сравнения предназначена для сравнения

0 чисел в счетчике 27 и регистре 29 и выработки сигнала управления при совпадении. Регистр 29 предназначен для хранения количества шагов (микрокоманд) , которые должны быть вы51полнены.

С первого по пятый выходы блока 1 управления соединены с первыми входами соответственно блока 2 индикации неисправности, первого регистра 3

0 адреса микрокоманд, первого регистра 4 признака перехода, блока 5 синхронизации и первого арифметического блока 6. Первый и второй выходы арифметического блока 6 соединены соответственно со вторым входом пер5вого регистра 3 адреса микрокоманд и первым входом блока 1 управления. Второй вход блока 1 управления соединен с первым выходом первого регистра 7 микрокоманд. Второй и тре0тий выходы первого регистра 7 микрокоманд соединены соответственно с третьим входом первого регистра 3 адреса микрокоманд и со вторым входом первого регистра 4. признака пере5хода. Выход первого регистра 4 признака перехода И первого коммутатора 8 соединены соответственно с четвертым и пятым входами первого регистра 3 адреса микрокоманд. Выход

0 первого регистра 3 адреса микрокоманд через первую память 9 соединен с входом первого регистра 7 микрокоманд. Входы второго арифметического блока 11 соединены с первыми выходами второго 12 и третьего 13 коммута5торов. Выход второго арифметического блока 11 соединен с первым входом второго коммутатора 12. Второй и третий выходы второго коммутатора

12соединены соответственно с, пер0вым входом второго регистра 14 адреса микрокоманд и вторым входом блока 5 синхронизации. Выход блока 5 синхронизации соединен с первым входом третьего коммутатора 13. Второй и

5 третий выходы третьего коммутатора

13соединены соответственно со вторьам входом второго регистра 14 адреса микрокоманд и с первым входом второго регистра 15 признака перехода. Выходы регистра 17 режима ра0боты соединены соответственно со вторым входом блока 2 индикации неисправностей, с третьим входом блока 1 управления и через первый узел 19 задания начального адреса с первым

5

входом первого коммутатора 8. Второй вход первого коммутатора 8 соединен с выходом второго узла 20 задания начального адреса. Входы второго узла 20 задания начального адреса и четвертый вхрд блока 1 управления соединены соответственно с первым, вторым и третьим выходами блока 18 анализа микрокоманд. Четвертый выход блока 18 анализа микрокоманд соединен с первым входом второго регистра 16 мик{ оксманд. Выход второго регистра 16 микрокоманд соединен с первым входом четвертого коммутатора 21. Выходы четвертого коммутатора 21 соединены соответственно с первым входом пятого коммутатора 22, третьим входом блока 5 синхронизации вторым входом второго регистра 15 признака перехода и третьим входом второго регистра 14 адреса микрокоманд. Выход второго регистра 14 адреса микрокоманд соединен с первым входом шестого коммутатора 23, первый и второй выходы которого соединены соответственно со вторым входом пятого коммутатора 22 и входом второ памяти 10. Выход второй памяти 10 соединен с первым входом седьмого коммутатора 24. Выходы седьмого коммутатора 24 соединены соответственно с третьим входом пятого коммутатора 22 и вторым входом второго регистра 16 микрокоманд. Третий выход и второй вход седьмого коммутатора 24 соединены соответственно с входом блока 18 анализа микрокоманд и первым выходом восьмого коммутатора 25. Вход восьмого коммутатора 25 соединен с третьим выходом первого арифметического блока 6. Второй вход первого арифм тического блока 6 соединен с выходом пятого коммутатора 22. Четвертый, пятый и шестой входы пятого коммутатора 22 соединены соответственно с четвертым выходом третьего коммутатора 13, четвертым выходом второго коммутатора 12 и первым выходом девятого коммутатора 26. Второй выход и входы девятого коммутатора 26 соединены соответственно с четвертым входом второго регистра 16 адреса микрокоманд, выходом второго регистра 15 признака перехода и вторым выходом восьмого коммутатора 25. С третьего по шестой выходы восьмого коммутатора 25 соединены с вторыми входами соответственно второго 12, третьего 13,«четвертого 21 и шестого 23 коммутаторов. Вход блока 18 анализа микрокоманд соединен с входом дешифратора 30 и первьлми входами первого коммутатора 31 и двух элементов И 36 и 37, Первый выход дешифратора 30 соединен со вторым входом первого коммутатора 31 и первым входом первого элемента ИЛИ 33. Выход первого элемента ИЛИ 33 соединен с первыми

входами счетчика 27 и второго элемента ИЛИ 34. Выход второго элемента ИЛИ 34 соединен с третьим выходом блока 18 ансшиза микрокоманд. Второй выход дешифратора 30 соединен с третьим входом первого коммутатора 31 и вторы входом первого элемента ИЛИ 33. Выход первого коммутатора 31 через регистр 29 соединен с первым входом схемы 28 сравнения. Выход схемы 28 сравнения соединен со вторы входом второго элемента ИЛИ 34 и первым входом третьего элемен.та И 38. Выход третьего элемента И 38 соединён с четвертым выходом блока 18 анализа микрокоманд. Третий выход дешифратора 30 соединен с третьими входами первого 33 и второго 34 элементов ИЛИ. Первая группа выходов Дешифратора 30 через третИ|й элемент ИЛИ 35 соединена, со вторыми входами счетчика 27, вторым входом второго элемента И 37 и вторым выходом блока 18 анализа микрокоманд. Первый выход блока 18 соединен с выходом второго элемента И 37. Вторая группа выходов дешифратора 30 через второй коммутатор 32 соединена со вторым входом первого элемента И 36. Выход первого элемента И 36 соединен со вторым входом третьего элемента И 38. Выход счетчика 27,соединен со вторым входом схемы 28 сравнения.

Устройство работает следующим образом.

Возможны следуквдие режимы работы микропрограммного процессора. Обработка (в этом режиме ведется обработка информации по программам пользователя на традиционном микропрограммном процессоре (блоки 5, 10, 11, 14, 15, 16, 39). Отладка, (в этом режиме ведется отлгщка микропрограмм пользователя, выполняемых на традиционном микропрограммном процессоре 39,- с помощью микропрограммного процессора 40 для отладки и диагностики). Диагностика (в этом режиме ведется диагностика неисправностей традиционного микропрограммного процессора 39 и индикация неисправностей микропрограммного процессора 40 для отладки и диагностики) .

В режиме Обработка работают блоки 5,10-16, 21, 23, 24, 26,традиционного микропрограммного процессора 39. Код режима работы через регистр 17 режима работы подается в блок 1 управления, который настраивает коммутаторы 23, 24, 21, 26, 13, 12 и передает управление блоку 5 синхронизации, который и управляет работой традиционного микропрограммного процессора 39 по микропрограмме, записанной в блоке 10.

В режиме Отладка работают все блоки микропрограммного процессора, кроме блока 2 индикации неисправноети. В данном режиме пользователь, используя блоки 18, 20, 8, 9, 3, У, 4, 1, б, 22, 25 микропрограммного процессора 40 для отладки и диагностики может вьтолнять микропрограммы и программы либо в плановом режиме, либо до заданной, микрокоманды, либо до заданного адреса,и т.д. В то же время использователь может получать необходимую ему информацию о ходе выполнения микропрограмма и программ (например, адрес выполняемой или выполненной микрокоманды, код микрокоманды, или ее символьное представление на языке микропрограммирования содержимое арифметического устройства до и после выполнения микрокоманды или команды и т.д.) . Это достигается за счет блока 18 ангшиза микрокоманды и второго узла 20 задания начального адреса, первый из которых определяет режим выполнения микропрограммы и программы, а второй необходимую для пользования информацию о ходе выполнения микропрограм и программ. Таким образом, пользователь получает эффективное средство для отладки микропрограмм и программ, которое может иметь все необходимые пользователю возможности по. отладке за счет микропрограммирования микропрограммного процессора 40 для отладки и диагностики, т.е. пользователь может записывать свои микропрограммы в блок 9 дополнительно к существующим.

В режиме Диагностика работают все блоки микропрограммного процессора. Код режима работы через регист 17 режима работы подается на блок индикации неисправности, который сообщает пользователю о неисправности процессора И на блок 1 управления После этого начинает работать микропрограммный процессор 40 для отладки и диагностики, который микропрограммно проверяет свою работоспособность и при отсутствии собственных неиспраностей начинает проверять традиционный микропрограммный .процессор 39. Сперва .проверяются отдельные блоки, затем работа двух, трех, четырех, пяти блоков совместно и в конце выполняется тестовая задача на традиционном микропрограммном процессоре 39. При обнаружении неисправности выдается сообщение о неисправности блока на пульт оператора. Если ошибок не найдено, то вьщается сигнал на блок 2 индикации неисправности, который устанавливает его в состояние Исправен. Этодостигается за счет коммутаторов 12, 13 и 2.1-26, которые обеспечивают доступ ко всем элементам традиционного микропрограммного пооиессора 39.

Формула изобретения

1. Микропрограммный процессор, со.держащий блок управления, с первого

по пятый выходы которого соединены с первыми входами соответственно блока индикации неисправности, первого регистра адреса микрокоманд, первого регистра признака перехода, блока синхронизации и первого арифметического блока, первый и второй выходы которого соединены соответственно со вторым входом первого реги.стра адреса микрокоманд и с первым входом блока управления, второй вход

o которого соединен с первым выходом первого регистра микрокоманд, -второй и третий выходы которого соединены соответственно с третьим входом первого регистра адреса микрокоманд и

5 со вторым входом первого регистра признака перехода., выход которого и выход первого коммутатора соединены соответственно с четвертым и пятым входами первого регистра адреса микрокоманд, выход которого че0рез первую память соединен со входом первого регистра микрокоманд, вторую памятьj второй арифметический блок, выходы которого соединены с первыми выходами второго и третьего коммута- .

5 торов, выход второго арифметического блока соединен с первым входом второго коммутатора, второй и третий выходы которого соединены соответственно с первым входом второго ре0гистра адреса микрокоманд и вторым входом блока синхронизации, выход которого соединен с первым входом третьего коммутатора, второй и третий выходы которого соединены соответст5венно со вторым входом второго регистра адреса микрокоманд и с первым входом второго регистра признака перехода, второй регистр микрокоманд, отличающийся тем, что,, с целью повышения коэффициента исполь0зования оборудования, в него введены регистр режима работы, блок анализа микрокоманд, два узла згщания начальных адресов и шесть коммутаторов, причем выходы регистра режима работы

5 соединены соответственно со вторым входом блока индикации неисправности, с третьим входом блока управления и через первый узел задания начального адреса с первым входом первого

0 коммутатора, второй вход которого соединен с выходом второго узла задания начального адреса, входы которюго и четвертый вход блока управления соединены соответственно с первьвм,

5 вторым и третьим выходгими блока анализа микрокоманд, четвертый выход которого соединен с первым входом второго регистра микрокоманд, выход которого соединен с первым входом четвертого коммутатора, выходы кото0рого соединены соответственно с первым входом пятого коммутатора, третьим входом блока синхронизации, вторым входом второго регистра признака перехода и третьим входом второго регистра адреса микрокоманд, вы ход которого соединен с первым входом шестого коммутатора, первый и второй выходы которого соединены со ответственно со вторым входом пятого коммутатора и входом второй памяти, выход которой соединен с первым входом седьмого коммутатора, выходы которого соединены соответственно с третьим входом пятого коммутатора и вторым входом второго регистра микрокоманд, третий выход и второй вход седьмого коммутатора соединены соответственно со входом блока анализа микрокоманд и первым выходом восьмого коммутатора, вход которого соединён с третьим выходом первого арифметического блока, второй вход которого соединен с выходом пятого коммутатора, четвертый, пятый и шес той входы которого соединены соответ ственно с четвертым выходом третьего коммутатора, четвертым выходом второго коммутатора и первым выходом девятого коммутатора, второй выход и входы которого соединены соответственно с четвертым входом второго регистра адреса микрокоманд, выходом второго регистра признака перехода, вторым выходом восьмого коммутатора с третьего по шестой выходы которого соединены со вторыми входами соответственно второго, третьего, чет вертого и шестого коммутаторов. 2. Микропрограммный процессор по П.1, отличающийся тем что блок анализа микрокоманд содержит счетчик, схему сравнения, регистр, дешифратор, два коммутатора, три элемента ИЛИ, три элемента И, причем вход блока соединен со входом дешифратора и первыми входами перво го- коммутатора и двух элементов И, первый тзиход дешифратора соединен со BTopbiM входом первого коммутатора и с первым входом первого элемента ИЛИ, выход которого соединен с первыми входами счетчика и второго элемента ИЛИ, выход которого соединен с третьим входом блока, второй выход дешифратора соединен с третьим входом первого коммутатора и вторым входом первого элемента.ИЛИ, выход первого коммутатора через регистр соединен с первым входом схемы сравнения, выход которой соединен со вторым входом второго элемента ИЛИ и первым входом третьего элемента И, выход которого соединен с четвертым выходом блока, третий выход дешифратора соединен с третьими входами первого и второго элементов ИЛИ, первая группа выходов дешифратора через третий элемент ИЛИ соединена со вторыми входами счетчика, второго элемента И и вторым выходом блока, первый выход которого соединен с выходом второго элемента И, вторая группа выходов дешифратора через; второй коммутатор соединена со вторым входом первого элемента И, выход которого соединен со вторым входом третьего элемента И, выход счетчика соединен со вторым входом схемы сравнения . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 2831302/18-24, кл. G 06 F 15/00, 1979. 2.Авторское свидетельство СССР № 551648, кл. G 06 F 15/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления и отладки микропрограмм процессора | 1984 |

|

SU1168937A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммный процессор | 1980 |

|

SU947868A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для отладки программ | 1986 |

|

SU1410038A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

Авторы

Даты

1981-10-23—Публикация

1980-02-01—Подача