со со

сх о

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля цифровой аппаратуры, состоящей из однотипных каналов, каждый из которых может работать в полном объеме или в части его. Частным случаем является аппаратура, состоящая из -узлов постоянной памяти, построенных на микросхемах 556 серии, в которой часть микросхем не используется совсем либо не используется часть адресов в них.

Цель изобретения - расширение функциональных мозможностей устройства за счет выборочного контроля отдельных каналов многоканальной цифровой аппаратуры на выбранных словах контролирующего тестя.

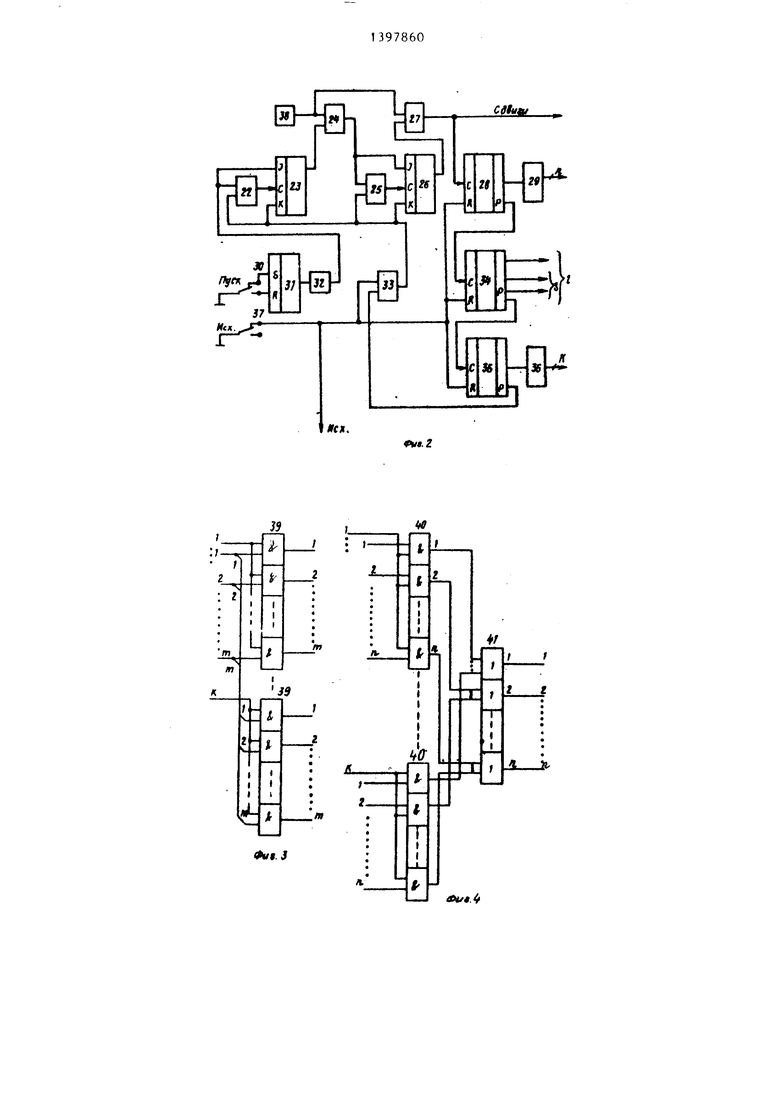

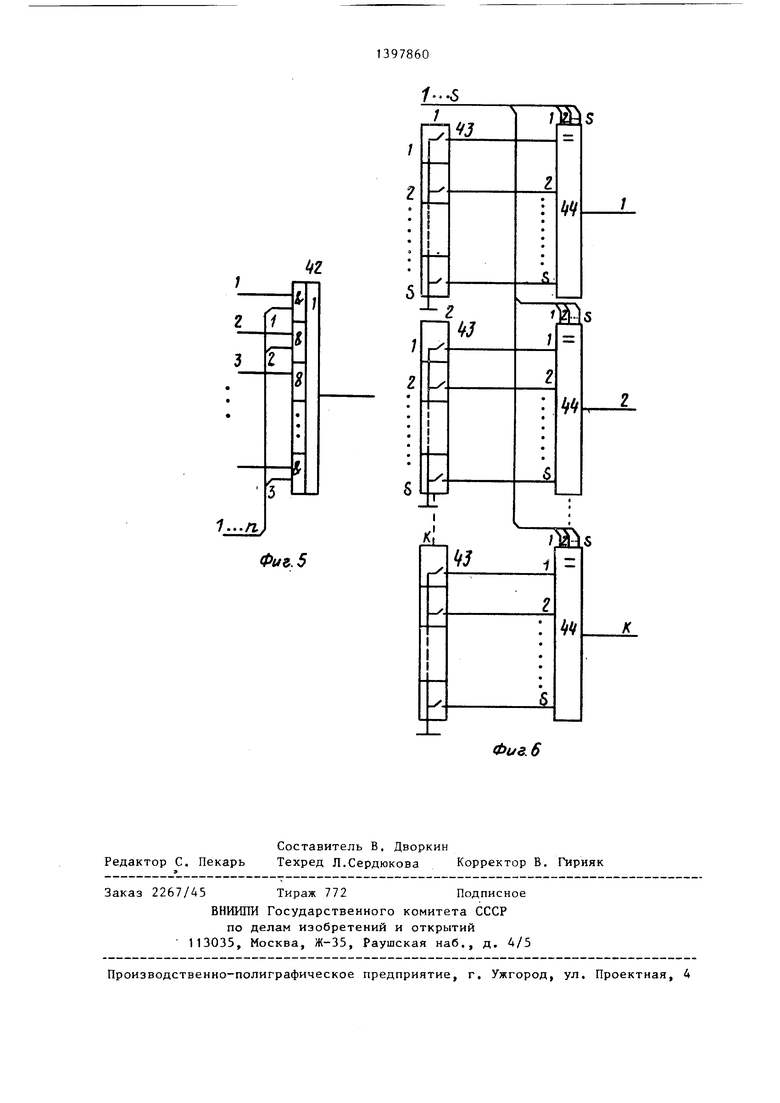

На фиг. 1 представлена схема уст- ройства для контроля многоканальной цифровой аппаратуры; на фиг. 2 - блок управления; на фиг. 3 - мультиплексор; на фиг, 4 - демультиплексор; на фиг. 5 - первый селектор; на фиг.6 - блок задат.чиков зоны с блоками сравнения.

Устройство для контроля многоканальной цифровой аппаратуры 1, разделенной на отдельные каналы 2.1-2.k, содержит блок 3 управления, генератор 4 тестов, мультиплексор 5, демультиплексор 6, первый селектор 7, сигнатурный анализатор 8, индикатор 9, двухвходовый элемент И 10,блок 11 задатчиков начальной зоны считьгоания, первый блок 12 сравнения, блок 13 задатчиков конечной зоны считывания, второй блок 14 сравнения, блок 15 элементов ИЛИ (трехвходовых), блок элементов И 16, второй селектор 17, выключатель 18 полноты контроля,блок 19 выключателей каналов, двухвходовый элемент ИЛИ 20, блок 21 выключателей диапазонов.

вход которого соединен .с выходом двух- входового элемента И Ю, а выход - с входом индикатора 9. Группа первых выходов блока 3 управления соединена

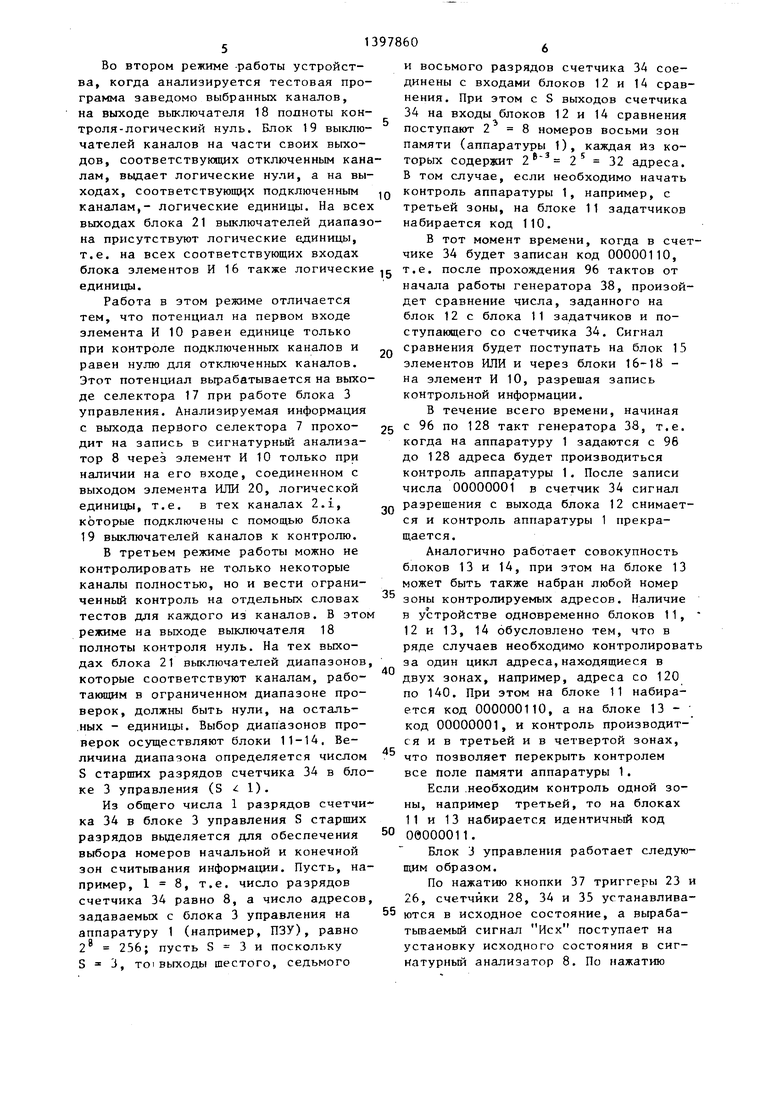

Блок 3 управления (фиг. 2) содержит элемент ИЛИ 22, 1К-триггер 23, элемент И 24, элемент ИЛИ 25, 1К-триг- гер 26, элемент И 27, счетчик 28,

декодер 29, кнопку 30, RS-триггер 31,50 с первыми входами первого 12 и второ- формирователь 32 импульсов, элемент ИЛИ 33, счетчики 34 и 35, декодер 36, кнопку 37, генератор 38 тактов.

го 14 блоков сравнения. Выходы генератора 4 тестов подключены к вторым входам мультиплексора 5, выходы которого соединены с клеммами для подклюГенератор 4 тестов в общем случае ее чения входов проверяемой цифровой представляет собой постоянную память с записанной в ней тестовой программой проверки на m выходов и 1 двоичных разрядов адреса.

аппаратуры 1. Демультиплексор 6 своими вторыми входами соединен с клеммами для подключения выходов проверяемой цифровой аппаратуры 1, а выхода0

0 5

0

Мультиплексор 5 (фиг. 2) состоит из k однотипных т-входовых элементов И 39.

Демультиплексор 6 (фиг. 4) состоит из k однотипных п-входовых элементов И 40 и из п k-входовьгх элементов ИЛИ 41.

Селекторы 7 и 17 (фиг. 5) представляют собой соответственно п и k элементов 2И-ИЛИ 42.

Сигнатурный анализатор 8 - сдвигающий регистр с обратными связями через схему сложения по модулю два.

Блоки 11 и 13 задатчиков зоны (фиг. 6) состоят из k групп элементарных выключателей 43 по S штук в группе.

Блоки 12 и l4 сравнения состоят из k S-разрядных элементов 44 сравнения.

Блоки элементов И 16 и ИЛИ 15 состоят соответственно из k элементарных двухвходовых и трехвходовых элементов И и ИЛИ.

Выключатель 18 полноты контроля представляет побои двоичный тумблер, вьщающий потенциал логического нуля или единицы.

Блок 19 выключателей каналов и блок 21 выключателей диапазонов представляют собой k элементарных двоичных тумблеров.

Блок 3 управления своими первыми выходами соединен с входами генератора 4 тестов, вторыми выходыми - с первыми входами демультиплексора 6, первыми входами мультиплексора 5 и вторыми входами второго селектора 17, третьи выходы блока 3 управления соединены с первыми входами первого селектора 7. Четвертый и пятый выходы- блока 3 управления соединены, соответственно с первым и вторым входами сигнатурного анализатора 8, третий

вход которого соединен .с выходом двух- входового элемента И Ю, а выход - с входом индикатора 9. Группа первых выходов блока 3 управления соединена

чения входов проверяемой цифровой

аппаратуры 1. Демультиплексор 6 своими вторыми входами соединен с клеммами для подключения выходов проверяемой цифровой аппаратуры 1, а выходами - с вторыми входами первого селектора 7. Первый селектор 7 своим выходом подключен к второму входу двух- входового элемента И 10, первый вход которого соединен с выходом двухвходо- вого элемента ИЛИ 20, а выход - с третьим входом сигнатурного анализатора 8. Индикатор 9 подключен к выходам сигнатурного анализатора 8. Вторые входы первого блока 12 сравнения соединены с вьпсодами блока 11 за- датчиков начальной зоны считывания, вторые входы второго блока 14 сравнения - с выходами блока 13 задатчи- ков конечной зоны считывания.

Выходы первого блока 12 сравнения и второго блока 14 сравнения соединены соответственно с первыми и вторыми входами блока 15 элементов ИЛИ, третьи входы которого соедине- ны с выходами блока 21 выключателей диапазонов, выходы блока 15 элементов ИЛИ соединены с первыми входами второго селектора 17. Выход второго селектора 17 подключен к первому входу двухрходового элемента ИЛИ 20, выход выключателя 18 полноты контроля - к второму входу двухвходового элемента ИЛИ 20.

Устройство для контроля многоканальной цифровой аппаратуры работает в зависимости от режимов следующим образом.

В режиме контроля по полной программе выключатель 18 полноты контроля находится во включенном положении, на его выходе логическая единица. Эта единица через элемент ИЛИ 20 откроет элемент И 10. Работа начинается с выработки сигнала установки исходного состояния в блоке 3 управления (фиг. 2) по нажатию кнопки 37. Этот сигнал сбрасывает в исходное состояние элементы блока 3 управления и сигнатурный анализатор 8. По нажатию кнопки 30 с выхода элемента И 27 блока 3 управления начинают вы- даватьс импульсы сдвига, поступающие на вход сигнатурного анализатора 8. В это время с выходов блока 3 управления снимается адрес слова (1), по которому в генераторе 4 тестов записан первый тест. Первый тест с генератора 4 тестов через мультиплексор 5, управляемый информацией с выходов блока управления (k), поступает на входы канала 2.1 проверяемой аппаратуры 1. Информация с выходов канала 2.1

через демультиплексор 6, управляемый той же информацией с выходов блока 3 управления, приходит на входы первого селектора 7. По мере счета импульсов сдвига счетчиком 28 в блоке 3 управления сигналы с декодера 29 (п) поочередно подключают через -селектор 7 выходы демультипле1 сора 6 через открытый элемент И 10 к входу сигнатурного анализатора 8, а информация о первом тесте с выходов канала.2.1 по сдвигам записывается в регистр сигнатурного анализатора 8.После прохождения п импульсов в счетчик 34 в блоке 3 добавляется единица и с выходов блока 3 управления вьщается очередной адрес второго теста.Очередные п импульсов генератора 38 блока 3 управления повторно и поочередно подключают через демультиплексор 6 и селектор 7 информацию с выходов канала 2.1 и т.д., выводится один тест за другим, включая последний, пока импульс переполнения со счетчика 34 в блоке 3 управления не изменит состояния счетчика 35. Начиная с этого момента информация с вторых выходов блока 3 управления подключет через мультиплексор 5 тесты к второму каналу аппаратуры, а через демультиплексор 6 - выходы второго канала к селектору 7 и т.д.

После последовательного подключения всех каналов импульс переполнения со счетчика 35 через элемент ИЛИ 33 прекращает поступление импульсов сдвига с генератора 38 через элемент И 27 и работа устройства прекращается. На индикаторе 9 фиксируется значение сигнатуры, которое следует сравнить с эталонным значением. За один полный цикл работы счетчики 28, 34, 35 блока 3 управления поочередно под- ключают входы каналов 2.1-2.k к генератору 4 тестов, а выходы этих каналов - к селектору 7. В каждом канале

А

реализовано 2 тестов. Например, в том случае, если аппаратура 1 - это

ПЗУ, то задано 2 адресов, а в момент подачи каждого теста с помощью селектора 7 информации считанные числа с выходов каждого из каналов поочередно выводятся на вход сигнатурного анализатора 8 и по импульсам сдвига с блока 3 управления записываются в сдвиговом регистре сигнатурного анализатора 8.

Во втором режиме -работы устройства, когда анализируется тестовая программа заведомо выбранных каналов, на выходе выключателя 18 полноты контроля -логический нуль. Блок 19 выключателей каналов на части своих выходов, соответствуюпшх отключенным канлам, выдает логические нули, а на выходах, соответствующих подключенным каналам,- логические единицы. На все выходах блока 21 выключателей диапазна присутствуют логические единицы, т.е. на всех соответствующих входах блока элементов И 16 также логически единицы.

Работа в этом режиме отличается тем, что потенциал на первом входе элемента И 10 равен единице только при контроле подключенных каналов и равен нулю для отключенных каналов. Этот потенциал вьфабатывается на выходе селектора 17 при работе блока 3 управления. Анализируемая информация с выхода перйого селектора 7 проходит на запись в сигнатурный анализатор 8 через элемент И 10 только при наличии на его входе, соединенном с выходом элемента ИЛИ 20, логической единицы, т.е. в тех каналах 2.1, которые подключены с помощью блока 19 выключателей каналов к контролю.

В третьем режиме работы можно не контролировать не только некоторые каналы полностью, но и вести ограниченный контроль на отдельных словах тестов для каждого из каналов. В это режиме на выходе выключателя 18 полноты контроля нуль. На тех выходах блока 21 выключателей диапазонов которые соответствуют каналам, работающим в ограниченном диапазоне проверок, должны быть нули, на осталь- ,ных - единицы. Выбор диапазонов проверок осуществляют блоки 11-14, Величина диапазона определяется числом S старщих разрядов счетчика 34 в блоке 3 управления (S 1).

Из общего числа 1 разрядов счетчика 34 в блоке 3 управления S старших разрядов вьщеляется для обеспечения выбора номеров начальной и конечной зон считьшания информации. Пусть, например, 1 8, т.е. число разрядов счетчика 34 равно 8, а число адресов задаваемых с блока 3 управления на аппаратуру 1 (например, ПЗУ), равно 2 256; пусть S 3 и поскольку 5 3 то1 выходы шестого, седьмого

5

0

5

5

0

5

0

и восьмого разрядов счетчика 34 соединены с входами блоков 12 и 14 сравнения. При этом с S выходов счетчика 34 на входы блоков 12 и 14 сравнения поступают 2 8 номеров восьми зон памяти (аппаратуры 1), каждая Из которых содержит 2 32 адреса. В том случае, если необходимо начать контроль аппаратуры 1, например, с третьей зоны, на блоке 11 задатчиков набирается код 110.

В тот момент времени, когда в счетчике 34 будет записан код 00000110, т.е. после прохождения 96 тактов от начала работы генератора 38, произойдет сравнение числа, заданного на блок 12 с блока 11 задатчиков и поступающего со счетчика 34. Сигнал сравнения будет поступать на блок 15 элементов ИЛИ и через блоки 16-18 - на элемент И 10, разрешая запись контрольной информации.

В течение всего времени, начиная с 96 по 128 такт генератора 38, т.е. когда на аппаратуру 1 задаются с 96 до 128 адреса будет производиться контроль аппар атуры 1. После записи числа 00000001 в счетчик 34 сигнал Q разрешения с выхода блока 12 снимается и контроль аппаратуры 1 прекращается.

Аналогично работает совокупность блоков 13 и 14, при этом на блоке 13 может быть также набран любой номер зоны контролируемых адресов. Наличие в устройстве одновременно блоков 11, 12 и 13, 14 обусловлено тем, что в ряде случаев необходимо контролировать за один цикл адреса,находящиеся в двух зонах, например, адреса со 120 по 140. При этом на блоке 11 набирается код 000000110, а на блоке 13 - код 00000001, и контроль производится и в третьей и в четвертой зонах, что позволяет перекрыть контролем все поле памяти аппаратуры 1.

Если .необходим контроль одной зоны, например третьей, то на блоках 11 и 13 набирается идентичный код 00000011.

Блок 3 управления работает следующим образом.

По нажатию кнопки 37 триггеры 23 и 26, счетчики 28, 34 и 35 устанавлива- 5 ются в исходное состояние, а вьфаба- тьтаемый сигнал Исх поступает на установку исходного состояния в сигнатурный анализатор 8. По нажатию

кнопки 30 на триггере 31 .формируется положительный перепад, который на формирователе 32 преобразуется в одиночный импульс запуска требуемой длительности, который по своему отрицательному фронту устанавливает единицу на 1К-триггере 23. Элемент ИЛИ 22 обеспечивает срабатывание 1К-триггера 23 по заднему фронту.

Непрерывная импульсная последовательность с генератора 38 проходит через открытый элемент И 24, но пер- зьй импульс этой последовательности может быть искажен по длительности (укорочен), поэтому не может исполь- .зоваться для сдвигов.

, Для его исключения введены элементы ИЛИ 25, 1К-триггер 26 и элемент И 27. Первый импульс последовательности не проходит через элемент И 27, а только взводит 1К-триггер 26 в единичное состояние по заднему фронту, подготавливая элемент И 27 к пропус

3

соединенный своими первыми выхорыми выходами - с первыми входами мультиплексора и демультиплексора, третьими выходами - с первыми входами первого селектора, четвертым и пятым выходами - соответственно с первым и вторым входами сигнатурного анализатора, вторые входы мультиплексора соединены с выходами генератора тестов, выходы мультиплексора - с соответствующими клеммами для подключения входов проверяемой цифровой аппаратуры, вторые входы демультиплексора соединены с соответствующими клеммами для подключения вькодов проверяемой цифровой аппаратуры, выходы демультиплексора - с вторыми входами

первого селектора, отличающееся тем, что, с целью расширения функциональных возможностей устройства, введены блок .задатчиков начальной зоны считьшания и блок задат

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики многоканальной цифровой аппаратуры | 1986 |

|

SU1348758A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Сигнатурный анализатор для контроля цифровых блоков | 1984 |

|

SU1309026A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

Изобретение относится к контрольно-измерительной технике и служит для расширения функциональных возможностей устройства. Устройство содержит блок 3 управления, генератор 4 тестов, мультиплексор 5,демульти-. плексор 6, селектор 7, сигнатурный анализатор 8 блока 12 сравнения, индикатор 9 и блок 21 выключателей диапазонов. Введение, блоков 11 и 13 за- датчиков соответственно начальной и конечной зон считывания, двухвходо- вого элемента И 10, блока 14 сравнения, блока 15 элементов ИЛИ, блока 16 элементов И, селектора 17, двух- входового элемента ИЛИ 20, выключатели 18 полноты контроля и блока 19 выключателей каналов обеспечивает выборочный контроль отдельных каналов многоканальной цифровой аппара- туры ни выбранных словах контролирующего теста. 6 ил. (Л

канию второго неискаженного импульса, 25 чиков конечной зоны считывания, втокоторыи может использоваться для сдвигов в сигнатурном анализаторе 8

Импульсы сдвига поступают на три последовательно соединенных счетчика 28, ЗА, 35. Счетчик 28 и декодер 29 на п выходов обеспечивают поочередное подключение выводов каждого из k саналов через первый селектор 7 и элемент И 10 к анализатору 8. Счетчик 34 на 1 двоичных разрядов является счетчиком адреса для выбора очередного из 2 тестов с генератора 4 тестов Старшие разряды счетчика 34, обозначенные как S, используются для выбора анализируемой зоны в блоках 12 и 14 сравнения.

Счетчик 35 с декодером 36 предна- знАчены для подключения к анализатору 8 через мультиплексор 5 и демульти- плексор 6 выводов очередного из k каналов. Импульс переполнения последнего счетчика 35 через элемент ИЛИ 33 сбрасывает триггеры 23 и 26 в нулевое состояние и прерывает пачку импульсов сдвига. Элементы 22 и 25 обеспечивают срабатывание триггеров 23 и 26 по заднему фронту импульса переполнения .

Формула изобретения

Устройство для контроля многоканальной цифровой аппаратуры, содержащее первый блок сравнения, блок выключателей диапазонов, блок управле0

5

0

5

0

5

рой блок сравнения, блок выключателей каналов, блок элементов ИЛИ,блок элементов И, второй селектор, выключатель полноты контроля, двухвходовый элемент И, двухвходовый элемент ИЛИ, причем первые входы первого и второго блоков сравнения соединены с соответствующими первыми выходами блока управления, вторые входы блоков сравнения - соответственно с выходами блока задатчиков наклонной зоны считывания и блока задатчиков конечной зоны считывания, выходы первого и второго блоков сравнения соед унены соответственно с первыми и вторыми входами блока элементов ИЛИ, третьи входы которого соединены с выходами блока выключателей диапазонов, выходы - с первыми входами блока элементов И, вторые входы блока элементов И соединены с выходами блока выключателей каналов, выходы - с первыми входами второго се-п лектора, вторые входы которого соединены с вторыми выходами блока управления, выход - с первым входом двухвходового элемента ИЛИ, второй вход которого соединен с выходом выключателя полноты контроля, выход - с первым входом двухвходового элемента И, второй вход двухвходового элемента И соединен с выходом первого селектора, выход - с третьим входом сигнатурного анализатора, выход которого соединен с входом индикатора.

ДГСХ.

Фиг. 5

Фиг. 6

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и диагностики многоканальной цифровой аппаратуры | 1986 |

|

SU1348758A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-05-23—Публикация

1986-10-14—Подача