(54) : МУЛЬТИПЛЕКСНЫЙ КАНАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Мультиплексный канал | 1980 |

|

SU879580A1 |

| Устройство управления каналами | 1973 |

|

SU518769A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Устройство для управления каналами связи вычислительной системы | 1975 |

|

SU525095A1 |

1

Денное изобретение относится к вычислительной технике, в частности к органнаащ1я структур мультиплексных каналов микрО1фограммных вычислительных машин.

Известны мультиплексные каналы, соде1 жавдие блок управления квкала, входной я выходной информационные регистры, вход- иой и выходной регистры управпения интвр рейсом, блок, сборки регистров и блок ксйгролй / абсты канала.

Нелзъ изобретения - повышение быстро- fle cTBHS устройства.

Предлагаемый мультиплексный канал до гюлки-тельно содержит блок хоммугадии н блок jCTaKJBOKs первый и второй входы ко-г jioporo соединены соответственно с выходом п.1ска /лра;злемия и выходного регистра уп4 ре злэнип ЩтерфейсоМб один из входов которого пода.яючен к выходу блока установок; T iei:-Ky. его вход соединен с соответсту syscsiHM управляющим входом устройства. Четвеггый вход блока установок и первый Еход Snotfl коммутации подключены ко входу улраьг;«; ;:щей информации, второй и трютий входы бжжа коммутации соединены с cooiv,

ветствующими выходами «блока управления канала и выходом входного {информационного регистра соответственно, четвертый и пятый входы блсжа коммутации подключены); к адресному и j информационному входа устройства соответственно, первый и вторсЦ выходы блока коммутации соединены сО вхбдом выходного информационного регист- ра и с информацноннь5М выходом устройсту ва соответственно.

Это позволяет повывить быстродействие канала благодаря использованию отдельног(| информационного потока для передачи данн1 1Х ускорению коммутации информационных ший и возможности частичного совмещения боты других устройств вычислительной мэ-{ шины во время выполнения циклов переда чн данных через мультиплексный канал.

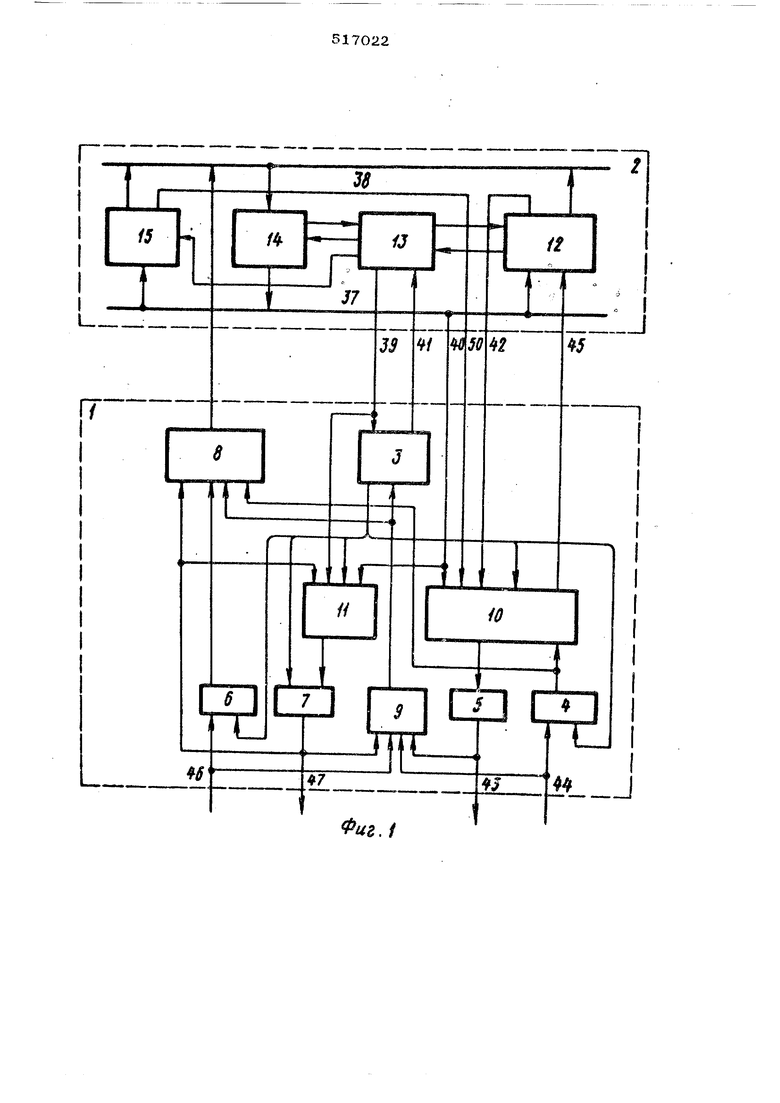

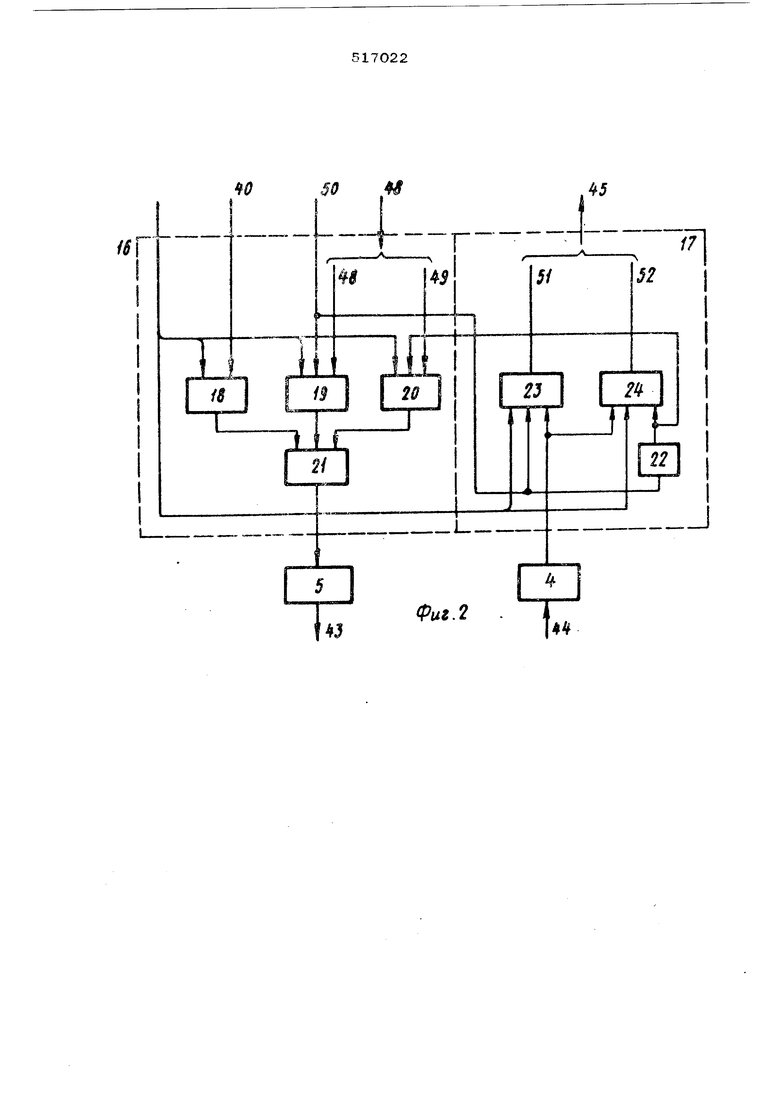

На фиг. 3. представлена струтстурная схема мультг;;лексного канала; на фиг. 2 схема бяока коммутации; на фиг. 3 - схеки блока установок.

; Устройство состоит из муяьтиплеконого канала 1 и процессора 2. Мультиплексный канал содержит блок управления 3, входной информационный регистр 4, выходной информационный регистр 5,вхоаной регистр управления интерфейсом 6,выхос ной регистр управления интерфейсом 7, блок сборки регистров 8, блок KOHt роля работы канала 9, блок коммутации 10 блок установок 11. В состав процессора входят оперативная память 12, блок микропрограммного управления 13, арифметическо логическое уст ройство 14, блок регистров 15. Блок коммутации содержит схему коммутации выходных информационных шин про цессора 16, . схему коммутации входных информационных шин 17. В схему коммутации 16 {фиг. 2) входят схемы И 18-20, схема ИЛИ 21. Схема коммутации 17 состоит из схемы НЕ 22 и схем И 23, 24. Схема блока установок (фиг. 3) состоит из выходного регистра управления интерфейсом 7 и блока установок 11. Первая из ниа содержит триггер приема передачи 25, триггер останова ввода-вывода 26, триггер зацепления по данным 27, схему ИЛИ 28, схему ИЛИ 29. В состав вто рой входят схема установки триггера ЗО, схема установки триггера 31, схема установки триггера 32j состояшая из схем И 33 и 34 и схемы НЕ 35, а также схема НЕ 36. Мультиплексный канал 1 предназначен для подключения к процессору 2 микропрограммной вычислительной машины сравнительно медленнодействующих устройств вво .да-вывода и управления передачей информации между ними и процессором. Работает мультиплексный канал следующим образом. Операция ввода-вывода в канале начина ется по определенной команде, которая задает адрес канала и устройства ввода-вывода и при помощи управляющих слов указывает код команды, начальный адрес данных, количество передаваемых по этой команде байтов данных, управляющие приэ наки и ключ защиты памяти. Канал формирует управл5пощее слово для каждой операции ввода-вывода и хра нйт его в специальной области оперативной памяти 12, называемой мультиплексной памятью. Управляющая информация передается мажду процессором 2 и мультиплексным каналом 1 через арифметическовлогическое устройство 14, его выходные информ ционные шины 37, блок коммутации Ю, а также через блок сборки регистров 8 и входвз ю информационные шинь 38 устройс ва 14. При этом указанный в микрокомане признак регистра, в который необходимо принять или из которого необходимо передать информацию, передается из блока микропрограммного управления 13 через выходные управляющие шины 39 процессе ра в блок управления канала 3, которь1Й подключает :;:ааанный в микрокоманде регистр к блоку сборки регистров 8 или ЕЫкодной информационный регистр 5 канала к выходным информационным шинам 40 арифметическо логического устройства 14 через блок коммутации 10. Получив необходимую управляющую информацию, канал 1 выполняет начальную выборку а,аресуемого устройства ввода-вьгвода. При этом передачей адреса устройства ввода-вывода, кода команды и байта начального состояния адресуемого ва управляют входной и выходной регистры управления интерфейсом 6 и 7 соотве- -- Ственно. Установка соответствующих триггеров в этих регистрах производится микропрограммно или аппаратными средствами. После окончания -начальной выборки устройства вво- да-вывоаа канал сообщает процессору о результатах попытки начать ввод-вывод (путем установки соответствующего кода результата) и, как правило, освобождает процессор для выполнения других команд, в том числе и команд обращения к другим устройствам. Дальнейшим выполнением опе раций ввода-вь вода управляет мультиплексный канал 1. При готовности устройства ввода-вывода принять или передать первый (очередной) байт данных мультиплексный канал передает в процессор запрос на обслуживание, который через соответствующую вход-, ную управляющую шину 41 процессора по- ступает в блок микропрограммного управления 13. По этому запросу приостанавливается выполнение текущей микропрограммы после завершения очередного цикла обращения к оперативной памяти, если процессор не выполняет более приоритетных , микропрограмм,и выполняется определенная микропрограмма, которая; -запоминает состояние адресных и информационных регистров процессора; -считывает управляющее слово из соответствующего подканала мультиплексной памяти; -выполняет циклы передачи информации между оперативной памятью процессора и устройством ввода-вывода; -модифицирует адрес данных и счетчик байтов на количество переданных байтов; -запоминает модифицированное управлшощее слово устройства в своем под канале мультиплексной памяти; -восстанавливает состояние регистров процессора и продолжает выполнение приостановленной микропрограммы. Цикл передачи информации повторяется столько раз, сколько байтов данных передается между соответствующим усоройство ввода-вывода и оперативной памятью за од но подключение его к каналу. При i выполнении команды записи инфар передается из оперативной памяти 12 процессора через выходные информацио ные шины 42 оперативной памяти, блок ко мутации 1О, выходной информационный ре- гистр 5 канала и выходные информационны шины 43 канала в устройство ввода-вывода. При выполнении команды считывания и формация передается из устройства вводавывода через входные информационные шины 44 канала, входнбй информационный ре гистр 4, блок коммутации 1О и входные информационные шины 45 оперативной пам ти - в оперативную память 12 процессора При этом передачей информации через ин.формационные шины интерфейса 43 и 44 упраЕляют вхоакой и выхоцной регистры отравления интерфейсом 6 и 7, которые связаны со входными и выходнь ми управля ющими шинами калала 46 и 47 соответственно. За правильнос-тЕ ю информации, передаваемой по информационным шинам канала, а за соблюдением требований к длительности последовательностей сигналов, передаваемых межау каналом 1 и устройствами вБода-выво.ца, следит блок контроля работы канала 9, который в случае об«наружения на информационных шинах четной , информации или нарушений в последователь- -КОСТЯХ управляющих сигналов интерфейса устанавливает запрос на обслуживание, который через блок управления канала 3 и входную управляющую шину 41 процессора посггулаат в блок микропрограмтущого упр влс--:ч 13 (зьпюлнение операции вводайывода :;рк этОИ прекращается). По этому после завершения очередного цикла обращения к оперативной памяти выполняет-: г спэцкальная михропрограмма, которой аналкзкрует состояние канала и передает и гроцессор информацию о причине прекрн-.аеаия операции ввода-вывода. : В Оц--;;;й к выход -1ые информационные - JHHb: стрративной памяти 42 и 45 в рассматри-заемой вычислительной машине яв- .лшотсг двухбайтовыми. Ланпые меж,ау каналом 1 и устройствами ввода-вывода всегда передаются по одному байту. Поэтому в каждом щш/1ё передачи данных проиэврдится коммутация четного (или нечетного) байта информационных шин или оператив- ; ной памяти и входного или выходного информационных регистров каналов в блоке коммутации 10. Информационные яшны коммутируются в зависимости от четности адреса оперативной памяти по сигналам, вырабатываемым микропрограммно в блоке управления 3 канала. Для ускорения анализа способа коммутации информационных ший в рассматриваемом канале 1 i нспользоввн ; комбинированный (микропрограммно-ahfRaратный) метод управления коммутацией информационных шин при помощи блока I коммутации 10, пример реализации котороч iго приведен на фиг. 2. Этот блок содерйси i CXOMbJ коммутации выходных и ВХОДНЬ Х ИН i формационных шин процессора 16 и 17 со ответственно. Схема коммутаци выходных информации онных ШИН 16 процессора, представляющая i собой последовательно соединенные схемы IM и схему ИЛИ 21, подключает I выходной информационный регистр 5 канаI ла к выходнь м информационным шинам 4О ; арифметическо-логического устройства ; (при передаче управляющей информации) , или к шинам четного или нечетного байта |48, 49 соответственко выход ш1х информа- Щионных шин процессора и зависимости от состояния мла,ашвго разряда адреса опера- тивной памяти, поступающего от адресного регистра блока регистров 15 процессора I по шине 5О четности а.ареса оперативi ной памяти (при передаче данных). Схема 17 коммутации входных информа; ционных ШИН 45 оперативной памяти, состоящая из схем И 23,,24, подключает : входной информационный регистр 4 канал к шинам четного или нечетного байга 51, 52 соответственно входных информа: ционных щин 45 оперативной г амяти Процессора в зависимости от состояния младего разряда адреса оперативной памяти 50 .2) Сигнал на передачу байта данных межоу оперативной памятью и каналом вырабаты- вается в блоке управления канала 3 М1Ж- ропрограммно по сигналам, поступающим из блока микропрограммного управления ;13 при Сггыаании соответствующих ;микрокод анд. Аппаратный анализ четности i адреса оперйтивной памяти позволяет рить выбор способа коммутации информа- ционных шик, так как микропрограммное формирование сигналов управления переда;чей данных между оперативной памятью 12 и каналом 1 совмещается со схемным анализом четясхгги адреса оперативной памяти. Кроме того, использование отдельного информационного потока для передачи байтов да1Шых между мультиплекс ным каналом 1 и оперативной памятью 12 позволяет использовать арифметическологическое устройство для модификации а.ареса данных и счетчика байтов одновременн с передачей информации и, следовательно, повысить быстродействие канала. Выполнение циклов передачи данных ускоряется также благодаря комбинированному (микропрограммнО впаратному) управлению передачей данных межау каналом 1 1И устройством ввода-вывода блоком устано вок 11, пример реализации которого приведен на фиг1 3. Этот блок содержит схе -му 30 установки триггера 25 приема передачи регистра 7, схему 31 установки триггера 2 6 останова ввода-вывода регист ра 7 и схему 32 установки триггера зацепления 45 по данным регистра 7. В каждом цикле передачи данных при готовности канала принять или передать очередной байт данных (в ответ на требова нив устройства ввода-вывода) триггер 25 приема-передачи в выходном регистре управления интерфейсом 7 устанавливается в единичное ссх гоянне через схему установки 30 и схему ИЛИ 28 при помощи блока управления канала 3, в .зависимости от состояния счетчика байтов для данной операции. Триггер приема-передачи 25 устанавливается в единичное состояние в том случае, если счетчик байтов не равен нулю (т. е если нет сигнала на шине бЗ нулевого счетчика байтов и на выходе схемы НЕ 36 установлен разрешающий для установки триггер 25 сигнал Счетчик не равен ). После ответа устройства ввода-выв да об окончании приема-передачи байта данных триггер 25 перевоДитчзя в нулевое состояние (цепи установки триггеров регистра 7 в нулевое состояние Hai фиг, 3 не показаны). Циклы передачи данных повторяютсядо тех пор, пока устройство ввода-вывода не закончит выполнение операции ввода-вывода или пока содержимое счетчика байтов длятекушей операции ввода-вывода не станет равйным нулю. В последнем случае в ответ на готовность устройства вводавывода принять или передать очередной байт данных канал 1 устанавливает в единичное состояние триггер останова вводавывода 26 через схему установки 31 и схему ИЛИ 29f если не установлен в ед ничное состояние триггер зацепления по , данным 27« которЕ й на время выполнения циклов передачи данных отражает состйяни Щ)51знака ошцепления по данным, указанного для ценной операции ввода-вывода в соответтвующем подканале мультиплексной памяти. 27 устанавливается в единичное состояние (при считывании управляющего лова, содержащего этот признакj и загруэв его в регистры процессора) при помоши блока управления канала 3 и схемы 32 установки, cocrosuaefi из схем И 33,. 34 и схемы НЕ 35. Триггер 27 устанав ливаетсй в едяничное состояние через схе- му И 33 по единичному состоянию признака зацепления по данным в управляющем слове устройства, поступающем в канал по одной из Ьыходных информационных шин 4О арифметическо-логического устройства, ИЛИ в нулевое состояние через схему И 34, если этот признак не установлен. По единичному состоянию триггера оста нова ввода-вывода 26 устройство вводавывода прекращает формирование запросов на передачу данных и передает в канал сп1эциальный байт информации, отражаю щий состояние устройства Б момент останова ввода-вывода. Триггер 26 переводится в нулевое состояние после того, как устройство ввода-вывода сообщает каналу о выполие- НИИ команды Остановить операцию ввода- вывода. I Для установки ;;., триггеров 25 и 26 в единичное состояние используются специ альные разряды микрокомакоэ что позволяет параллельно с управлением передаче данных выполнить другие (фикции при по мощи арифметическо-логического устройства. Формула изобретения Мультиплексный канал, содержащий блок управления канала, входной и выходной информационные регистры, входной и выхоцной регистры управления интерфейсом блж сборки регистров, входы которого подключены соответственно к выходам вход ного и выходного регистров управления интерфейсом, к выходу входного информациоН ного регистра и к выходу блока контроля работы канала, подключенному ко входу блока управления канала, выход блока сборки регистров соединен с соответствующим выходом канала, входы блока контроля работы канала соединень соответственно с выходами выхоанся о регистра управления интерфейсом, выходного информационного регистра, пцакдюченными к соответствующим выходам канала, и со входами вхоц- ного регистра упрвв:пвния интерфейсом,

входного информационного регистра, поцключеннымк к соответствующим входам канала, управляющие входы вхоаного регистра управления интерфейсом и входного информационного регистра подключены к соответствукжцим выходам блока управле- ния канала, соединенного с управ пяюшнми зх(Шами и выходами канала, отличающийся теМ; что, с целью по вьпиення быстродействия, в него введекь,., блок коммутации и блок установок, первый и второй входш которого соедянень соот ветстэенно с выхоцами блока управления канала и выходного регистра управления интерфейсом, один из ахоаов ; которого подключен к выходу блсжа установок, трв«

10

1тий вход которогХ) сседкнан с соогветстйуj юшим управляющим входо - устроГ.ства, чет зертый вход блока установок м первый вхоц блоке коммутации подключены ко входу уПравляюшей информации9 второй и третий входы блока коммутации соединены с соот ветствуюшими выходами блока управпения канала и выходом входного информащюнного регистра соотаетственно, четвертый и входы блока коммутации гюдключены к адресному к имформацяонному входам уст ;ройства соотЕвтственно, первый и второй |выхо.аь блока коммутации соединены со входом выхоцного информационного регнст- jpa и с информационным выходом устройс- |ва соответственно.

г;

15

/4

1

J7

/J

fE

:I

42

4j

Ш

f

//

10

UJ

UJ

«

3

/

7

i4I

J

«2. /

0 so

d

IS

25

f

I

Г

L.

Фиг.З

Авторы

Даты

1976-06-05—Публикация

1973-07-18—Подача