Изобретение относится к автоматике и вычислительной технике и может быть использовано для обнаруже ния отказов типа постоянный нуль и постоянная единица дублируемых систем дискретного действия с одновременным сохранением исправной выходной информации. Известно дублированное устройство содержащее два идентичных логических блока, входы которых подключены к входным шинам, две схемы сравнения и схему ИЛИ (ll. Однако это устройство неспособно обнаружить и отключить от выхода устройства отказавшую дублируемую систему. Наиболее близким техническим реш нием к изобретению является дублированное устройство, содержащее два дублируемых блока, выходы которых подключены ко входам схемы сравнения и к первым входам схемы совпаде ния соответственно, а выходы послед них соединены со входами схем ИЛИ 12 Недостатком известного устройств является то, что оно не позволяет обнаружить отказавший блок и под ключить к выходу устройства выход исправного дублируемого блока и, те самым, ошибочная информация попадает в последующие устройства. Цель изобретения -. повышение надежности устройства. Эта цель достигается тем, что в дублированноеустройство, содержащее злемент ИЛИ, два дублируемых блока, подключенных выходами к первым входам первого блока сравнения и к первым входам соответствующих вторых блоков сравнения, введенычетыре элемента И, три блока задержки, два триггера и два блока памяти, соединённых входами с выходами соответствующих дублируемых блоков, а выходами - со вторыми входами соответствующих вторых блоков сравнения, подключенных выходами к первым входам соответственно первого и второго элементов И, соединенных вторыми входами с ВЫХОДОМ первого блока сравнения и со входом первого элемента задержки, подсоединенного выходом чрт рез первый триггер к третьим входам первого и второго элементов И, подключенных выходами через соответственно второй и третий элемент задержки ко входам второго триггера,выхсды которого подсоединены к первым входам третьего ичетвертого элеменTOE И, соединенных вторыми входами о выходами соответствующих блоков памяти, а выходами - со входами элемента ИЛИ.

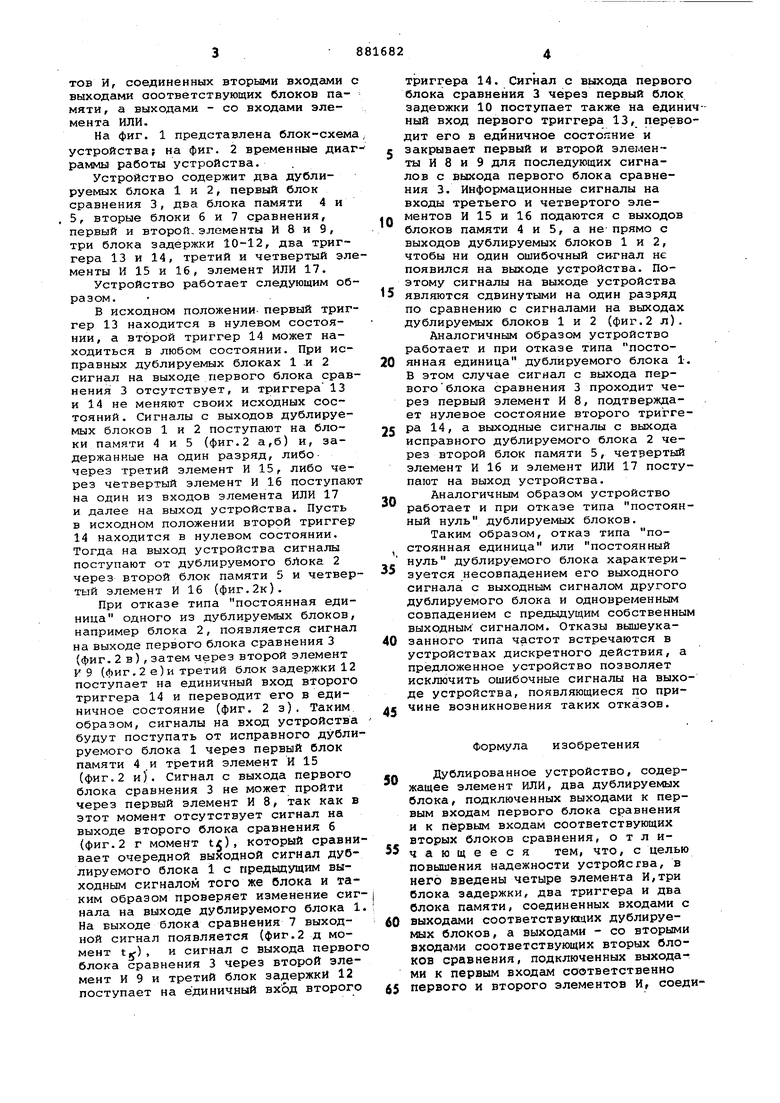

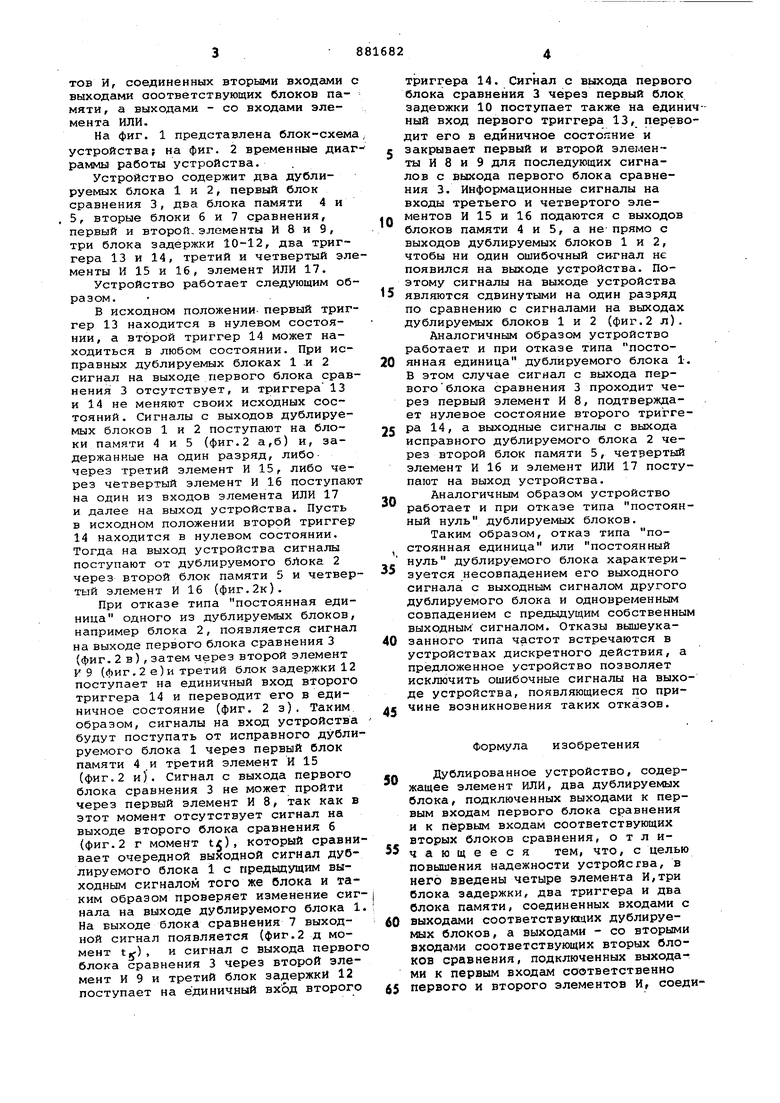

На фиг. 1 представлена блок-схема устройства} на фиг. 2 временные диаграммы работы устройства.

Устройство содержит два дублируемых блока 1 и 2, первый блок сравнения 3, два блока памяти 4 и 5, вторые блоки 6 и 7 сравнения, первый и второй, элементы И 8 и 9, три блока задержки 10-12, два триггера 13 и 14, третий и четвертый элементы И 15 и 16, элемент ИЛИ 17.

Устройство работает следующим обра э ом.

В исходном положении, первый триггер 13 находится в нулевом состоянии, а второй триггер 14 может находиться в любом состоянии. При исправных дублируемых блоках 1 .и 2 сигнал на выходе первого блока сравнения 3 отсутствует, и триггера 13 и 14 не меняют своих исходных состояний. Сигналы с выходов дублируемых блоков 1 и 2 поступают на блоки памяти 4 и 5 (фиг.2 а,б) и, задержанные на один разряд, либочерез третий элемент И 15, либо через четвертый элемент И 16 поступают на один из входов элемента ИЛИ 17 и далее на выход устройства. Пусть в исходном положении второй триггер 14 находится в нулевом состоянии. Тогда на выход устройства сигналы поступают от дублируемого бЛока 2 через второй блок памяти 5 и четвертый элемент И 16 (фиг.2к).

При отказе типа постоянная единица одного из дублируемых блоков, например блока 2, появляется сигнал на выходе первого блока сравнения 3 (фиг. 2 в), затем через второй элемент И 9 (фиг. 2 е)и третий блок задержки 12 поступает на единичный вход второго триггера 14 и переводит его в единичное состояние (фиг. 2 з). Таким образом, сигналы на вход устройства будут поступать от исправного дублируемого блока 1 через первый блок памяти 4 и третий элемент И 15 (фиг.2 и). Сигнал с выхода первого блока сравнения 3 не может пройти через первый элемент И 8, так как в этот момент отсутствует сигнал на выходе второго блока сравнения 6 (фиг.2 г момент t), который сравнивает очередной выходной сигнал дублируемого блока 1 с предьщущим выходным сигналом того же блока и таким образом проверяет изменение сигнала на выходе дублируемого блока 1 На выходе блока сравнения 7 выходной сигнал появляется (фиг.2 д момент tjf) , и сигнал с выхода первого блока сравнения 3 через второй элемент И 9 и третий блок задержки 12 поступает на единичный вход второго

триггера 14. Сигнал с выхода первог блока сравнения 3 через первый блок задевжки 10 поступает также на единный вход первого триггера 13, перевдит его в единичное состояние и закрывает первый и второй элементы И 8 и 9 для последующих сигналов с выхода первого блока сравнения 3. Информационные сигналы на входы третьего и четвертого элементов и 15 и 16 подаются с выходов блоков памяти 4 и 5, а не прямо с выходов дублируемых блоков 1 и 2, чтобы ни один ошибочный сигнал не появился на выходе устройства. Поэтому сигналы на выходе устройства являются сдвинутьоми на один разряд по сравнению с сигналами на выходах дублируемых блоков 1 и 2 (фиг.2 л).

Аналогичным образом устройство работает и при отказе типа постоянная единица дублируемого блока 1 В этом случае сигнал с выхода первого блока сравнения 3 проходит через первый элемент И 8, подтверждает нулевое состояние второго триггера 14, а выходные сигналы с выхода исправного дублируемого блока 2 через второй блок памяти 5, четвертый элемент И 16 и элемент ИЛИ 17 поступают на выход устройства.

Аналогичным образом устройство работает и при отказе типа постоянный нуль дублируемых блоков.

Таким образом, отказ типа постоянная единица или постоянный нуль дублируемого блока характеризуется несовпадением его выходного сигнала с выходным сигналом другого дублируемого блока и одновременным совпадением с предыдущим собственным выходным сигналом. Отказы вышеуказанного типа частот встречаются в устройствах дискретного действия, а предложенное устройство позволяет исключить ошибочные сигналы на выходе устройства, появляющиеся по причине возникновения таких отказов.

Формула изобретения

Дублированное устройство, содержащее элемент ИЛИ, два дублируемых блока, подключенных выходами к первым входам первого блока сравнения и к первым входам соответствующих вторых блоков сравнения, отличающееся тем, что, с целью повышения надежности устройства, в него введены четыре элемента И,три блока задержки, два триггера и два блока памяти, соединенных входами с выходами соответствугацих дублируемых блоков, а выходами - со вторыми входами соответствующих вторых блоков сравнения, подключенных выходами к первым входам соответственно первого и второго элементов Иг соедненных вторыми входами с выходом первого блока сравнения и со входом первого элемента задержки, подключенного выходом через первый триггер к третьим входам первого и второго элементов И, подключенных выходами через соответственно второй и третий элемент задержки ко входам второго триггера, выходы которого подсоединены к первым входам третьего и четвертого элементов И, соединенных

вторыми входами с выходами соответствующих блоков памяти, а выходами со входами элемента ИЛИ.

Источники информации, принятые вб внимание при экспертизе

1.Авторское свидетельство СССР 424120, кл. G 05 В 23/02, 1972.

2.Авторское свидетельство СССР 283688, кл. G 06 F 11/00, 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Устройство для управления реконфигурацией резервированной вычислительной систем | 1989 |

|

SU1718398A1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| Устройство для управления переключением резервных блоков | 1982 |

|

SU1091168A1 |

| Устройство контроля и регистрации служебных признаков в системе телемеханики | 1984 |

|

SU1275513A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И РЕЗЕРВИРОВАНИЯ ИНФОРМАЦИОННОЙ СИСТЕМЫ | 2010 |

|

RU2453079C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для контроля и сигнализации высоты полета самолета | 1990 |

|

SU1817125A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

Авторы

Даты

1981-11-15—Публикация

1980-01-14—Подача