(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕУСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Перепрограммируемое постоянное запоминающее устройство | 1980 |

|

SU900316A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 1984 |

|

SU1841014A1 |

| Устройство для группового управления лифтами | 1982 |

|

SU1089024A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU959168A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096694A1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1994 |

|

RU2116674C1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

1

Изобретение относится к вычислительной технике и предназначено для хранения программ.

Известно постоянное запоминающее устройство (ПЗУ), в котором информация представлена в двоичном коде, содержащее схему адресации, информационную шину и транзисторную матрицу , ксокдый столбец которой содержит шину считывания и шину констант, а каждая строка - адресную шину. В зависимости от наличия или отсутствия соединения транзистора с шиной константы определяется значение записанной в данную ячейку информации 12.

Наиболее близким техническим решением к предлагаемому является ПЗУ, содержсвдее матричный накопитель, первый вход каждого запоминающего элемента которого подключен к соответствующему выходу первого адресного дешифратора,.выход каждого запоминающего элемента соединен с шиной считывания, и второй адресный дешифратор (генератор констант). Значение хранимой в каждом запоминающем элементе (ячейке) ПЗУ информации определяется наличием или отсутствием соединения второго входа этой ячейки с шиной константы (землей). ТаКИМ образом, данное ПЗУ может хранить по одному биту в ячейке Г2,

Недостатком данных ПЗУ является малая информационная емкость устройства.

Цель изобретения - повышение информационной емкости устройства.

Поставленная цель достигается тем, что в ПЗУ введен формирователь

10 двоичных последовательных кодов, входы которого соединены с выходами генератора констант, а каждый из выходов - со. вторым входом соответствующего запоминающего элемента. Кро15ме того, формирователь двоичных последовательностей кодов содержит группу элементов ИЛИ, причем первые входы элементов ИЛИ групп и вторые входы элементов ИЛИ первой группы

20 подключены ко входам формирователя двоичных последовательных кодов, а вторые входы элементов ИЛИ второй группы - к соответствующим выходгил элементов ИЛИ первой группы, выходы

25 элементов ИЛИ групп подключены к выходсш формирователя двоичных последовательных кодов.

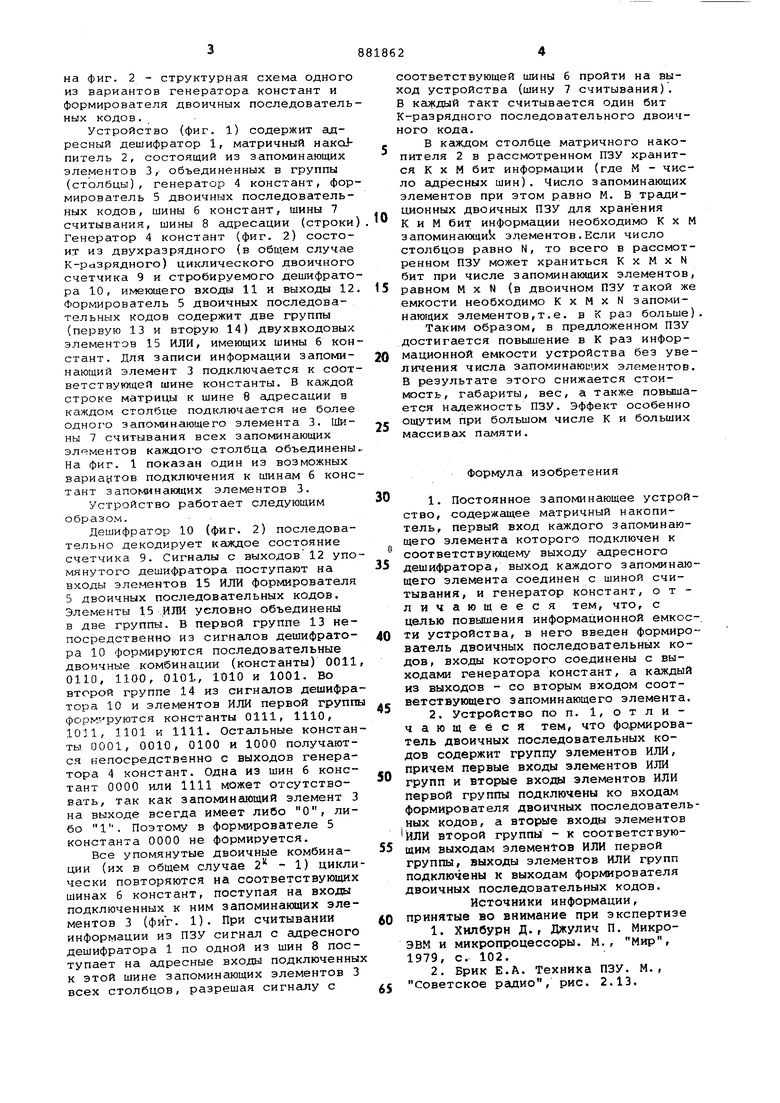

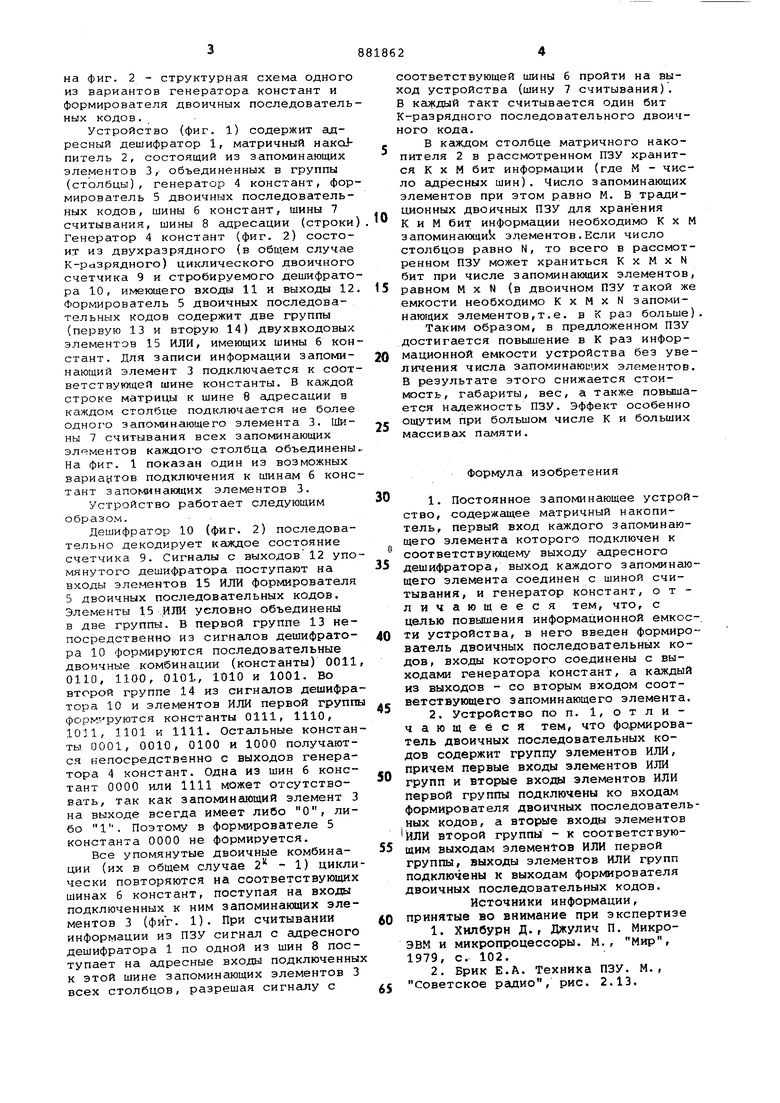

На фиг. 1 изображена структурная схема предлагаемого ПЗУ для случая

30 хранения двух бит в каждой ячейке

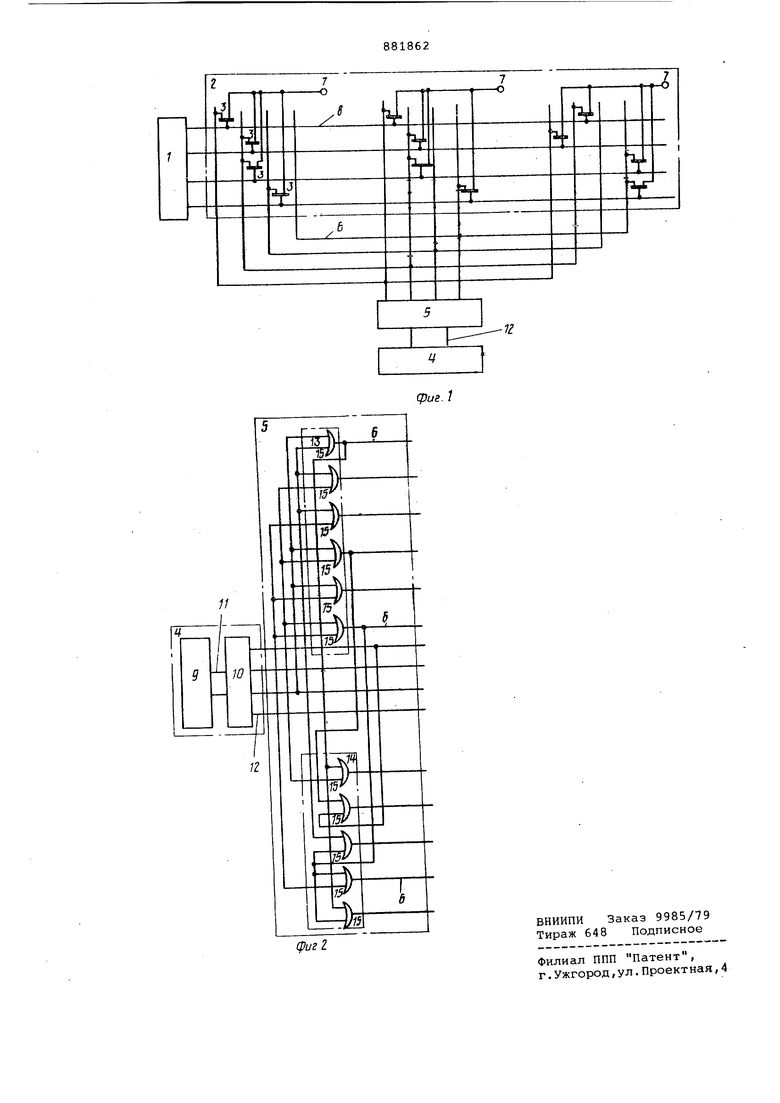

на фиг. 2 - структурная схема одного из вариантов генератора констант и формирователя двоичных последовательных кодов.

Устройство (фиг, 1) содержит адресный дешифратор 1, матричный нако1питель 2, состоящий из запоминающих элементов 3, объединенных в группы (столбцы), генератор 4 констант, формирователь 5 двоичных последовательных кодов, шины 6 констант, шины 7 считывания, шины 8 адресации (строки Генератор 4 констант (фиг. 2) состоит из двухразрядного (в общем случае К-разрядного) циклического двоичного счетчика 9 и стробируемого дешифратора 10, имеющего входы 11 и выходы 12 Формирователь 5 двоичных последовательных кодов содержит две группы (первую 13 и вторую 14) двухвходовых элементов 15 ИЛИ, имеющих шины б констант. Для записи информации запоминающий элемент 3 подключается к соответствующей шине константы. В каждой строке матрицы к шине 8 адресации в каждом столбце подключается не более одного запоминающего элемента 3. Шины 7 считывания всех запоминающих элементов каждого столбца объединены На фиг. 1 показан один из возможных вариа(тов подключения к шинам 6 констант запоминающих элементов 3.

Устройство работает следующим образом.

Дешифратор 10 {фиг. 2) последовательно декодирует каждое состояние счетчика 9. Сигналы с выходов12 упомянутого дешифратора поступают на входы элементов 15 ИЛИ формирователя 5 двоичных последовательных кодов. Элементы 15 ИЛИ условно объединены в две группы. В первой группе 13 непосредственно из сигналов дешифратора 10 формируются последовательные двоичные комбинации (константы) ООН ОНО, 1100, 0101, 1010 и 1001. Во второй группе 14 из сигналов дешифратора 10 и элементов ИЛИ первой группы формгруются константы 0111, 1110, 1011, 1101 и 1111, Остальные константы 0001, 0010, 0100 и 1000 получаются кепосредственно с выходов генератора 4 констант. Одна из шин б констант 0000 или 1111 может отсутствовать, так как запоминающий элемент 3 на выходе всегда имеет либо О, либо 1. Поэтому в формирователе 5 константа 0000 не формируется.

Все упомянутые двоичные комбинации (их в общем случае 2 - 1) циклически повторяются на соответствующих шинах 6 констант, поступая на входы подключенных к ним запоминающих элементов 3 (фиг. 1). При считывании информации из ПЗУ сигнал с адресного дешифратора 1 по одной из шин 8 поступает на адресные входы подключенных к этой шине запоминающих элементов 3 всех столбцов, разрешая сигналу с

соответствующей шины б пройти на выход устройства (шину 7 считывания). В каждый такт считывается один бит К-разрядного последовательного двоичного кода.

В каждом столбце матричного накопителя 2 в рассмотренном ПЗУ хранится К х М бит информации (где М - число адресных шин). Число запоминающих элементов при этом равно М, В традиционных двоичных ПЗУ для хранения К и М бит информации необходимо К х М зaпoминaющиk элементов.Если число столбцов равно N, то всего в рассмотренном ПЗУ может храниться К х М х N бит при числе запоминающих элементов, равном М X N (в двоичном ПЗУ такой же емкости необходимо К х М х N запоминающих элементов,т.е. в К раз больше)

Таким образом, в предложенном ПЗУ достигается повышение в К раз информационной емкости устройства без увеличения числа запоминающих элементов. В результате этого снижается стоимость, габариты, вес, а также повышается Надежность ПЗУ. Эффект особенно ощутим при большом числе к и больших массивах памяти.

Формула изобретения

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-11-15—Публикация

1980-01-09—Подача