(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

1 , ;, ;

Изобретение относится к автоматике и вычислительной технике, в частности к запоминакшзим устройствам (ЗУ).

Известно ЗУ с контролем правильности работы дешифратора и адресных цепей методом шифрации выбранных адресных шин б код адреса, либо сверткой кода адреса и последующим сравнением, либо с кодом адреса, либо ,с. внешней контрольной сверткойкода адреса по некоторому .

Недостатками данного устройства являются большая, избыточность и малое быстродействие, являкяциеся следствием сложности шифратора.

Наиболее близким по технической сущности к изобретению является запоминающая система, использующая устройства с неисправными ячейками, содержащая основную память, дешиф- раторы адреса, постоянную память, дополнительную память. При наличии неисправных адресных шин в основно памяти производится обращение к дополнительной памяти, либо к резервным адресным шинам основной памяти- 2. Недостатком данного устройства является низкая точность контроля.

Цель изобретения - повышение точности контроля.

Поставленная цель достигается

с тем, что в запоминающее устройство с самоконтролем, содержащее матричный накопитель, одни входы которого подключены к выходам дешифратора строк, а другие входы - к выходам 4п дешифратора столбцов, группы программируемых элементов памят1и, входы которых подключены к соответствующим выводам матричного накопителя, дополнительно введены схема сравнения и дискриминаторы, вход каждо15го из которых подключен к выходам программируемых, элементов-памяти соответствующих групп, выходы дискриминаторов подключены к одним из входов схемы сравнения, выходы и

20 другие входы схемы сравнения являются соответственно выходами и входами устройства.

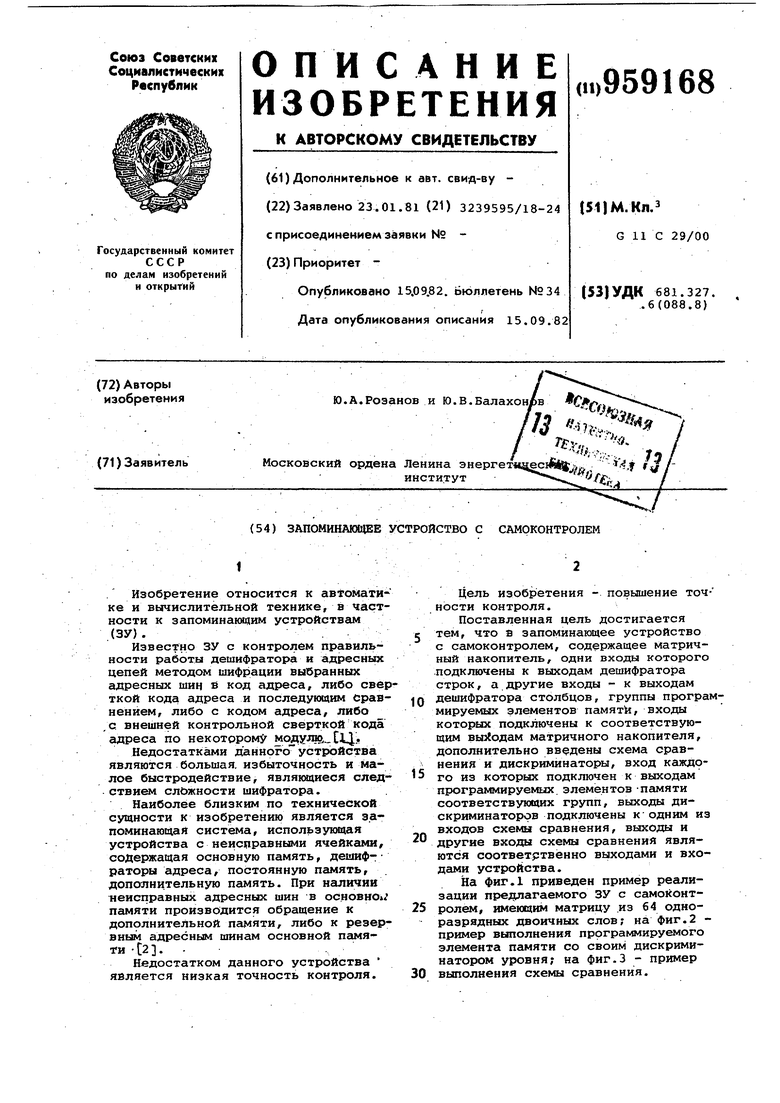

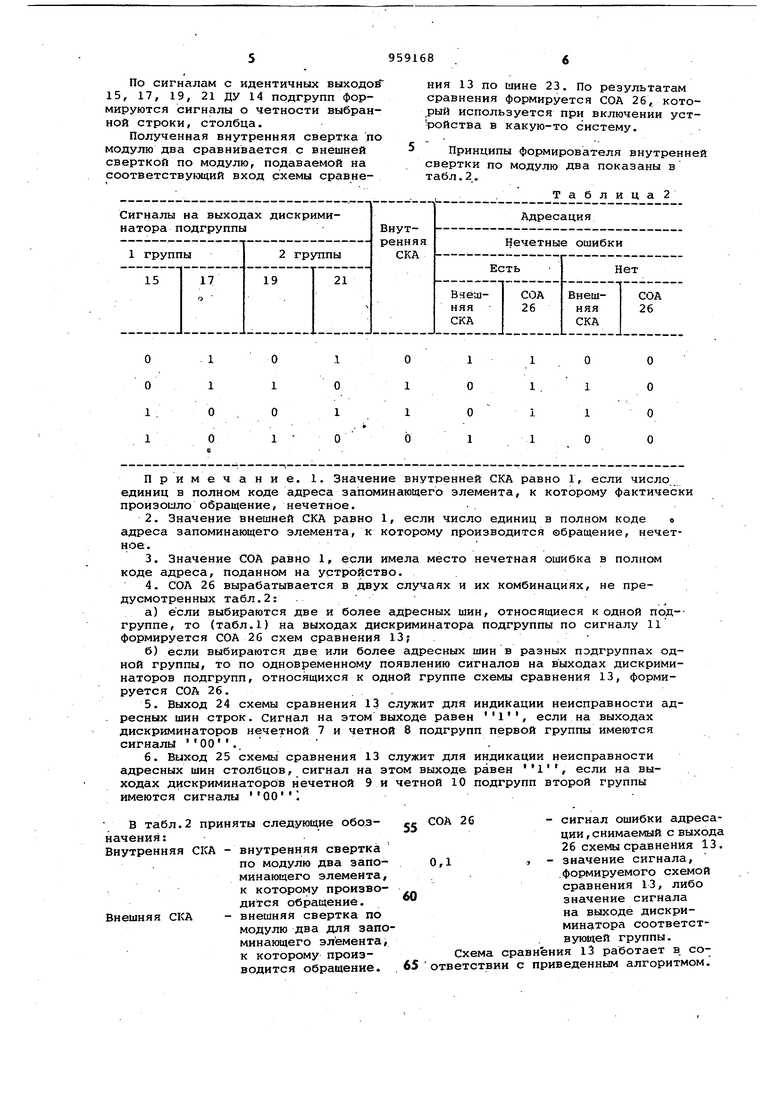

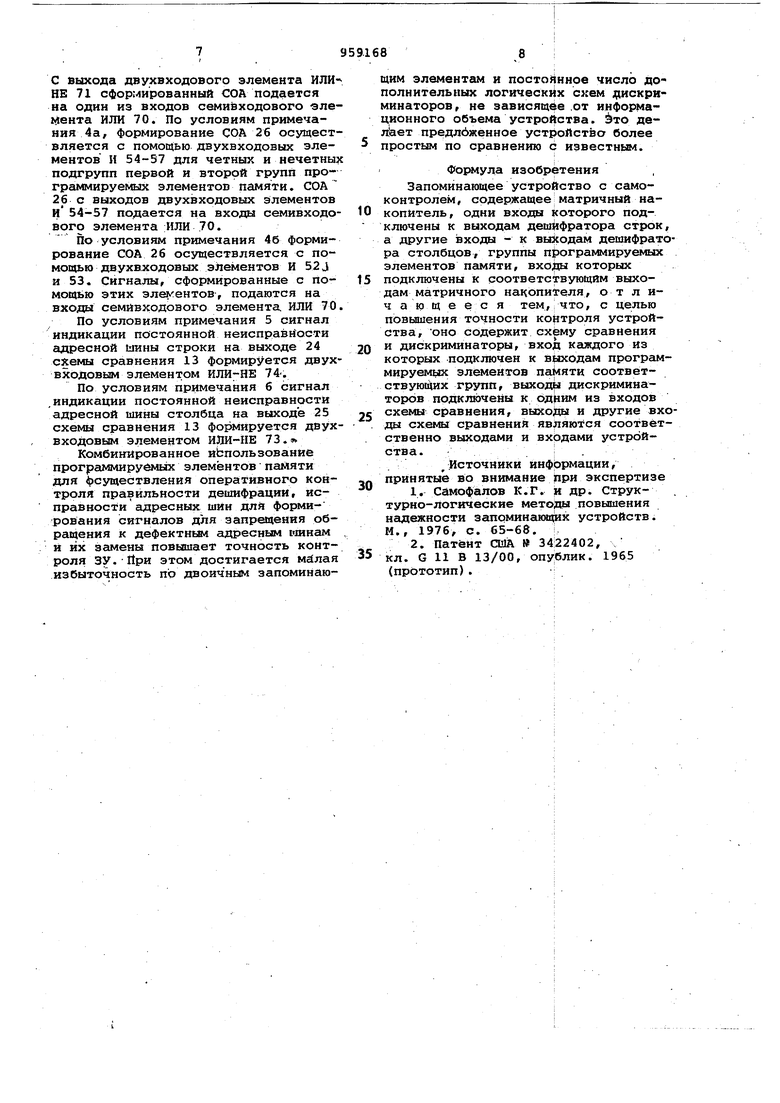

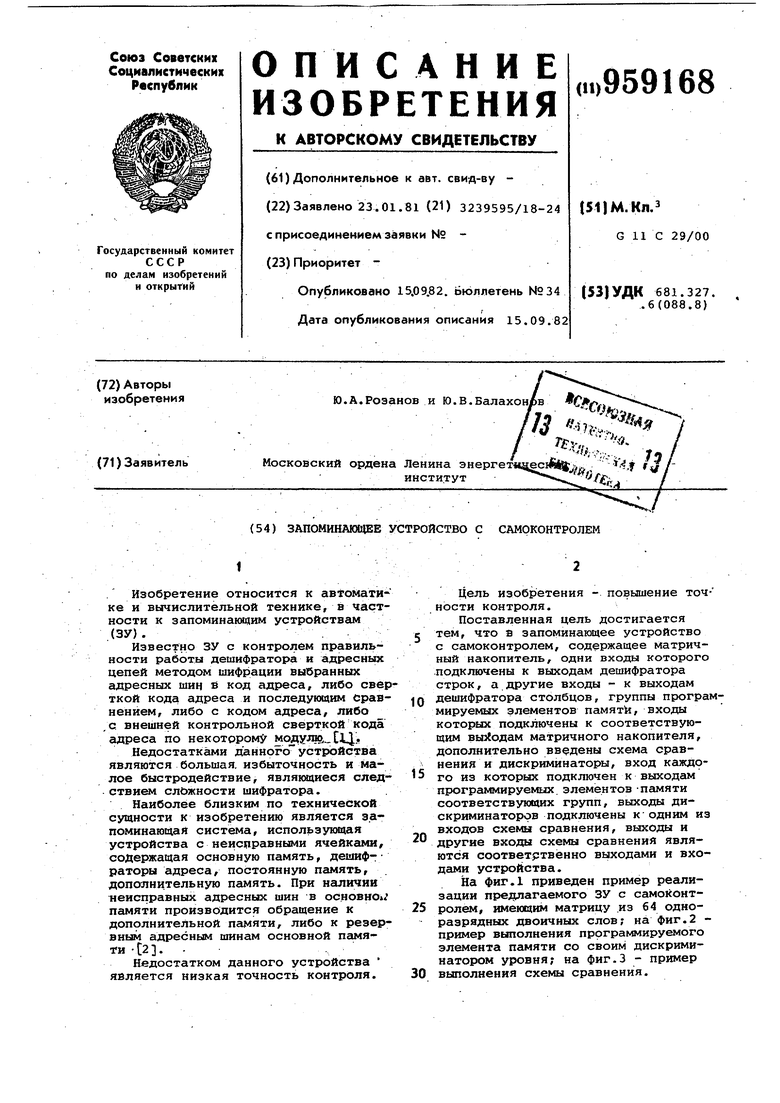

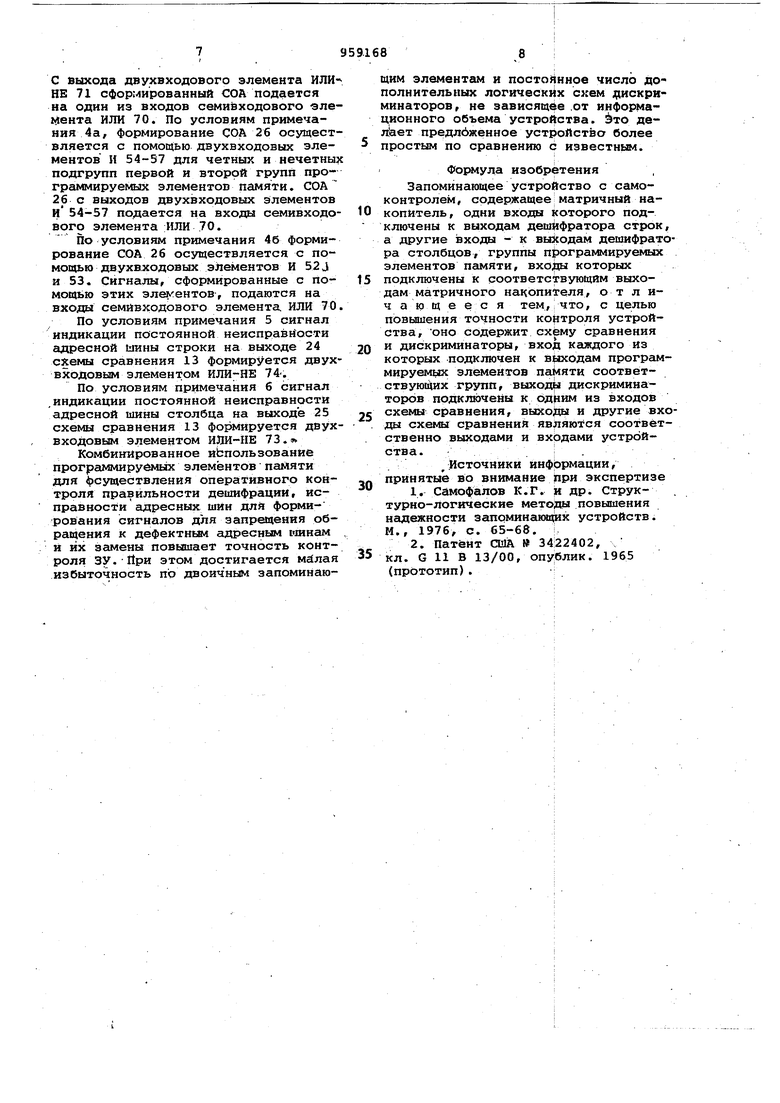

На фиг.1 приведен пример реализации предлагаемого ЗУ с самоконтролем, имеющим матрицу из 64 одно25разрядных двоичных слов; на фиг.2 пример ВЕтолнения программируемого элемента памяти со своим дискриминатором уровня; на фиг.3 - пример

30 выполнения схемы сравнения. Устройство содержит программируемые элемгнты памяти 1 первой группы , нечетной подгруппы, программируемые элементы памяти 2 первой группы чет ной подгруппы, программируемые элементы памяти 3 второй группы нечетной подгруппы, программируемые элеме ITH памяти 4 второй группы четной подгруппы, запоминающие элементы 5, матричный накопитель 6, программируемые элементы памяти со своими дискриминаторами 7-10, дешифратор строк 11, дешифратор столбцов 12, схему сравнения 13, дискриминатор (ДУ) 14 выходы 15 и 16 дискриминатора первой группы четной подгруппы, выходы 17 и 18 дискриминатора первой группы четной подгруппы, выходы 19.и 20 дискриминатора второй группы нечетной подгруппы, выходы 21 и 22 ди скриминатора второй группы четной подгруппы, шину 23 внешней свертки по модулю два полного кода адреса, выходы 24-26 (сигнал ошибка адресации - СОЛ) схемы сравнения, адресные шины 27-42, шины кода адреса 4348-, пороговые усилитель 49 и 50, точ ку 51 на шине, соединяющую резистор и диод, двухвходовые: элементы И 5263, элементы НЕ 64-69, семивходовой элемент ИЛИ 70, элементы ИЛИ-НЕ 7172, элементы ИЛИ-НЕ 73-74. Устройство работает при выполнени следующих условий. После изготовления устройства про изводится его контроль и диагностика с целью обнаружения и локализации всех неисправностей. При обнаружении дефектов, приводящих к неправильной дешифрации некоторых адресных шин, мехзамыканиях производится программирование програ мируемых элементов памяти, соединенных с этими адресными шинами. Запоминающие элементы выбираются с помощью двух адресных шин (стро ки и столбца), с которыми соединены соответственно программируемые элементы памяти первой и второй группы При. обнаружении хотя бы одного дефектного запоминающего элемента производится программирование одного из этих двух программируемых элементов памяти. Потенциал на выбранной адресной шине строки, .столбца при обращении повышается до определенной постоянной величины, одинаковой для любой адресной шины строки, либо столбца, а невыбранные адресные шины строк и столбцов имеют нулевой потенциал. Программируемые элементы памяти устройства могут быть любого типа, лишь бы внутренние сопротивления непрограммированных элементов были при мерно равны постоянной величине/ а внутреннее сопротивление запрограммированного - во много раз больше внутреннего сопротивления незапрограммированного. Например, он может состоять из последовательно соеди- ненных резистора, диода и плавной перемычки. ДУ 14 в подгруппах может быть любого типа. Основным требованием к его параметрам является надежное определение двух уровней тока. Например, он может быть выполнен (фиг.2) |На двух пороговых усилителях, входы которых соединены параллельно и подключены к резистору. Каждый программируемый элемент памяти состоит из последовательно соединенных резистора R, диода Д и плавной перемычки П. Программирование элемента в подгруппах мсэжет осуществляться различным образом, например подачей программирующего потенциала с внешнего источника питания на общую шину подгруппы ив точку 51 на шине, соединяющей резистор и диод, в результате чего плавная перемычка П пережигается повышенным током. Рассмотрим выходные сигналы на идентичных выходах ДУ 14 всех подгрупп в следующих случаях работы устройства.: Отсутствие обращения и дефектов в устройстве. Потенциал всех адресных шин равен нулю, поэтому на входе соответствующего дискриминатора не будет течь ток. При правильной рабрте тракта дешифрации выбирается одна адресная шина строки и в общей шине выбранной подгруппы в первой и второй группе . потечет ток примерно равный IqocT Вследствие сбоя или постоянной неисправности выбираются две и более адресных шин строки, столбца, относящихся к .одной пoдгp5fппe. В этом случае по общей шине подгруппы течет ток . , так как йа двух или более адресных шинах строк, либо столбцов, потенциал првышается до определенной постоянной величины, одинаковой для всех выбранных адресных шин, строк, лиро столбцов.Дискриминатор подгруппы реагирует на отсутствие тока, наличие, , наличие тока 1 1пост тока I общей шине выбранной подгруппы (таблЛ).,j,g „ ц а 1 Постоянный 1 Постоянный 1

По сигналам с идентичных выходой 15, 17, 19, 21 ДУ 14 подгрупп формируются сигналы о четности выбранной строки, столбца.

Полученная внутренняя свертка по модулю два сравнивается с внешней сверткой по модулю, подаваемой на соответствующий вход схемы сравнения 13 по шине 23. По результатам сравнения формируется СОА 26, который используется при включении устройства в какую-то систему.

Принципы формирователя внутренней свертки по модулю два показаны в табл.2.

Таблица2

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Запоминающее устройство | 1982 |

|

SU1023393A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970477A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1010651A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1251188A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| Ассоциативная запоминающая матрица | 1981 |

|

SU1005188A1 |

| Оперативное запоминающее устройство с самоконтролем | 1985 |

|

SU1300569A1 |

Примечание. 1. Значение внутренней СКА равно 1, если число единиц в полном коде адреса запоминающего элемента, к которому фактически произошло обращение, нечетное.

а)если выбираются две и более адресных шин, относящиеся к одной ПО|Д-группе, то (табл.1) на выходах дискриминатора подгруппы по сигналу 11 формируется СОА 26 схем сравнения 13;

б)если выбираются две. или более адресных шин в разных подгруппах одной группы, то по одновременному появлению сигналов на выходах дискриминаторов подгрупп, относящихся к одной группе схемы сравнения 13, формируется СОЛ 26..

дискриминаторов нечетной 7 и четной 8 подгрупп первой группы имеются сигналы 00 ..

няты следующие обоз- внутренняя свертка по модулю два запоминающего элемента, к которому производится обращение. - внешняя свертка по модулю два для запоминающего элемента, к которому производится обращение.

если на выходах

СОА 26 - сигнал ошибки адресации, снимаемый с выхода 26 схемы сравнения 13. 0,1 , - значение сигнала,

.формируемого схемой сравнения 13, либо значение сигнала на выходе дискриминатора соответствующей группы.

Схема сравнения 13 работает в. со-; ответствии с приведенным алгоритмом.

С SbtxoAa двухвходового элемента ИЛИНЕ 71 сформированный СОА подается на один из входов семивходового элемента ИЛИ 70. По условиям примечания 4а, формирование СОА 26 осуществляется с помощью двухвходовых элементов И 54-57 для четных и нечетных подгрупп первой и второй групп программируемых элементов пшляти. СОА 26 с выходов двухвходовых элементов и54-57 подается на входы семивходового элемента :ИЛИ 70.

По условиям примечания 46 формирование СОА 26 осуществляется с помощью двухнходовых элементов И 52J и 53. Сигналы, сформированные с помощью этих элементов, подаются на входы семивходового элемента. ИЛИ 70

По условиям примечания 5 сигнал индикации постоянной неисправности адресной иины строки на выходе 24 схемы сравнения 13 формируется двухвходовым элементом ИЛИ-НЕ 74.

По условиям примечания 6 сигнал .индикации постоянной неисправности адресной шины столбца на выходе 25 схемы сравнения 13 формируется двухвходовнм элементом ИЛИ-ИЕ 73.

Комбинированное иЬпользование программируемых элементов памяти для Осуществления оперативного контроля правильности дешифрации, исправности адресных шин для формирования сигналов для запрещения обра1Я|ения к дефектньм адресным ршнам и их замены повышает точность контроля ЗУ. При этом достигается милая избыточность по двоичным запомиНающим элементам и постоянное число дополнительных логических схем дискриминаторов, не зависящее .от информационного объема устройства. Это предлбженное устройство более простым по сравнению с известным.

Формула изобретения Запоминающее устройство с самоконтролем, содержащее матричный накопитель , одни входы которого подключены к выходам дешифратора строк а другие входы - к вы1содам дешифратра столбцов, группы программируемых элементов , вхо которых подк.шочены к соответствующим выходам матричного накопителя, от л ич ающ е ее я тем, что, с целью повышения точности контроля устройства, ОНО содержит сравнения и дискриминаторы, вход каждого из которых подключен к в|1ходам программируемых элементов пайяти соответствующих групп, выходы дискриминаторов подключены к бдЬим из входов схемы сравнения, выхо;цы и другие вхды схемы сравнения яв тяются соответственно выходами и вхЬдами устройства. .,. . I

/.Источники инфЪрмации, принятые во внимание ;при экспертизе

кл. G 11 В 13/00, опублик. 1965 (прототип).

2$

23

фи1.1

71

Авторы

Даты

1982-09-15—Публикация

1981-01-23—Подача