Изобретение относится к вычислительной технике и может быть использовано для построения постоянных запоминающих устройства (ПЗУ).

Известно ПЗУ, в которое с целью уменьшения количества запоминающих элементов включаются генератор констант и формирователь двоивдых последовательных кодов П.

Недостатком ПЗУ является последовательно считывание групп разрядов, что снижает быстродействие и усложняет управление выборкой информации.

Наиболее близким по технической сущности к предлагаемому является ПЗУ, содержащее матрицу запоминающих элементов, дешифраторы строк и столбцов, причем объе диненные по столбцам выходы запоминающих элементов соединены с входами первой группы коммутатора столбцов, зходы второй группы входов которого соединены с выходами дешифратора столбцов, а выход является выходом устройства, объединенные по строкам первые входы запоминающих элементов соединены с выходами дешифратора строк, входы дешифраторов строк и столбцов являются входами первой и второй групп адресных входов устройства соответственно 2.

Недостатком ПЗУ является сложность, обусловленная большим количеством запоминающих элементов в запоминающей матрице.

Цель изо6рете1шя - упрощение устройства за счет сокраще1тя количества запоминающих элементов.

Поставленная цель достигается тем, что постоянное запоминающее устройство, содержащее матрицу запоминающих элементов, дешифраторы строк и столбцов, коммутатор столбцов, причем объединенные по столбцам выходы запоминаюпдос элементов соединены с входами первой группы входов коммутатора столбцов, входы второй группы входов которого соедине1п 1 с выходами дешифратора столбцов, а выход является выходом устройства, объединешп.1е по строкам первые входы запоминаюшда: элементов соединены с выходами .дешифратора строк, входы дешифраторов строк и столбцов являются входами первой и второй групп адресных входов устройства соответственно, содержит блок формирования логических функций двух переменных, два входа которого являются входами третьей группы адресных входов устройства, а выходы соедине1п 1 с вторыми входами запоминающих элементов в соответствии с размещаемой в них информацией.

Блок формирования логических функций двух переменных содержит два элемента НЕ,

входы которых являются входами блока, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ, входы которых соединены с входами и выходами элементов НЕ, по четыре

двухвходовых элемента И и ИЛИ, причем первые входы первого и второго элементов И к ИЛИ соединены с входом первого элемента НЕ, а первые входы третьего и четвертого элементов И и ИЛИ - с выходом

первого элемента НЕ, вторые входы первого и третьего элементов И и ИЛИ соединены с входом второго элемента НЕ, а вторые входы второго и четвертого элементов И и ИЛИ - с выходом второго элемента НЕ,

выходы элементов И и ИЛИ являются с первого по восьмой выходами блока соответственно, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ являются девятым и десятым выходами блока соответственно, выходы первого и второго злементов НЕ являются одиннадцатым и двенадцатым выходами блока соответственно, вхрды первого и второго элементов НЕ являются тринадцатым и четырнадцатым выходами блока соответственно, шины нулевого потенциала и питания являются пятнадцатым и шестнадцатым выходами блока соответственно.

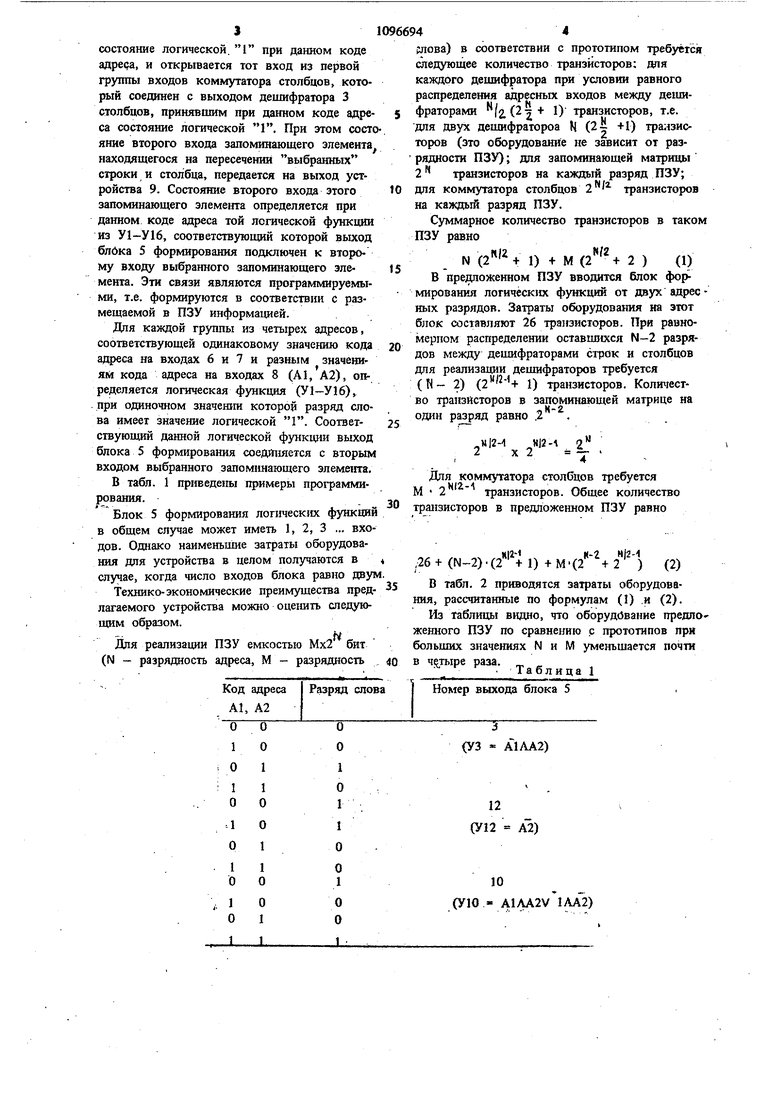

На фиг. 1 приведена схема ПЗУ; на

фиг. 2 схема блока формирования логических функций двух переменных.

Устройство содержит матрицу 1 запоминающих элементов, дешифратор строк 2 и столбцов 3, коммутатор 4 столбцов, блок 5

формирования логических функций двух переменных, три группы адресных входов 6-8 и выход 9. Блок формирования логических функций двух переменных содержит два элемента НЕ 10, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ И и ЭКВИВАЛЕНТНОСТЬ 12, по четыре элемента И 13 и ИЛИ 14. Полный набор логических функций (У1-У16) двух входных переменных (А1, А2) следующий: У1 А1АА2; У2 А1АА2; УЗ

- А1АА2; У4 AlAA2; У5 A1VA2; У6 A1VA2; У7 AlVA2; У8 A 1VA2; У9 A1AA2VA1AA2; У10 A1AA2VA1AA 2; УП А1; У12 А2; У13 А1; У14 А2; У15 0; У16 1.

Постоянное запоминающее устройство работает следующим образом.

Разряды кода адреса 6 и 7 поступают соответственно на входы дешифраторов строк 2 и столбцов 3, оставшиеся два разряда кода адреса 8 поступают на входы блока 5 формирования логических функций. При этом становятся проводящими запоминающие элементы той сфоки матрицы 1, которые соединены с выходом дешифратора 2 строк, принявшим

состояние логической. 1 при данном коде

I адреса, и открывается тот вход из первой грутты входов коммутатора столбцов, который соединен с выходом дешифратора 3 столбцов, принявпгам при данном коде адреса состояние логической 1. При этом состо яние второго входа запоминающего элемента находящегося на пересечении выбранных строки и столбца, передается на выход устройства 9. Состояние второго входа этого запоминающего элемента определяется при данном коде адреса той логической функции из У 1-У 16, соответствующий которой выход блбка 5 формирования подключен к второму входу выбранного запоминающего элемента. Эти связи являются программируемыми, т.е. формируются в соответствии с размещаемой в ПЗУ информацией.

Дня каждой группы из четырех адресов, соответствующей одинаковому значению кода адреса на входах 6 и 7

и разным знамениадреса на входах 8 (AI, А2), oit яМ кода

ределяется логическая функция (У1-У16), при одиночном значешш которой разряд слова имеет значение логической 1. Соответствующий данной логической функции выход блока 5 формирования соединяется с вторым входом выбранного запоминающего элемента,

В табл. 1 приведены примеры программирования.БЛОК 5 формирования логических функций в общем случае может иметь 1, 2, 3 ... входов. Однако наименьщие затраты оборудования для устройства в целом полз чаются в случае, когда число входов блока равно двум

Технико-экономические преимущества предлагаемого устройства можно оценить следующим образом.

Для реализации ПЗУ емкостью Мх2 бит (N - разрядность адреса, М - разрядность

ixnoBa) в соответствии с прототипом требуется следуюпдее количество транзисторов; дпя каждого дешифратора при условии равного распределения адресных входов между дешифраторами Ig. ) транзисторов, т.е. для двух дещифратороа N (2 +1) транзисторов (это оборудование не зависит от разрядности ПЗУ); для запоминающей матрицы 2 транзисторов на каждый разряд ПЗУ; для коммутатора столбцов 2 транзисторов на каждый разряд ПЗУ.

Суммарное количество транзисторов в тако ПЗУ равно

N ( + 1) + М ( + 2 )

(1)

В предложенном ПЗУ вводапгся блок формирозашш логических функций от двух адресных разрядов. Затраты оборудования на этот блок составляют 26 транзисторов. При равномерном распределении оставшихся N-2 разрядов между дешифраторами строк и столбцов для реализации дешифраторов требуется (N 2) ( 1) транзисторов. Количество транзисторов в запоминающей матрице на один разряд равно .2 .

«12-1 ад и 2

I4

Для коммутатора столбцов требуется М транзисторов. Общее количество транзисторов в предложенном ПЗУ равно

Н|2-1

,26 + (N-2)-(2 + 1) + М(2 + 2 ) (2)

В табл. 2 приводятся затраты оборудования, рассчитанные по формулам (1) .и (2).

Из таблицы видно, что оборудование предложенного ПЗУ по сравнению с прототипов при больших значениях N н М уменьшается почти

в четыре раза. „

. Таблица 1

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1987 |

|

SU1443030A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1989 |

|

SU1648205A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU842964A1 |

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2089943C1 |

| Запоминающее устройство | 1979 |

|

SU826418A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

1. ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее матрицу запоминаю-, щих элементов, дешифраторы строк и столбцов, коммутатор столбцов, причем объединенные по столбцам выходы запоминающих элементов соединены с входыми первой группы входов коммутатора столбцов, входы второй группы входов которого соединены с выходами дешифратора столбцов, а выход является выходом устройства, объединенные по строкам первые входы запоминающих элементов соединены с выходами дешифратора строк, входы дешифраторов строк и столбцов являются входами первой и второй групп адресных входов устройства соответственно, о тличающееся тем, что, с целью упрощения устройства, оно содержит блок формирования логических функций двух переме1шых, два входы которого являются входами третьей группы адреснъи входов устройства, а выходы соединены с вторыми входами за11оминающ11х элементов в соответствии с размещаемой в них информацией. 2. Устройство по п. 1, о -т л и ч а ющ е -е с я тем, что блок форм11рова1шя логических функций двух переменных содержит два элемента НЕ, входы которых являются входами блока, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ, входы которых соединены с входами и выходами элементов НЕ, по четыре двухвходовых элемента И и ИЛИ, причем первые входы первого и второго элементов .И и ИЛИ соединенъ с входом первого элемента НЕ, а первые входы третьего и четвертого элементов И и ИЛИ - с выходом первого элемента НЕ, вторые входы первого и третьего элементов И и ИЛИ соединены с входом второго элемента НЕ, а вторые входы второго и четвертого элементов И и ИЛИ - с выходом второго элемента НЕ, выходы элементов И и ИЛИ являются с первого по восьмой выходами блока соответственно, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ являются девятым и десятым выходами блоСО СГ) ка соответственно, выходы первого и второго элементов НЕ являются одиннадцатым и , х двенадцатым выходами блока соответственно, входы первого и второго элементов НЕ явля- I со 4: ются трннадцать1М и четырнадцатым выходами блока соответственно, Ш1шы нулевого по тенциала и питания являются пятнадцатым и шестнадцатъ1м выходами блока соответственно.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Постоянное запоминающее устройство | 1980 |

|

SU881862A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микрюпроцессоры системы | |||

| М., Мир, 1981, с | |||

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-06-07—Публикация

1982-07-16—Подача