1

Изобретение относится к области цифровой обработки сигналов, в частности к цифровой фильтрации, и может быть использовано в различных цифровых комплексах, например, для обра- 5 ботки случайных процессов.

Известный рекурсивный фильтр Г содержит запоминающее устройство, умножитель, накапливающий сумматор и реализует решение разностного уравне- 10 ния вида

V-... (1) ,iO 1-1

- значение входного сигна- |5

где X

H-V

ла в n-i-M такте; У„. - значение выходного сигнала в n-i-M такте; а- , Ь - коэффициенты определяющие частотную характе- 20 ристику Лильтра.

В таком фильтре можно реализовать произвольную частотную характеристику, для чего необходимо лишь задать соответствующие коэффициенты а- и bi. 25

Недостатком фильтра является широкий диапазон изменения значений сигнала, обрабатываемого в блоках фильтра, и выходного сигнала, соответствующий диапазону изменения входного 30

сигнала, что приводит к необходимости увеличивать разрядность блоков фильтра и устройств обработки отфильтрованного (выходного) сигнала для достижения приемлемой точности.

Известный цифровой фильтр 2 наиболее близок по технической сущности и решаемой задаче к предлагаемому техническому решению. В известном фильтре коэффициент передачи автоматически регулируется обратно пропорционально изменению уровня фильтруемого сигнала. Это позволяет сузить диапазон изменения амплитуды выходного сигнала и, следовательно, уменьшить разрядность устройств обработки отфильтрованного (выходного) сигнала. Известный цифровой фильтр содержит соединенные в кольцо запоминающее устройство выборок, умножитель и накапливающий сумматор, а также запоминающее устройство коэффициентов, подключенное ко второму входу умножителя, блок сравнения, к первому входу которого подключен выход умножителя, ко второму входу - датчик уровня выходного сигнала, а к выходу - интегратор, выход которого подсоединен к выходу запоминающего устройства коэффициетов. Работа этого фильтра тактирована (частотой квантования входного сигнал В каждом такте цифровой фильтр прини Йает входной сигнал, вырабатывает вспомогательный выходной сигнал, а затем и сам выходной сигнал. Очередное значение входного сиг;йала поступает в запоминающее устрой ство выборок, где хранятся предыдущи 3 научения входного и выходного вспомо :гательного сигналов. Из запоминающего устройства выборок указанные знач ния входного и вспомогательного выходного сигналов поочередно подаются на умножитель, где умножаются на значения соответствующих коэффициен тов, поступающие из запоминающего устройства коэффициентов. Результаты перемножения складываются в накапливающем сумматоре. Полученное значе;ние суммы, являющееся вспомогатель;ным выходным сигналом текущего такта записывается в запоминающее устройст :во выборок и поступает на умножитель В это же время на второй вход умножителя с запоминающего устройства коэффициентов поступает значение кор ректирующего множителя. Указанный множитель регулирует коэффициент передачи фильтра. Полученный в результате умножения сигнал является выходным сигналом цифрового фильтра. : Этот сигнал подается на блок сравнения , на второй вход которого проходи сигнал порогового уровня от датчика уровня выходного сигнала. В блоке сравнения выходной сигнал сравнивается с пороговым уровнем. Полученная при этом разность между пороговым уровнем и выходным сигналом поступает на вход интегратора. Интегратор вырабатывает си-гнал, изменение которого -находится в обратной зависимост от среднего отклонения выходного сиг нала от порогового уровня. Сигнал с выхода интегратора подается на запоминающее устройство коэф(Т1Ициентов и в качестве значения корректирующего .множителя на умножитель в очередном такте для умножения на него очередного значения вспомогательного выходного сигнала. Значение выходного сигнала 2 при этом определяется вы ражением Zfl С У„, где Yf - значение вспомогательного выходного сигнала в п-м такте, определяемого форму лой (1) ; С - значение корректирующего множителя, определяемого уравнением С Со k (А- IZDd-t, (3) о где А - сигнал порогового уровня; k - коэффициент интегрирования. В уравнении (3) для упрощения дискретное интегрирование разности порогового уровня и выходного сигнала заменено непрерывным интегрированием. Недостатком известного фильтра является то, что несмотря на сужение диапазона выходного сигнала фильтра динамический диапазон сигнала, обрабатываемого в самом фильтре, остается широким, а именно равным динамическому диапазону входного сигнала. Это обстоятельство приводит к необходимости увеличивать разрядность блоков фильтра, т. е. к увеличению его вёсо-габариткых характеристик. Цель изобретекия - сокращение оборудования путем уменьшения разрядности его блоков б-ез сужения динамического диапазона входного сигнала, который мохсет обработать фильтр. Сущность изобретения закгаочается в том, что производится предварительная регулировка.мощности входного сигнала путем умножения его на корректирующий множитель, приводящая к уменьшению его динамического диапазона, затем такой вспомогательный входной сигнал обрабатывается в фильтре, после чего осуществляется окончательная регулировка мощности отфильтрованного сигнала путем умножения его на тот же корректирующий множитель. Так как уменьшение динамического диапазона сигнала происходит таким образом, что мощный сигнал несколько ослабляется, а слабый сигнал усиливается, после каждого умножения сигнала на корректирующий множитель производится сдвиг произведения в сторону старших разрядов, чтобы сместить динамический диапазон отрегулированного сигнала к верхней границе динамического диапазона входного сигнала и работать всегда с достаточно мощным сигналом. Поставленная цель достигается тем, что в ш- фровой фильтр, содержащий блок памяти выборок, блок памяти коэффициентов, накапливающий сумматор, блок умножения, блок сравнения, датчик уровня выходного сигнала, выход которого соединен с парны - входом блока сравнения, выходом подключенного ко входу интегратора, выход накапливающего сумматора подсоединен ко входу блока памяти выборок а выход блока памяти коэффициентов - к первому входу блока умножения, введены KOivcvsyTaTOp выборок, коммутатор коэффициентов, комглутатор слагаемых и регистр сдвига, выход которого является выходом фильтра и соединен со вторым входом блока сравнения и первым входом коммутатора слагаемых. При этом выход коммутатора cлaгae 1ыx, подключен ко входу накапливающего сумматора, выходом соединенного с первым входом коммутатора выборок, выход которого подключен ко второму входу блока

умножения, выходом соединенного со входом регистра сдвига и вторым входом коммутатора слагаемых, третий вход которого является нулевым входом .фильтра. Выход интегратора подключен к первому и второму входу коммутатора коэффициентов, третий вход которого служит установочным входом фильтра, выход блока памяти выборок подключен ко второму входу коммутатора выборок, третий вход которого является входом фильтра. Вход блока памяти коэффициентов соединен с выходом коммутатора коэффициентов соединен с выходом коммутатора коэффициентов, управляющий вход которого объединен с управляющими входами коммутатора выборок и коммутатора слагаемых и является управляющим входом фильтра.

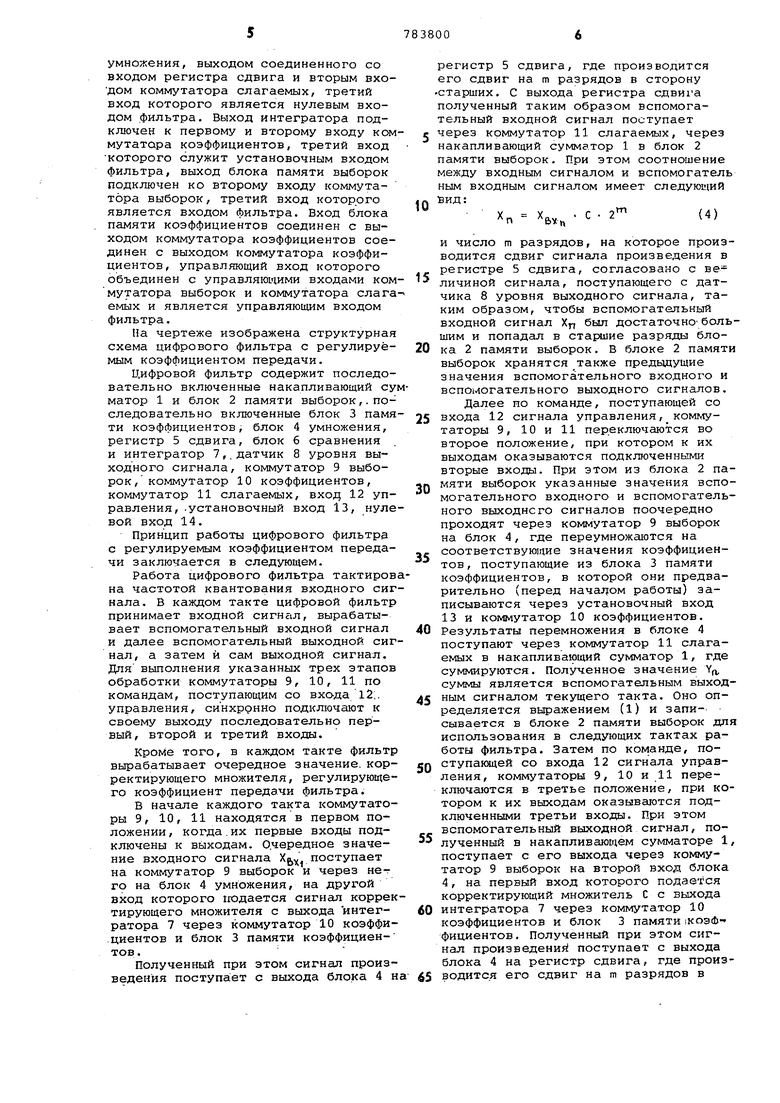

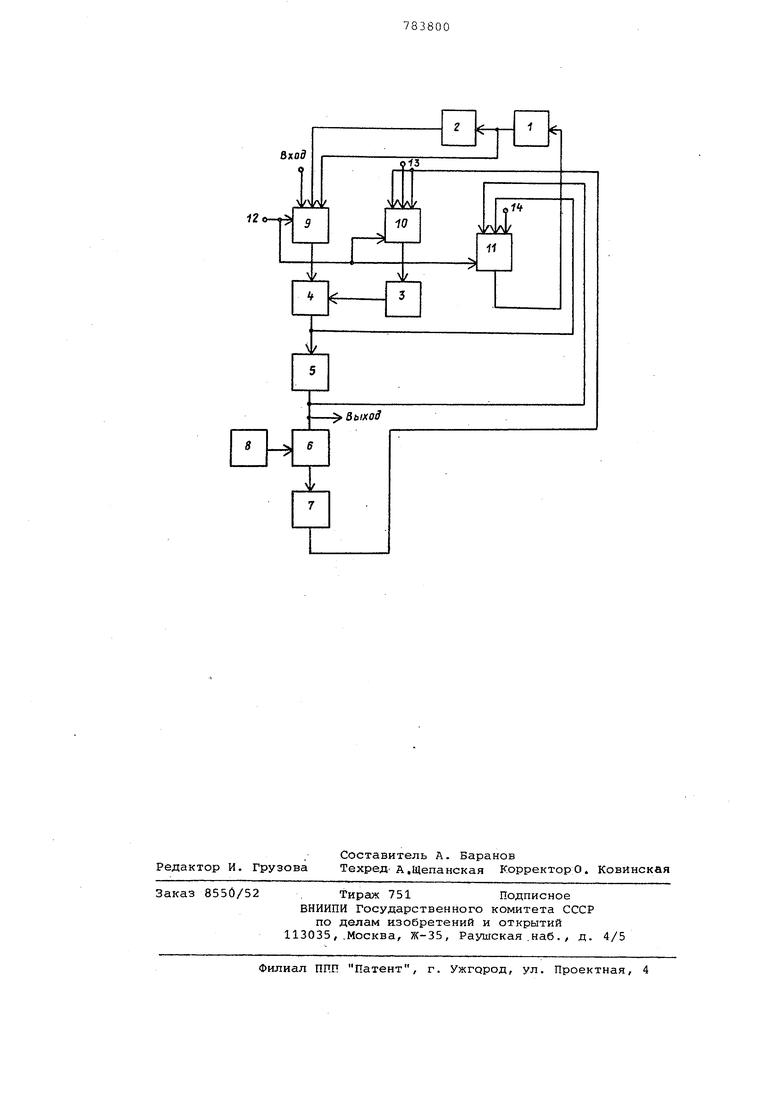

Па чертеже иэображена структурная схема цифрового фильтра с регулируемым коэффициентом передачи.

Цифровой фильтр содержит последовательно включенные накапливающий суматор 1 и блок 2 памяти выборок,. последовательно включенные блок 3 памяти коэффициентов, блок 4 умножения, регистр 5 сдвига, блок 6 сравнения и интегратор 7,,датчик 8 уровня выходного сигнала, коммутатор 9 выборок , коммутатор 10 коэффициентов, коммутатор 11 слагаемых, axofl 12 управления, .установочный вход 13, нулевой вход 14.

Принцип работы цифрового фильтра с регулируемым коэффициентом передачи заключается в следующем.

Работа цифрового фильтра тактировна частотой квантования входного сигнала. В каждом такте цифровой фильтр принимает входной сигнгш, вырабатывает вспомогательный входной сигнал и далее вспомогательный выходной сигнал, а затем и сам выходной сигнал. Для выполнения указанных трех этапов обработки коммутаторы 9, 10, 11 по командам, поступающим со входа 12;. управления, синхррнно подключают к своему выходу последовательно первый, второй и третий входы.

Кроме того, в каждом такте фильтр вырабатывает очередное значение, корректирующего множителя, регулирующего коэффициент передачи фильтра.

В начале каждого такта коммутаторы 9, 10, 11 находятся в первом положении , когда.их первые входы подключены к выходам. Очередное значение входного сигнала Xg поступает на коммутатор 9 выборок и через нет го на блок 4 умножения, на другой вход которого тюдается сигнал корректирующего множителя с выхода интегратора 7 через коммутатор 10 коэффи.циентов и блок 3 памяти коэффициентов.

Полученный при этом сигнал произведения поступает с выхода блока 4 н

регистр 5 сдвига, где производится его сдвиг на m разрядов в сторону старших. С выхода регистра сдвиха полученный таким образом вспомогательный входной сигнал поступает J через коммутатор 11 слагаемых, через накапливающий сумматор 1 в блок 2 памяти выборок. При этом соотношение между входным сигналом и вспомогатель ным входным сигналом имеет следующий вид:

0

(4)

п бу

и число m разрядов, на которое производится сдвиг сигнала произведения в регистре 5 сдвига, согласовано с ве

5 личиной сигнала, поступающего с датчика 8 уровня выходного сигнала, таким образом, чтобы вспомогательный входной сигнал Х был достаточно большим и попадал в старшие разряды бло0ка 2 памяти выборок. В блоке 2 памяти выборок хранятся также предыдущие значения вспомогательного входного и вспомогательного выходного сигналов. Далее по команде, поступающей со входа 12 сигнала управления, комму5таторы 9, 10 и 11 переключаются во второе положение, при котором к их выходам оказываются подключенными вторые входы. При этом из блока 2 памяти выборок указанные значения вспо0могательного входного и вспомогательного выходного сигналов поочередно проходят через коммутатор 9 выборок на блок 4, где переумножаются на соответствующие значения коэффициен5тов, поступающие из блока 3 памяти коэффициентов, в которой они предварительно (перед Ha4aJjoM работы) записываются через установочный вход 13 и коммутатор 10 коэффициентов.

0 Результаты перемножения в блоке 4 поступают через коммутатор 11 слагаемых в накапливающий сумматор 1, где суммируются. Полученное значение Yfj, суммы является вспомогательным выходным сигналом текущего такта. Оно оп5ределяется выражением (1) и записывается в блоке 2 памяти выборок для использования в следующих тактах работы фильтра. Затем по команде, поступакнцей со входа 12 сигнала управ0ления, коммутаторы 9, 10 и 11 переключаются в третье положение, при котором к их выходам оказываются подключенными третьи входы. При этом вспомогательный выходной сигнал, по5лученный в накапливающем сумматоре 1, поступает с его выхода через коммутатор 9 выборок на второй вход блока 4, на первый вход которого подается корректирующий множитель С с выхода интегратора 7 через коммутатор 10

0 коэффициентов и блок 3 памяти КоэФ фициентов. Полученный при этом сигнал произведений поступает с выхода блока 4 на регистр сдвига, где производится его сдвиг на m разрядов в

5

С -орону старших и формируется таким образом выходной сигнал Z| оильтра, ойределенньзй выражением:

m

Z,

С 2

п

; Накапливающий сумматор 1 подключается через ком лутатор слагаемых к нулевому входу 14 и обнуляется.

Выходной сигнал с регистра 5 сдвига подается на блок б сравнения, на второй вход которого поступает сигнал порогового уровня с датчика 8 уровня выходного сигнала. В блоке 6 сравнения выходной сигнал сравнивается с noporoBbmi уровнем. Полученная при этом разность между пороговым уровнем и выходным сигналом поступает на вход интегратора 7., Интегратор 7 вырабатывает сигнал,изменение котррого находится в обратной завксимрсти от срецнехо от лоне ни я вьг сод;- ого сигнала от порогового уровня. Сигнал с выхода интегратора 7 подается на входы Ko.vLMyTaTopa 10 коэисЬицнемто и г качестве корректирук щего мно;кителя С через блок 3 памят;- коэффициентов поступает з соответс;твующие мометы времени на блок 4, как было показ:ано.

: Значение корректирующего множител С при этом определяется зыражен -тем (3) ,

Эффективность предложенного цифрового фильтра с регулируемым коэффициегнтом передачи соетоит в том, что корректирующий множитель С используется для регулирования не только выходного но и входного сигнала в соответствии с равенством (.4) . При этом наряду со етабилрЗаи.лей выходного сигнала фильтра про;-:зводится частичная (предварительная) регулировка мощности входного еигналга. И хотя последний стабилизируется не полностью вследствие неопределенности его спектральных характеристик, тем не менее его динамический д -1апазон существенно сужается, что позволяет снизить разрядность блоков цифрового фильтра.

Ввиду наличия обргггной зависимости между мощностью входного сигнала и значением корректирующего г«1ножителя С, вытекающий из выражений (1-5) , большим значениям входного сигнала соответствуют м;длые 3Via4eHHH С и наоборот , При умножении таких сомножителей на умножителе с фиксированной, запятой результат умножения всегда существенно мены-iie максимально возможного значения выходного сигнала умножителя. Сдвиг результата в старших разрядов после каждого умножения на корректирующий множи:тель позволяет приблизить резу;1ьтат умножения к максимально возможному

значению :; при суже1н-1и динамического диапазона сигнала за счет регулирования сместить его к верхней границе динамического диапазона сигнгша до регулирования.

Эффективность изобретения особенно высока при обработке нестационарных сигналов е широклм динамическим диапазоном значений, с изменяющимися спектральными характеристиками и т. д., так как позволяет решить задачу обработки сигнала фильтром, соcTOHiiiHM из блоков с малой разрядностью .

Формула изобретения

Цифровой фильтр с peгyлиpye ым коэффициентом передачи, содержащий блок памяти выборок, блок памяти коэффициентов, накапливающий суь-тматор, блок умножения, блок сравнения, датчик уровня выходного сигнала, выход которого соединен с первым входом блока сравнения, выход которого подключен ко входу интегратора, выход накапливак 1Г;его еум1.матора подключен ко входу блока памяти выборок, а выход блока памя.ти коэффициентов соединен с первым входом блока умножения, о т л ич а 10 щ к и с я тем, что, с целью сокращения оборудования, он содержит коммутатор выборок, коммутатор коэффициентов, коммутатор слагаемых и регистр сдвига/ выход которого является выходом фильтра и соединен со вторым входом блока сравнения и первым входом коммут.тора слагаемых, выход которого подключен ко входу накапливающего сум.1атора, выход которого соединен с первым входом коммутатора выборок, выход которого НОДКЛЮчен ко второму вхо;ду блока умножения, выход ;оторого соединен со входом регистра сдвига и вторым входом кО№ утатора слагаемых, трети; вход которого является нулевым входом фильтра, выход интегратора подключен к первому и второму входу коммутатора коэффициентов, третий вход которого является установоч.ным входом фильтра выход блока памяти выборок подключен кО второму входу «ог-/1мутатора выборок третий вход которого является входом фильтра, вход блока памяти коэффициентов соединен с выходом коммутатора коэффициентов, ун1эавляющий вход которого объединен с управляющими входами коммутатора выборок и коммутатора елаraeVibix и .является управля-сг им входом фильтра.

Источники информации, принятые во внима - ие при экспертизе

1. Патент .США 3703692, кл. 235-152, опубл. 1973.

2. Авторское свидетельство СССР

J е.

G 0(

577533,

Вход

12 о

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с регулируемым коэффициентом передачи | 1978 |

|

SU734711A1 |

| Арифметическое устройство для цифровой фильтрации с автоматической регулировкой усиления | 1979 |

|

SU881987A1 |

| Цифровой нерекурсивный фильтр | 1980 |

|

SU942247A1 |

| Цифровой фильтр | 1976 |

|

SU577533A1 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1352622A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Цифровой нерекурсивный фильтр | 1983 |

|

SU1124430A1 |

| Устройство для цифровой фильтрации с автоматической регулировкой усиления | 1988 |

|

SU1509935A1 |

| Цифровой нерекурсивный фильтр нечетного порядка | 1985 |

|

SU1314445A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

Авторы

Даты

1980-11-30—Публикация

1979-01-29—Подача