1

Изобретение относится к связи и может использоваться в цифровых системах передачи ииформации.

Известио устройство для приема фазоманипулированных сигналов, содержащее последовательно соединенные усилитель и -фазовый детектор, выходы которого подключены к входам решающего блока и блока восстановления посылок, выход которого соединен с соответствующим входом решающего блока, а также декодер, выходы которого подключены к входам потребителя дискретной информации и регистратора ошибок 1.

Однако известное устройство имеет сравнительно невысокую помехоустойчивость.

Целью изобретения является повыщениё помехоустойчивости.

Для этого в устройство введены коммутатор, блок обнаружения сигналов и последовательно соединенные умножитель частоты, делитель частоты и фазовращатель, выходы которого подключены к дополнительным входам фазового детектора, вход которого соединен с входом умножителя частоты, при этом выходы решающего блока подключены к входам коммутатора и блока обнаружения сигналов, выходы которого соединены с дополнительными входами коммутатора, выходы которого подключены к входам декодера, дополнительный вход которого соединен с выходом блока восстановления посылок и соответствующим входом блока обнаружения сигналов.

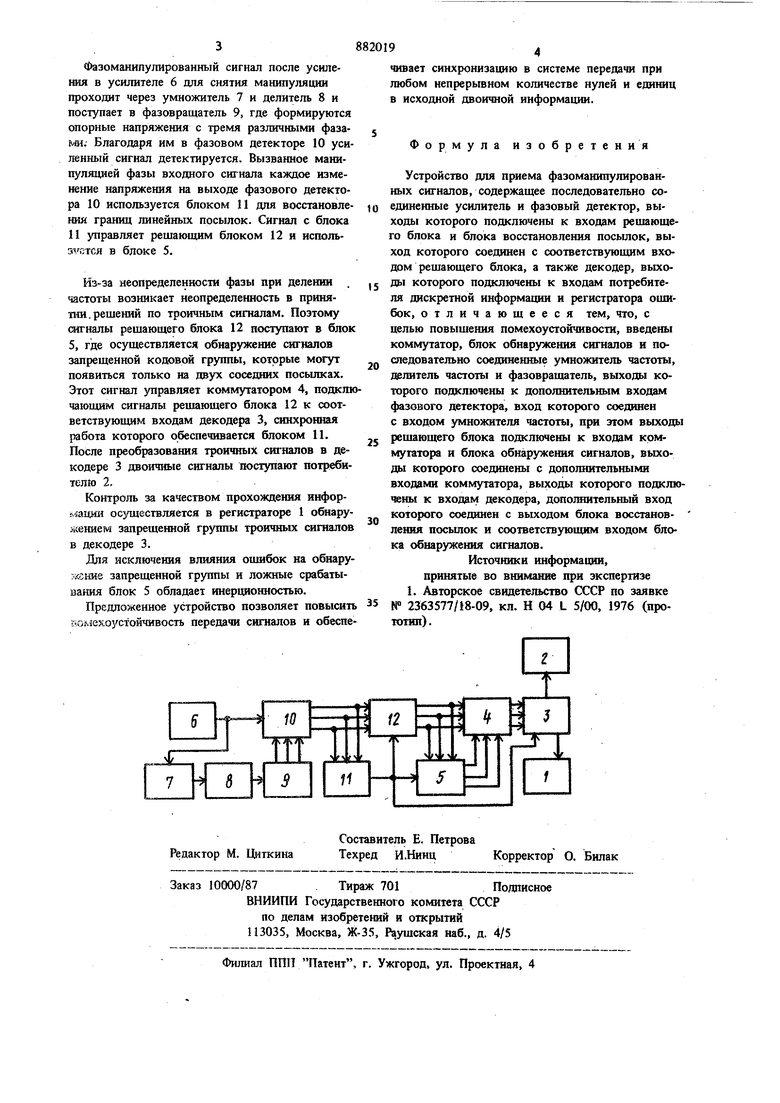

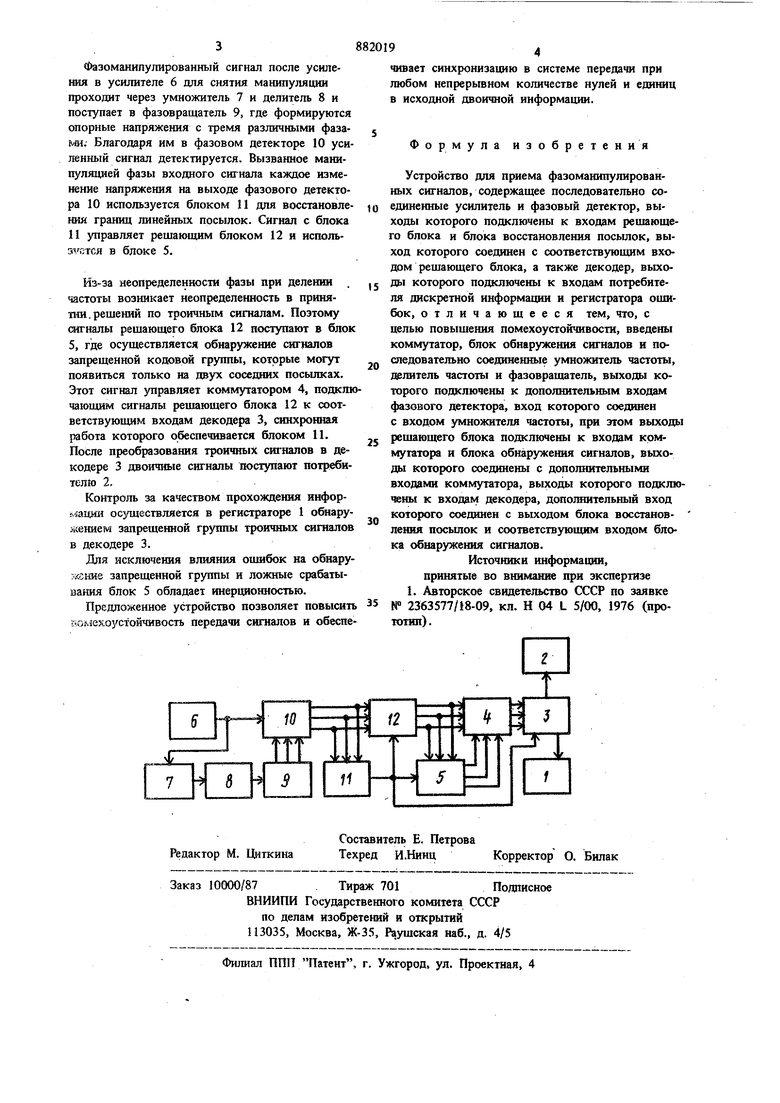

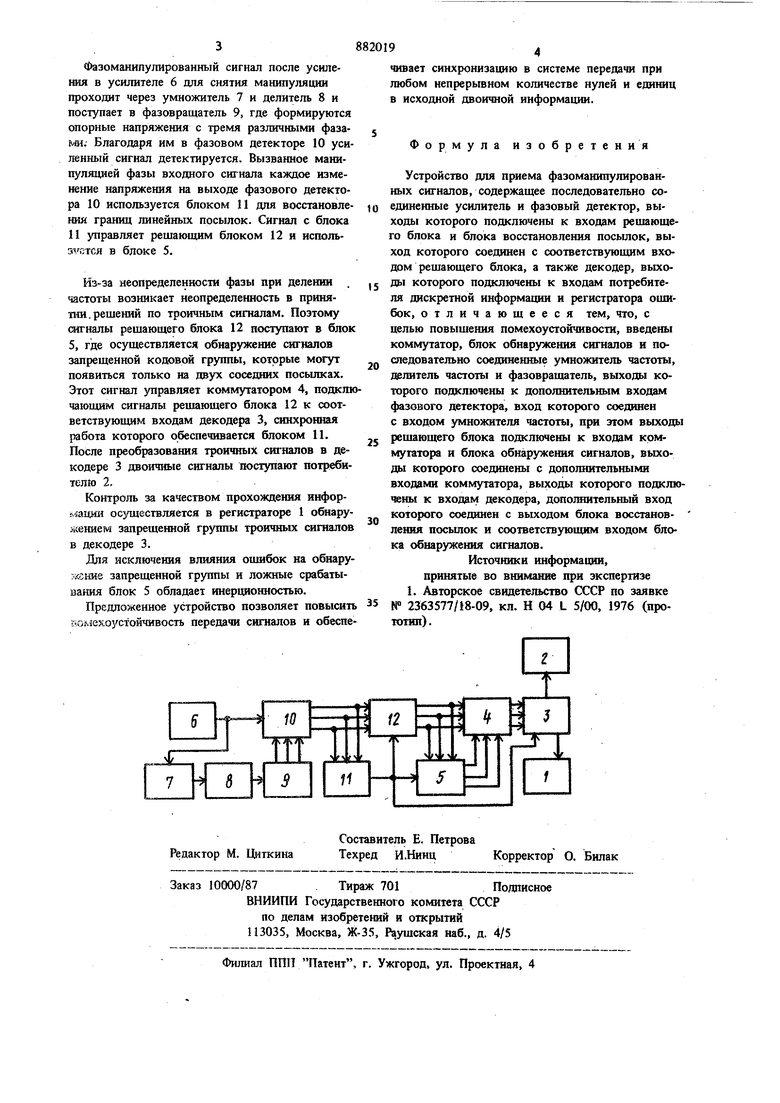

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство для приема фазоманипулированHbix сигналов содержит регистратор 1 ошибок, потребитель 2 дискретной информации, декодер 3, коммутатор 4, блок 5 обнаружения сигналов, усилитель 6, умножитель 7 частоты, делитель 8 частоты, фазовращатель 9, фазовый детектор 10, блок 11 восстановления посылок и решающий блок 12.

Устрой гво работает следующим образом.

В передающем устройстве (на чертеже не показано) подлежащую передаче двоичную информацию преобразуют в троичный сигнал, которым модулируют по фазе несущую, излучаемую по каналу связи (на чертеже не показан). Фазоманипулированный сигнал после усиления в усилителе 6 для снятия манипуляции проходит через умножитель 7 и делитель 8 и поступает в фазовращатель 9, где формируются опорные напряжения с тремя различными фазами; Благодаря им в фазовом детекторе 10 усиленный сигнал детектируется. Вызванное манипуляцией фазы входного сигнала каждое изменение напряжения на выходе фазового детектора 10 используется блоком 11 для восстановления границ линейных посылок. Сигнал с блока 11 управляет решающим блоком 12 и используется в блоке 5. Из-за неопределенности фазы при делении . частоты возникает неопределенность в принятии, рещений по троичным сигналам. Позтому опналы рещающего блока 12 поступают в блок 5, где осуществляется обнаружение сигналов запрещенной кодовой группы, которые могут появиться только на двух соседних посылках. Этот сигнал управляет коммутатором 4, подклю чающим сигналы решающего блока 12 к соответствующим входам декодера 3, синхронная работа которого обеспечивается блоком 11. После преобразования троичных сигналов в декодере 3 двоичные сигналы поступают потребителю 2, Контроль за качеством прохождения информации осуществляется в регистраторе 1 обнаружением запрещенной группы троичных сигналов в декодере 3. Для исключения влияния ошибок на обнаруriCHHe запрещенной группы и ложные срабатывания блок 5 обладает инерционностью. Предложенное устройство позволяет повысить гимехоустойчивость передачи сигналов и обеспе чивает синхронизацию в системе передачи при любом непрерывном количестве нулей и единиц в исходной двончной информации. Формула изобретения Устройство для приема фазомашшулированных снгналов, содержащее последовательно соединенные усилитель и фазовый детектор, выходы которого подключены к входам решающего блока и блока восстановления посылок, выход которого соединен с соответствующим входом решающего блока, а также декодер, выходы которого подключены к входам потребителя дискретной информации и регистратора ошибок, отличающееся тем, что, с целью повышения помехоустойчивости, введены коммутатор, блок обнаружения сигналов и последовательно соединенные умножитель частоты, делитель частоты и фазовращатель, выходы которого подключены к дополнительным входам фазового детектора, вход которого соединен с входом умножителя частоты, при этом выходы решающего блока подключены к входам коммутатора и блока обнаружения сигналов, выходы которого соединены с дополнительными входами коммутатора, выходы которого подключены к входам декодера, допошштельный вход которого соединен с выходом блока восстановления посылок и соответствующим входом блока обнаружения сигналов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство ХСР по заявке N« 2363577/18-09, кл. Н 04 L 5/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор трехпозиционных фазоманипулированных сигналов | 1989 |

|

SU1713115A1 |

| Система передачи дискретной инфор-МАции | 1976 |

|

SU818026A1 |

| Система передачи дискретной информации | 1976 |

|

SU688082A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Устройство для приема дискретной информации | 1978 |

|

SU790358A1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Устройство для передачи и приема дискретных сообщений | 1988 |

|

SU1552394A1 |

| Устройство для блочной синхронизации цифровой системы передачи | 1983 |

|

SU1124438A1 |

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

Авторы

Даты

1981-11-15—Публикация

1979-03-19—Подача