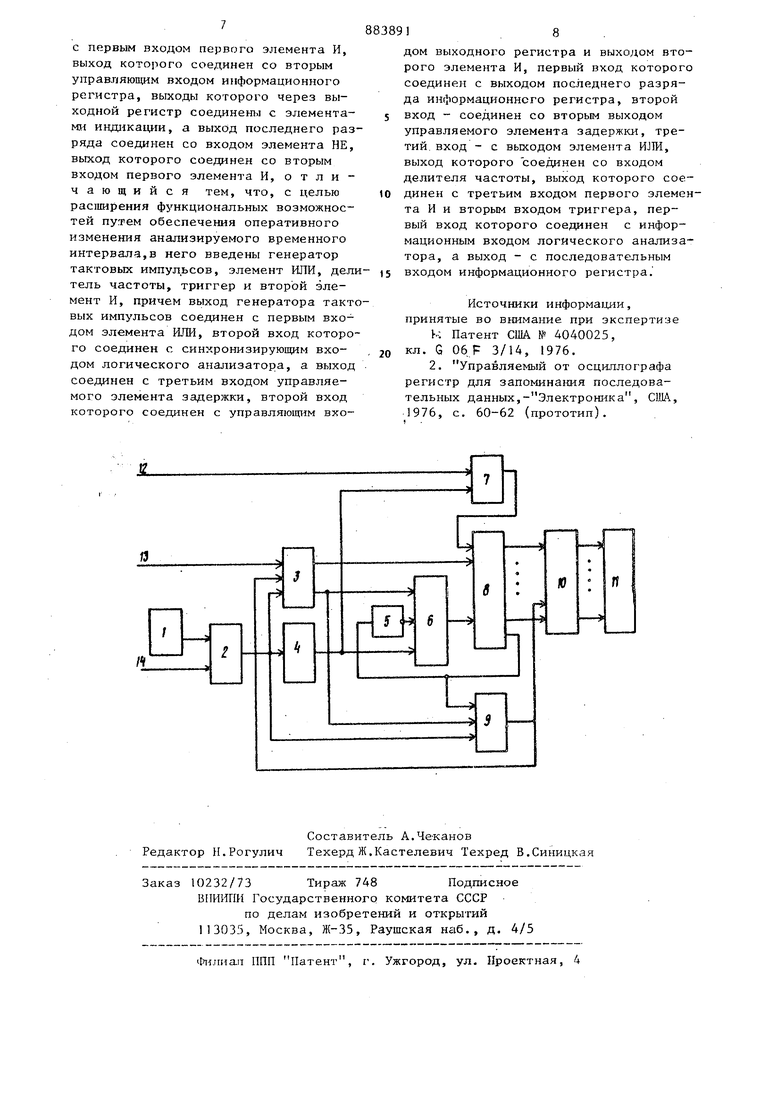

Изобретение относится к автоматике и вычислительной технике и может быть использовано при исследовании цифровых приборов. Известно устройство отображения цифровой информации при помощи регистра, синхронизируемого осциллографом, которое содержит регистры, стробируемую регулируемую линию задержки, элементы И, отображение инф мации осуществляется на светодиодах или аналогичных дискретных индикаторах flj . Наиболее близким по технической сущности к предлагаемому изобретению является устройство, содер жащее последовательно-параллельный регистр, выходной регистр, индикатор на светодиодах, схему задержки, элемент И, элемент НЕ.Задержка запускающего импульса производится при помощи стробируемой задержанной развертки осциллографа. Информация на экране осциллографа не отображается ДТоследний просто обеспечивает индикацию времени и, в том числе, обозначает начало последовательного слова, отображаемого на светодиодах. Когда закончится временной интервал, определяемый задержкой,, стробируемый задержанный выход осциллографа разрешает синхроимпульсу проверяемого прибора произвести сдвиг последовательного регистра, в результате чего, в него вводятся последовательные данныр. 2. Недостатком известного устройства является то, что оно отображает на светодиодном экране неизменяемый строго определенный временной интервал, равный Т п, где Т - отображаемый временной интервал;t - период следования синхроимпульсов;П - количество световых ячеек (светодиодов и не позволяет оперативно .перестраи вать форматы изображения в процессе работы.Кроме того, устройство может работать только совместно с осциллографом. Цель изобретения - расширение фун кциональцых возможностей устройства путем обеспечения оперативного изменения анализируемого временного интервала. Поставленная цель достигается тем что в логический анализатор, содержа щий информационный .регистр, выходной регистр, элементы индикации,- управля емый элемент задержки, первый элемен И, элемент НЕ, причем первый выход управляемого элемента задержки соединен с первым управляюищм-входом информационного регистра, -второй выход - с первым входом первого элемен та И, выход которого соединен со вто рым управляющим входом информационно го регистра, выходы- которого через выходной регистр соединены-с элементами индякади -, а выход последнего разряда соединен со входом элемента НЕ, выход которого йоединен со вторы входом первого элемента И, введены генератор тактовых импульсов, элемен ИЛИ, делитель частоты, триггер и вто рой элемент И, причем выход генератора тактовых импульсов соединен с первым входом элемента РШИ, второй вход которого соединен с синхронизирующим входом логического анализатора, а выход соединен с третьим входом управляемого элемента задержки, второй вход которого соединен с управляющим входом выходного ре- гистра и выходом второго элемента И, первый вход которого соединен с выходом последнего разряда информационного регистра,второй вход соединен со вторым выходом управляемого элемента задержБи, третий : вход - с выходом элемента ИЛИ, выход которого соединен со входом делителя частоты,выход которого соединен с третьим входом первого- элемента И и вторым входом триггера, первый вход которого соединен с информационным входом логического анализатора, а выход - с последовательным входом информацион ного регистра. На чертеже представлена блок-схе ма логического анализатора. Анализатор содеряшт генератор 1 тактовых импульсов, элемент ИЛИ 1 2, управляемый элемент 3 задержки, делитель.4 частоты , элемент НЕ 5, первый элемент И 6, триггер 7 Прием , информационный регистр 8, второй элемент И 9, выходной регистр 10, элементы 1 I индикации-, информационный вход Вход последовательных данных (шина 12J , запускающий вход Запускающий сигнал (шина 13) , синхронизирующий вход Вход синхроимпульсов (тайна 14). Приведенная схема относится к 8-бит словам последовательного типа, однако ее можно приспособить к слову любой длины, изменив число разрядов в регистрах. Количество разрядов информационного регистра 8-девять,а выход Horq,регистра 10 - восемь. Количество регистров может быть более одного и соответствовать числу разрядов в исследуемой шине. Упорядоченная-матрица светодиодов более удобна для отображения двоичного числа, чем многоканальный осциллограф, а выходной регистр позволяет исследовать однократные процессы. Информационный регистр 8 преобразует последовательные данные в формат, необходимый для отображения на ищ5икаторе,используется для счета битов, образующих последовательные слова. Выходной регистр 10 запоминает полученное в результате преобразования слово в параллельной форме и управляет элементами 11 индикации, которые отображают данные. Предварительно последовательные данные вводятся в триггер 7 Прием. В информационный регистр 8 предварительно введены единица в первый разряд и нули во все остальные. Синхроимпульсы проверяемого -прибора или тактовые импульсы генератора 1 такГтовых импульсов (при работе от внутренней частоты устройства) производят сдвиг, информационного регистра 8, в результате чего .в последний вводятся, последовательные данные с триггера 7 Прием. После подачи надлежащего количества сдвиговых импульсов единица, которая предварительно введена в первый разряд .информационного регистра 8, достигает последнего, разряда, чем -запрещается прохождение дальнейших сдвиговых импульсов, в результате чего информационный регистр 8 удерживает необходимое число бит информации (в данном конкретном случае восьми только что собранног слова данных. Регулируемый элемент 3 задержки предназначен для задержки и стробирования запускающего сигнала (шина 3) . Код задержки устанавливается на тумблерах пульта управления устройства (|пульт управления на схеме не показан). Когда закончится временной интервал, определяемый управляющим элементом 3 задержки, на первом входе элемента И 6 устанавливается разрешающий потенциал для импульсов мас штабной частоты с делителя 4 частоты (f| - частота масштабная), кото рые производят сдвиг информационног регистра 8, Делитель 4 частоты (формировател масштабной частоты определяет частоту следования сдвиговых импульсов в зависимости от кода масштаба, уст навливаемого на пульте управления устройства. Кодом масштабной частоты устанавливается цена деления индикатора, например светодиодного. Генератор 1 тактовых импульсов вырабатывает импульсы для синхронизации внешних сигналов. Устройство может работать и от внешних импульсов синхронизации (шина 14J . Устройство работает соедуюш 1М образом. Запускающий сигнал (шина 13) поступает на управляемый элемент 3 задержки, где стробируется и задерживается. Незадержанный стробированный импульс устанавливает единицу в первый разряд информационного регист ра 8 и нули во все остальные. Когда закончится временной интервал, определяемый задержкой, синхронно с синхроимпульсом (импульс с генератора I или синхроимпульсами, поступающими по шине I4J элемента 3 задержки разрешает импульсам масштабной частоты произвести сдвиг информационного регистра В. В результате чего в него вводятся последовательные данные, поступающие по цепи: шина 12, первый вход триггера 7 Прием, выход триггера 7, информационный вход информационного регистра В, После подачи надлежащего количест ва импульсов (в рассматриваемом случае восьми единица, которая пред варительно введена в первый разряд. 14 достигает последнего, этим запрещает:ся прохождение дальнейших сдвиговых импульсов (на второй вход элемента И. 6 поступает инвертированный сигнал с последнего разряда информационного, регистра 8, в результате чего информаци-онный регистр 8 удерживает 8 бит только что собранного слова. Единица в последнем разряде информационного регистра 8 на входе элемента И 9 разрешает передачу данных из информационного регистра 8 в выходной регистр 10, который служит для управления элементами индикации (светоизлучающими диодами. Дискретный элемент 3 задержки позволяет задерживать просматриваемый интервал с дискретностью, зада-г ваемой частотой тактовых импульсов или внешних синхроимпульсов (шина 14J , просматриваекаш временной интервал можно изменять за счет изменения . масштабной частоты f м. Код масштаба задается с пульта управления устройства и определяет частоту масштабных импульсов, являющихся сдвиговыми импульсами информационного регистра 8. Предлагаемое устройство по сравнению с известным позволяет отображать информацию информационной шины много больших форматов, т.е., анализировать уровни на большем временном интервале, что следовательноS расширяет его функциональные возможности. . С целью обеспечения работы устройства от собственных синхронизирующих импульсов оно дополнено генератором тактовых импульсов. ,, Кроме того, выполнение упр.авляемого элемента задержки в виде дискретной логической схемы позволяет с большой заданной точностью задавать требуемую задержку начала анализируемого интервала и упростить в общем устройство. Формула изобретения Логический анализатор, содержащий нформационный регистр, выходной регистр, элементы индикации, управляемый элемент задержки, первый элемент , элемент НЕ, причем первый выход правляемого элемента задержки соеинен с первым управляющим входом инормационного регистра, второй выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для поиска перемежающихся неисправностей | 1986 |

|

SU1381511A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1254489A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для контроля временных диаграмм логических блоков | 1979 |

|

SU788111A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

Авторы

Даты

1981-11-23—Публикация

1980-03-13—Подача