1

Изобретение относится к вычислительной технике и предназначено для использования в специализированных и универсальных вычислительных устройствах.

Известно устройство для вычисления элементарных функций (в том числе и потенцирования) табличного типа на основе постоянного запоминающего устройства, в котором регистр адреса блока памяти используется в качестве регистра аргумента, а регистр числа блока используется в качестве регистра аргумеита, а регистр числа блока памяти - в качестве регистра результата устройства. Такое устройство имеет предельно высокое быстродействие 11.

Однако область применения ограничивается 8-12 двоичными разрядами аргумента,, поскольку объем блока памяти быстро pacfer с увеличением разрядности аргумента. Современные вычислительные система работают с аргументами, имеющими разрядность до 64 разрядов.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для йотёиггиг рованиЯг содержащее регистр аргумеита, два блока памяти, узел сдвига, триггер, блок управления, три коммутатора, выполненные в виде схем

f И-ИЛИ, буферный регистр, регистр результата, сумматор 12.

Однако известное устройство при достаточно высоком быстродействии имеет большие объемы блоков памяти.

Цель изобретения - сокращение

10 аппаратурных затрат на блок памяти.

Поставленная цель достигается тем, что устройство, содержащее регистр аргумента, блок памяти, буферный регистр, три коммутатора и реISгистр результата, причем выход старших разрядов регистра аргумента подключен к первому информационному . входу первого коммутатора, выход которого через блок памяти соедданеи

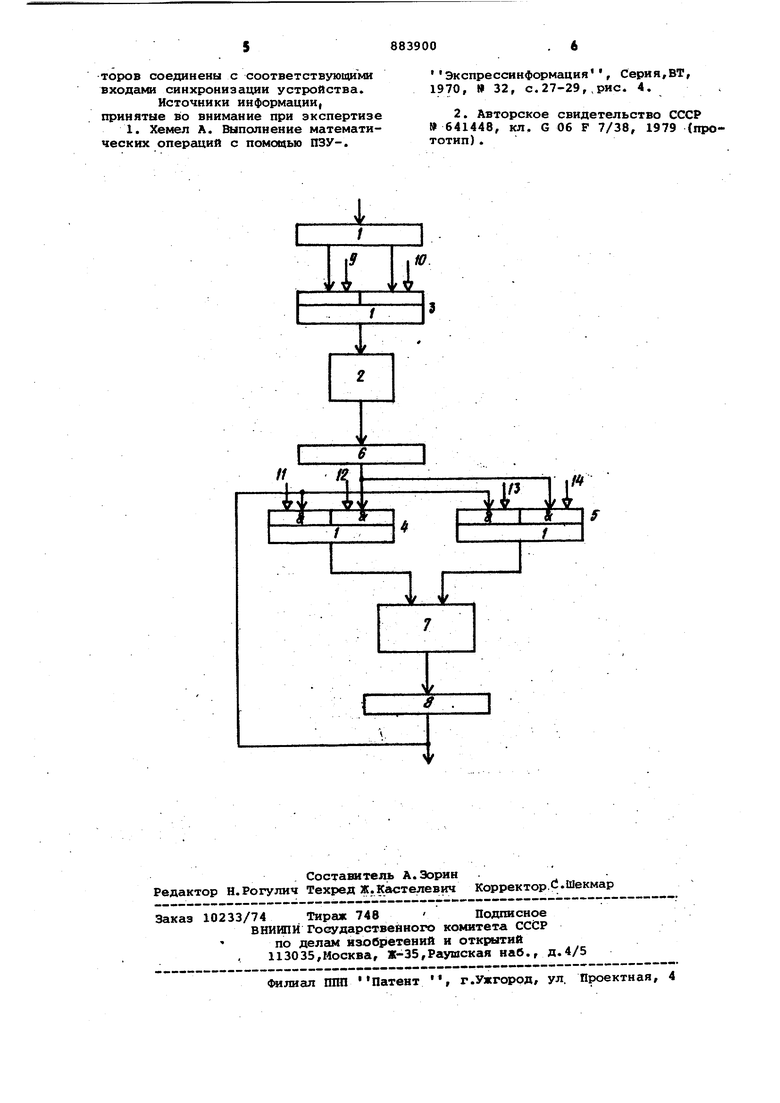

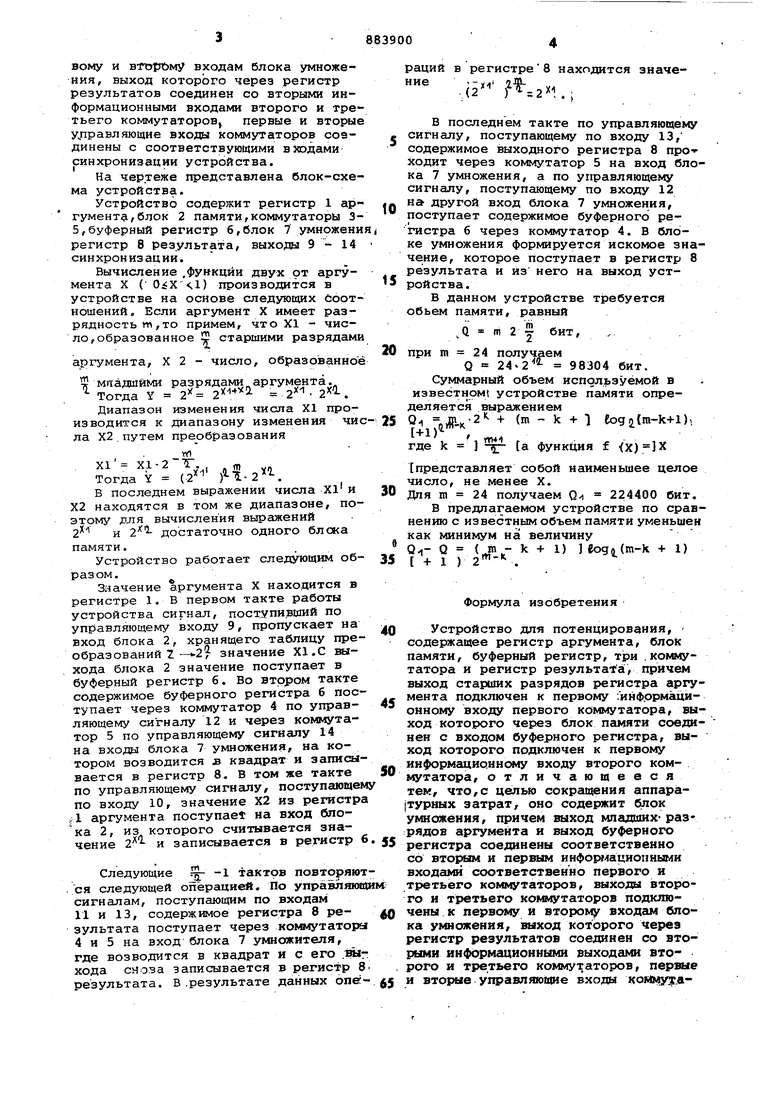

20 с входом буферного регистра, выход которого подключен к первому )мационному входу второго коммутатора, содержит блок умножения, причем выход млафшх разрядов регистра аргу 5 мента и выход буферного регистра соединены соответственно со вторым и первым информационными входами соответственно первого и третьего коммутаторов, выходы второго и третьего -коммутаторов подключены к первому и вторйму входам блока умножения, выход которого через регистр результатов соединен со вторыми информационными входами второго и третьего коммутаторов первые и вторые у гравляющие входы коммутаторов соэдинены с соответствующими входами синхронизации устройства. На чертеже представлена блок-схема устройства. Устройство содержит регистр 1 аргумента/блок 2 памяти,коммутаторы 35,буферный регистр б,блок 7 умножени регистр 8 результата, выходы 9 - 14 синхронизации. Вычисление .функции двух от аргумента X ( OiXXl) производится в устройстве на основе следующих Соотношений. Если аргумент X имеет разрядность т,то примем, что XI - число,образованное ;2 старшими разрядами аргумента, X 2 - число, образованно 2 мпадшйми разрядами аргумента. Тогда У 2 2 2 . Диапазон изменения числа XI производится к диапазону изменения чи ла Х2.путем преобразования XI XI - 2 )if.2 Тогда Y , . В последнем выражении числа XI и Х2 находятся в том же диапазоне, поэтому рля вычисления выражений 2X1 JJ достаточно одного блсжа памяти. Устройство работает следующим образом. Значение аргумента X находится в регистре 1. В первом такте работы устройства сигнал, ПОСТУПИВШИЙ по управл5тощему входу 9, пропускает на вход блока 2, хранящего таблицу пре образований 7 значение XI.С выхода блока 2 значение поступает в буферный регистр 6. Во втором такте содержимое буферного регистра 6 пос тупает через коммутатор 4 по управляющему сигналу 12 и через коммутатор 5 по управляющему сигналу 14 на входы блока 7 умножения, на котором возводится S квадрат и записы вается в регистр 8. В том же такте по управляющему сигналу, поступающе по входу 10, значение Х2 из регистр :;1 аргумента nocTynaet на вход бпока 2, из которого считывается значение 2 и записывается в регистр Следующие % 1 тактов повтрряю . СИ следующей операцией. По управляю сигналам, поступающим по входам 11 и 13, содержимое регистра 8 результата поступает через коммутато1« 4 и 5 на вход блока 7 умножителя, где возводится в квадрат и с его .та хода сяоза записывается в регистр 8 результата. В .результате данных one раций в регистре8 находится значев последнем такте по управляющему сигналу, поступающему по входу 13, содержимое выходного регистра 8 проходит через коммутатор 5 на вход блока 7 умножения, а по управляющему сигналу, поступающему по входу 12 на другой вход блока 7 умножения, поступает содержимое буферного регистра б через коммутатор 4. В блоке умножения формируется искомое значение, которое поступает в регистр 8 результата и из него на выход устройства. В данном устройстве требуется обьем памяти, равный ,Q m 2 I бит, . при m 24 получаем Q 24-2 98304 бит. Суммарный объем используемой в известном) устройстве памяти определяется выражением QI г.уР-к + (т - k + 1 Cogft{m-k+l).. +1)% где k -т а функция f х)Х представляет собой наименьшее целое число, не менее X. Для m 24 получаем Q 224400 бит. В предлагаекюм устройстве по сравнению с известным объем памяти уменьшен как минимум на величину Q-I- Q m,f k + 1) eog5(m-k + 1) I + 1 J л . Формула изобретения Устройство для потенцирования, содержащее регистр аргумента, блок памяти, буферный регистр, т)ри .коммутатора и регистр результата;, причем выход старших разрядов регистра аргумента подключен к первому :инфррмационному входу первого коммутатора, выход которого через блок пгичяти соединен с входом буферного регистра, выход которого подключен к первому информационному входу второго коммутатора, отличающееся тем, что,с целью сокргицения аппара|турных затрат, оно содержит блок умножения, причем выход млгщших-разрядов аргумента я выход буферного регистра соединены соответственно со вто|жт и первым инфосм/сацнопньоли входами соответственно первого и третьего коммутаторов, выходы второго и третьего кокянутаторов подключены к первому и второ входгш блока умножения, выход которого через регистр результатов соединен со вторыми информационными выходами второго и третьего коммутаторов, первые и вторые управляю1цне входы уоаиу яторов соединены с соответствующими входами синхронизации устройства.

Источники информации, принятые Bio внимание при экспертизе 1. Хемел А. Выполнение математических операций с помощью ПЗУ-.

Экспрессинформация, Серия,ВТ, 1970, 32, с.27-29,,рис. 4.

2. Авторское свидетельство СССР №641448, кл. G Об F 7/38, 1979 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1987 |

|

SU1425708A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

L1

|/«

г.д

i

j-j

Авторы

Даты

1981-11-23—Публикация

1980-03-19—Подача