1288695

порядка мантиссы и знака мантиссы синхронизирующие сигналы. Устройство соответственно. На вход 24 поступают работает в конвейерном режиме. 1 ил.

1

Изобретение относится к вычислительной технике и предназначено для использования в вычислительных устройствах при обработке данных в форматах с фиксированной и плавающей запятой.

Целью изобретения является повышение быстродействия и расширение функциональных возможностей устройства за счет обработки чисел в формате с плавающей запятой

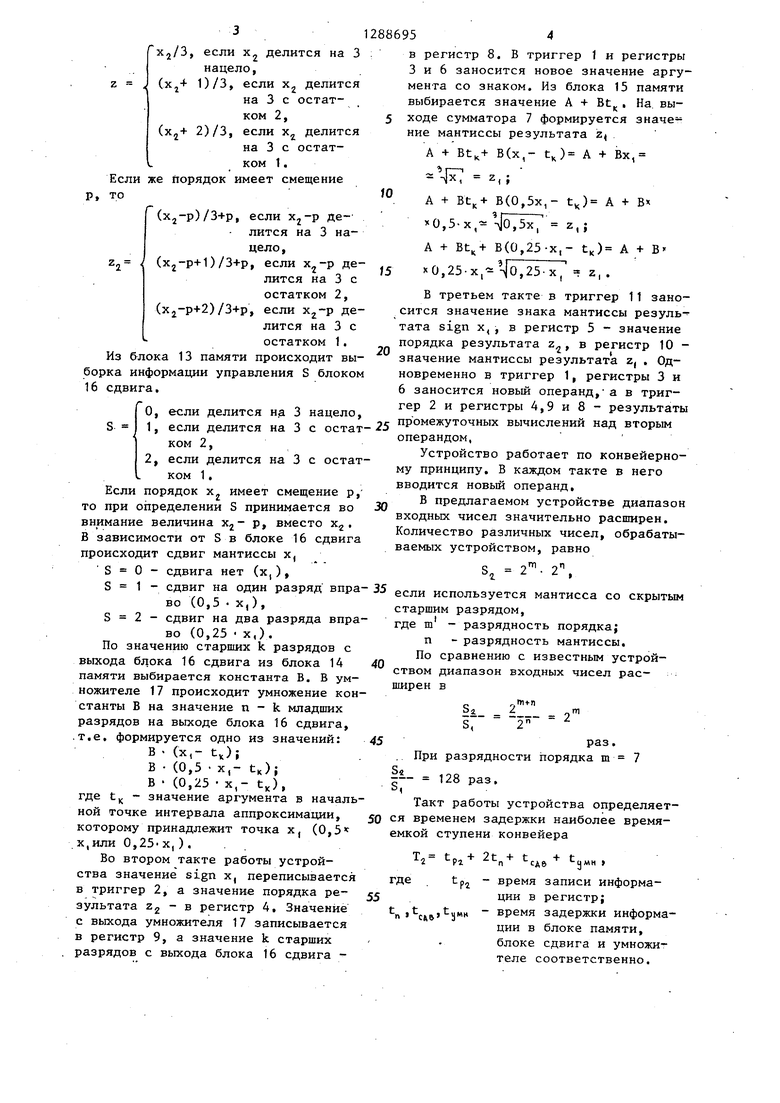

На чертеже представлена функциональная схема устройства.

Устройство содержит два триггера 1 и 2, четыре регистра 3-6, сумматор 7, пятый 8, шестой 9 и седьмой 10 регистры, третий 11 триггер, четыре блока 12-15 памяти, блок 16 сдвига и умножитель 17.

Устройство имеет вход 18 и выход 19 знака мантиссы, вход 20 и выход 21 порядка, вход 22 и выход 23 мантиссы и вход 24 синхронизации.

Блок сдвига легко построить при помощи селекторов-мультиплексоров.

Вычисление функции у |2Г произ- в одится на основе следующего алго- ; ритма. Аргумент х в формате с плаващей запятой представляется следующи образом;

9 X 2 ,

где X. - мантисса аргумента (0,5

х,1);

- порядок аргумента (х, - целое число).

у - ,.2

Хг/З

Так как величина Х2/3 не всегда является целой, то в необходимых слу- ,чаях производится сдвиг мантиссы вправо с прибавлением необходимого количества единиц к порядку аргумента.

1о,25-х, - i

.(

51. „Xi/Э

, / , если делится на 3

нацело,

у 4о,5-х7 , если делится

на 3 с остатком 2,

если делится на 3 с остатком 1.

Формирование подкоренного выражения производится при помощи блока 16 сдвига. В зависимости от значения порядка аргумента х из блока 13 памяти считывается управляющая информа- ция и в блоке 16 сдвига производится сдвиг аргумента на один или два раз- ряда вправо или значение аргумента передается на выход блока 16 сдвига без изменений.

Вычисление,мантиссы результата 2, ijt (0.125 ; t 1) производится на основе метода сегментной аппроксимации выражением у А + B z, где константы А и В выбираются из условия минимизации абсолютной погрешности.

Диапазон изменения аргумента (0,125 : t ; 1) разбивается на интервалы, количество которых определяется требуемой точностью, причем границы интервалов определяются k старшими разрядами мантиссы аргу--. мента .

На разных интервалах константы А и В имеют различные значения. В

блоке 14 памяти хранятся значения В, а в блоке 15 памяти - значения А+ВЦ, где t - значения начальной точки.

Устройство работает следующим образом.

В первом такте работы устройства в триггер 1 заносится значение знака мантиссы входного числа sign х,, в регистр 3 значение порядка входного числа х. В зависимости от значения

порядка х в блоке 12 памяти осуществляется определение порядка резуль- тата z. Если используется представление порядка без смещения, то

х./З,

э

если X,

делится на 3

(х.-ь

нацело,

Z J ( 1)/3, если х делится на 3 с остатком 2,

2)/3, если Xj, делится на 3 с остатком 1.

Если же порядок имеет смещение то

(х2-р)/3-«-р, если Xj,-p Де- - лится на 3 нацело,

(х -р+О/З+р, если делится на 3 с остатком 2,

(xj-p+2)/3+p, если делится на 3 с остатком 1,

Из &лока 13 памяти происходит выорка информации управления S блоком 6 сдвига.

2

S

если делится на 3 нацело, если делится на 3 с остат

О, 1,

ком 2, 2, если делится на 3 с остат

ком 1.

Если порядок х имеет смещение р,- то при определении S принимается во внимание величина Xj- р, вместо Xj. В зависимости от SB блоке 16 сдвига происходит сдвиг мантиссы х, сдвига нет (х,), сдвиг на один разряд впра

во (0,5 X,), сдвиг на два разряда впра

во (0,25 X,).

По значению старших k разрядов с выхода блока 16 сдвига из блока 14 памяти выбирается константа В. В умножителе 17 происходит умножение кон станты В на значение п - k младших разрядов на выходе блока 16 сдвига, .т.е. формируется одно из значений:

В В В

(х,- t (0,5

); - tJi

(0,25 X,- t).

где

t - значение аргумента в начальной точке интервала аппроксимации, которому принадлежит точка х, (0,5 х,или 0,25-X,). . .

Во втором такте работы устройства значение sign х, переписывается в триггер 2, а значение порядка результата Zg - в регистр 4. Значение с выхода умножителя 17 записывается в регистр 9, а значение k старших разрядов с выхода блока 16 сдвига 2886954

: В регистр 8. В триггер 1 и регистры 3 и 6 заносится новое значение аргумента со знаком. Из блока 15 памяти выбирается значение А Bt , На. вы- 5 ходе сумматора 7 формируется значе ние мантиссы результата z

А + В(х,- t) А + Вх,

NX, Z, ;

А + Btn+ В(0,5х,- t,) А + В (

,5-х,Мо,5х, Z,;

А + Bt,.+ В(0,25-х,- t) А + В

fO

15

0,25-х,,25-х, Z|.

20

В третьем такте в триггер 11 заносится значение знака мантиссы резуль тата sign х,, в регистр 5 - значение порядка результата z, в регистр 10 - значение мантиссы результата z, . Одновременно в триггер 1, регистры 3 и 6 заносится новый операнд, а в триггер 2 и регистры 4,9 и 8 - результаты 25 промежуточных вычислений над вторым операндом,

Устройство работает по конвейерному принципу. В каждом такте в него вводится новый операнд.

В предлагаемом устройстве диапазон входных чисел значительно расширен. Количество различных чисел, обрабатываемых устройством, равно

30

чЛП

35

40

если используется мантисса со скрытым

старшим разрядом,

где т - разрядность порядка;

п - разрядность мантиссы. По сравнению с известным устройством диапазон входных чисел рас- ширен в

§1 S,

2

45

раз,

При разрядности порядка m 7

84

- 128 раз. ч

Такт работы устройства определяет- 50 ся временем задержки наиболее время- емкой ступени конвейера

т -г

где

-Рг t

+ 2t + t.

+ t.

Pi

5

n c & -D

-n - -CA6

-время записи информации в регистр;

-время задержки информации в блоке памяти, блоке сдвига и умножи- теле соответственно.

При использовании микросхем серии 133, 556 и 1802 tp,j 35 не, не, 50 НС, t. 130 НС.

При I обработке 16-разрядных чисел быстродействие увеличено в 29 раз,

Фо рмула изобретения

Устройство для вычисления корня третьей степени, содержащее два триггера, четыре регистра и сумматор, отличающееся тем, что, с целью повьпиения быстродействия и расширения функциональных возможностей за счет обработки чисел в формате с плавающей запятой, устройство содержит пятый, шестой и седьмой регистры, третий триггер, четыре блока

памяти, блок сдвига и умножитель,

.причем информационный вход первого триггера соединен с входом знака мантиссы устройства, выход первого триггера соединен с информационным входом второго триггера, выход которого сое динен с информационным входом третьего триггера, выход которого является выходом знака мантиссы устройства, информационный вход первого регистра является входом порядка устройства, а выход первого регистра соединен с входами адреса первого и второго блоков памяти, выход первого блока памяти соединен с информационным входом второго регистра, выход которого

Редактор О.Головач Заказ 7809/47

Составитель Н.Захаревич

Техред В.Кадар Корректор В.Бутяга

Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раущская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

5

0 5

20

.25

035

соединен с информационным входом третьего регистра, выход которого соеди-- нен с выходом порядка устройства, выход второго блока памяти соединен с управляющим входом блока сдвига, информационный вход которого соединен с выходом четвертого регистра, информационный вход которого является входом мантиссы устройства, выход k старших разрядов блока сдвига (k log2 Р ; где Р - количество интервалов аппроксимации, - символ наименьшего целого не меньшего) соединен с входом адреса третьего блока памяти и с информационным входом пятого регистра, выход третьего блока памяти соединен с входом первого сомножителя умножителя, вход второго сомножителя которого соединен с выходом (п - k) младших разрядов блока сдвига (п - разрядность мантиссы операнда) , выход умножителя сое)а;инен с информационным входом шестого регистра, выход которого соединен с входом первого слагаемого сумматора, вход второго слагаемого которого соединен с выходом четвертого блока памяти, вход адреса которого соединен с выходом пятого регистра, выход сумматора соединен с информационным входом седьмого регистра, выход которого является выходом мантиссы устройства, входы синхронизации всех регистров и триггеров подключены к входу синхрониза- ции устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1985 |

|

SU1290308A1 |

| Устройство для вычисления корня | 1985 |

|

SU1339556A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Устройство для возведения в квадрат | 1986 |

|

SU1357953A2 |

| Устройство для вычисления функций | 1985 |

|

SU1297038A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления синуса | 1986 |

|

SU1319025A1 |

| Устройство для вычисления корня @ -степени | 1986 |

|

SU1381494A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления корня третьей степени в вычислительных машинах и устройствах с обработкой данных в формате с плавающей запятой. Целью изобретения является повышение быстродействия и расширение функциональных возможностей устройства за счет обработки данных в формате с плавающей запятой. Устройство содержит три триггера 1-3, семь регистров 3-6, 8-10, сумматор 7, четыре блока памяти 12-15, блок 16 сдвига и умножитель 17. На входы 20, 22, 18 подаются порядок, мантисса и знак мантиссы соответственно, на выходах 21,23,19 формируются значения I (Л г« .rs 00 о со ел

| Устройство для извлечения корня третьей степени | 1980 |

|

SU903869A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Белков М.С | |||

| и др | |||

| Разработка системы БИС для построения узлов ЦВМ | |||

| - Вопросы радиоэлектроники, Сер.ЭВТ, 1975, вып | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Уокерли Дж | |||

| Архитектура и программирование микро-ЭВМ | |||

| - М.: Мир, книга I, с | |||

| Раздвижной паровозный золотник с подвижными по его скалке поршнями между упорными шайбами | 1922 |

|

SU148A1 |

| Благовещенский Ю.В., Теслер Г.С | |||

| Вычисление элементарных функций на ЗВМ | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Устройство для вычисления кубического корня | 1980 |

|

SU1084786A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-07—Публикация

1985-07-08—Подача