Изобретение относится к вычислительной технике, в частности к организации условных переходов, и может быть использовано в цифровых вычисли тельных и управляющих машинах. Известно устройство, в котором при выполнении условного перехода адрес следующей команды формируется в зависимости от значений фиксированных разрядов числа, записанного в специальный регистр-аккумулятор 1 Недостатком этого устройства является повышенная сложность блока управления. Наиболее близким к предлагаемому изобретению по технической сущности является устройство, содержащее блок оперативной памяти, регистр адреса, арифметико-логический блок (АЛБ) и микропрограммный автомат (МПА) Г23 . Однако необходимость записи модификатора в оперативную память и использование для модификации АЛБ снижают быстродействие устройства и усложняют МПА. Цель изобретения - повьпиение быстродействия, а также упрощение устройства. Поставленная цель достигается тем, что в устройство управления последовательностью команд, содержащее €лок оперативной памяти, первая группа входов которого соединена с группой, информационных выходов АЛБ, группа входов кода операции которого соединена с группой выходов ксща операции блока оперативной памяти и группой входов кода операции МПА, группа выходов модифицированного адреса блока оперативной памяти соединена с группой входов модифицированного адреса АЛБ, группа адресных входов которого соединена с группой адресных выходов блока оперативной памяти и с группой входов блока элементов И, вход и группа выходов которого соединены соответственно с первым управлякх1шм выходом МПА и с группой адресных входов регистра адреса,группа разрядных выходов которого соединена со второй группой входов блока оперативной памяти, группа выходов МПА соединена с группой управляющих входов АЛБ, введен блок модификации, причем группа контрольных входов и группа входов модифицированного адреса бло- 10 модификации соединена соответстзенно с группой контрольных выходов АЛБ и с группойвыходов модифицированного адреса блока оперативной памяти, первый и второй управляющие входы блока модификации соединены соответственно с первым и вторым управляющими выходами МПА, группа выходов блока модификации соединена с группой контрольных входов регистра адреса.

Кроме того, блок модификации со дepжит два блока элементов И и. группу элементов ИЛИ, причем группы входов первого и второго блоков элементов И соединены соответственно с групами контрольных входов и входов модифицированйого адреса блока, входы первого и второго блоков элементов И соединены соответственно со вторым и первым управляющими входами блока, первые входы элементов ИЛИ группы соединены с соответствующими выходами первого блока элементов И, вторые входы элементов ИЛИ группы содинены с соответствующими выходами второго блока элементов И, выходы элементов ИЛИ группы соединены с группой выходов блока.

Кроме того, МПА содержит два.блока элементов И, регистр кода операции, блок, памяти микрокоманд, регист г.1икрокоманды, группу дешифраторов микрооперации и дешифратор, причем группа входов первого блока элементов И соединена с группой входов кода операции автомата, группа выходов ,и вход первого блока элементов И соединены соответственно с группой входов регистра кода операции и с первым выходом второго блока элементов И, группа разрядных выходов регистра кода операции соединена с первой группой входов блока памяти NMKрокоманд, вторая группа входов которого соединена с первой группой разрядных выходов регистра микрокоманды группы входов дешифраторов микроопераций группы соединены с соответствующими группами разрядных выходов регистра микрокоманды, группа.входов второго блока элементов И соединена с группами выходов дешифраторов микроопераций группы выход признака модификации регистра кода операции соединен с первым входом дешифратора, второй вход и выход которого соединены соответственно со вторым выходом второго блока элементов И и с вторым управляющим выходом автомата, выход блока памяти микрокоманд соединен со входом регистра микрокоманд, все выходы второго блока элементов И, кроме второго, соединены с группой выходов автомата, второй выход второго блока элементов И является первым управляющим выходом автомата. .

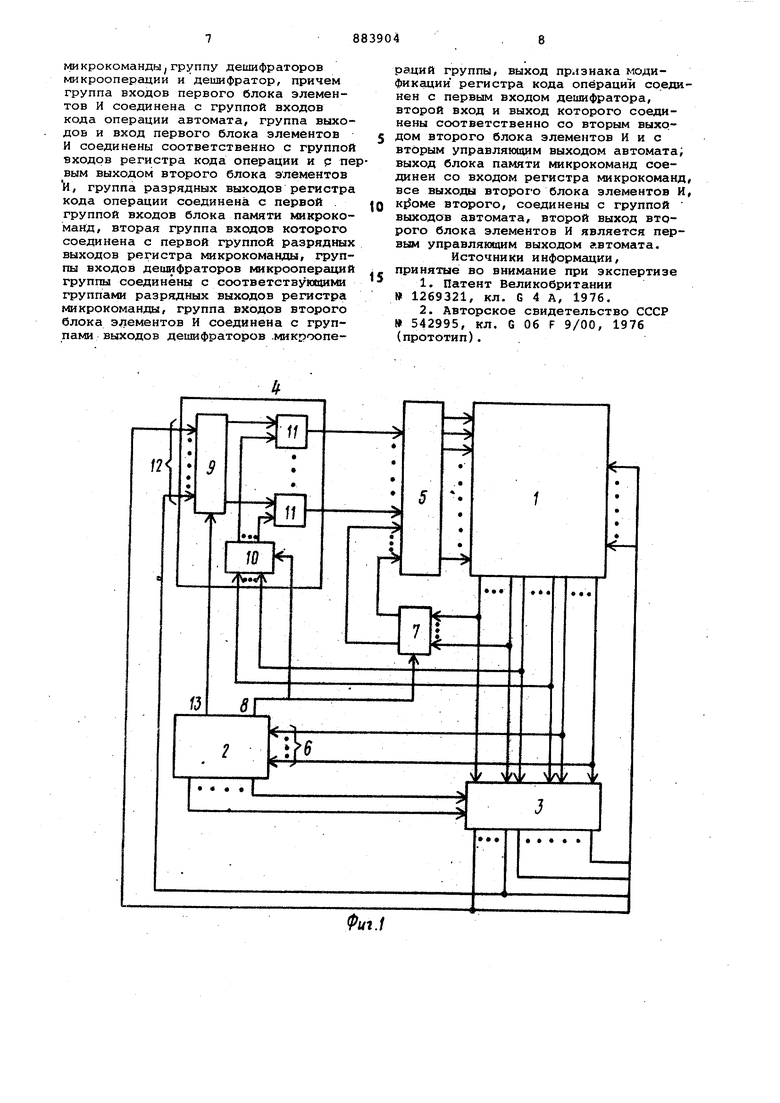

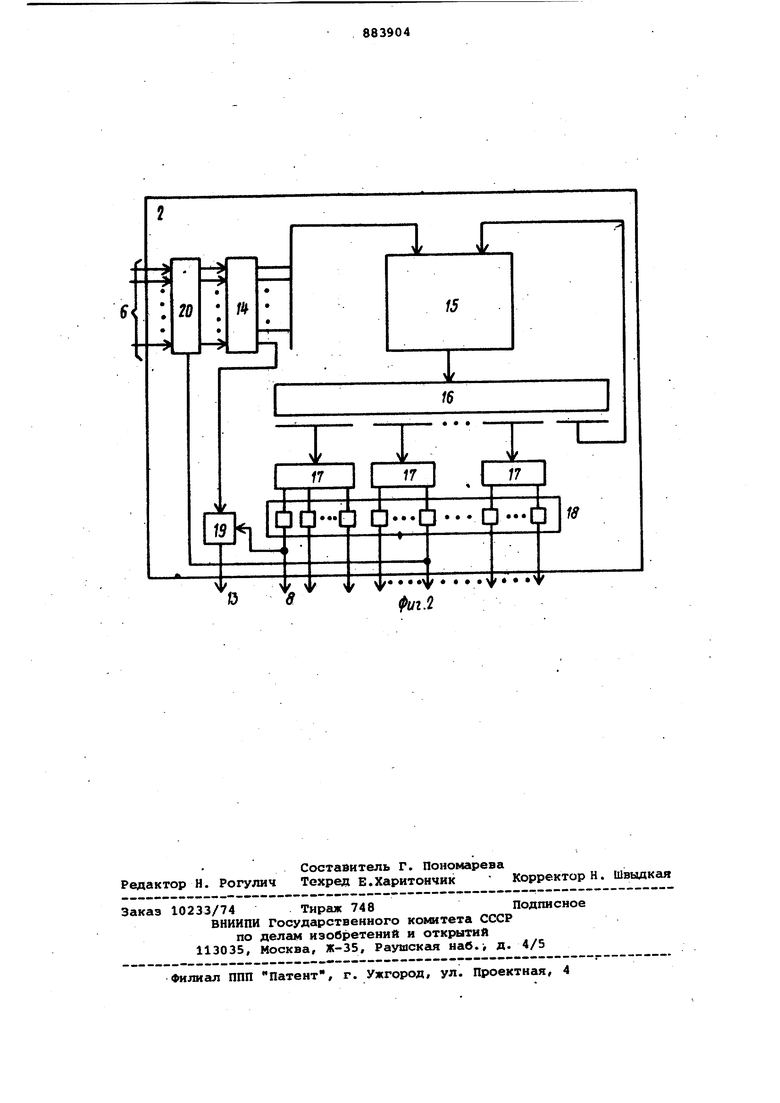

На фиг. 1 представлена блок -схема устройства для.случая принудительной

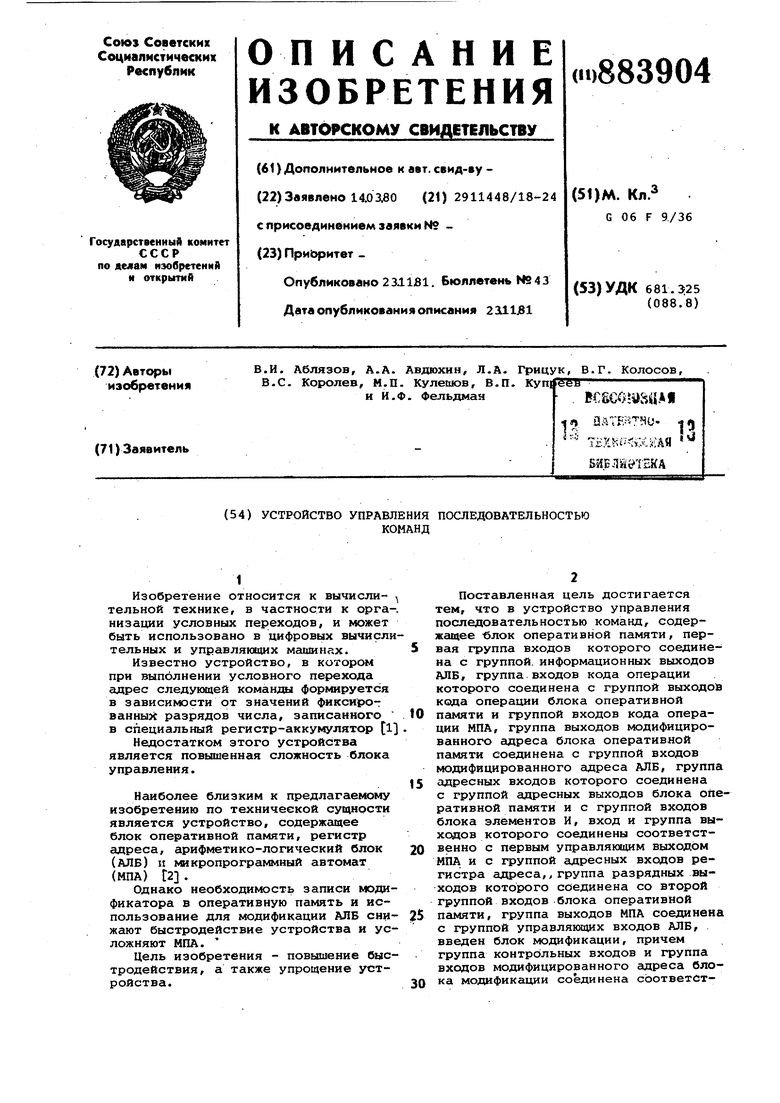

адресации; на фиг. 2 - блок-схема МПА.

Устройство содержит блок 1 оперативной памяти, МПА 2, АЛБ 3, блок 4 модификации и регистр 5 адреса, группу входов б кода операции МПА2, блок элементов .И 7, первый управляющий выход 8 МПА 2.

Блок 4 модификации содержит первый и второй блоки элементов И 9 и 1О, группу элементов ИЛИ 11, группу контрольных входов 12 и второй управлякяций выход 13,

МПА содержит регистр 14 кода операции, блок 15 памяти микрокоманд, регистр 16 микрокоманды, группу дешифраторов 17 микрооперации второй блок элементов И 18, дешифратор 19, первый блок элементов И 20.

Устройство работает следующим образом.

Работа устройства при выполнении команды происходит в течение трех фаз: выборка команды, ее выполнение и формирование адреса следующей команды. При этом во время выполнения команды адрес перехода хранится в блоке 1, куда он заносится во время первой фазы выполнения команды.

При считывании команды из блока 1 код операции по входам б поступает в МПА 2, где через открытый в этом такте блок элементов И 20 записывается на регистр 14. В дальнейшем МПА реализует управление выполнением данной операции, обеспечивая выдачу управляющих сигналов на свои выходные шины. Код операции интерпретируется, как адрес первой микрокоманды микропрограммы. Под управлением МПА в АЛБ 3 из блока 1 передаются операнды, где они подвергаются логической обработке. Результат выполнения команды появляется на выходных шинах АЛБ 3. Если дальнейшее выполнение программы зависит от результата выполнения данной команды, признаковый разряд кода операЭто значение

ции имеет значение

в течение времени выполнения команды присутствует на одном выходе дешифратора 19.

В заключительной фазе выполнения команды производится считывание адреса перехода из блока 1 с одновременным возбуждением управлякицего выхода 8. Это приводит к отпиранию по управляющим входам блоков элементов И 7 и 10. Часть разрядов адреса перехода записываются в регистр 5 непосредственно с выходов блока элементов И 7, а остальные разряды, значение которых может быть модифицировано, поступают на входы регистра 5 с выходов блока элементов И 10 через группу элементов ИЛИ 11. Одновременно с возбуждением выхода 8 возбуждается управляющий выход 13 (при выборке адреса перехода). Сигналом по выходу 13 открывается по управляющим входам блок элементов И 9. Контрольные разряды, выполняющие роль модификаторов, с выходов АЛБ 3 поступают на группу входов 12 открытого в данный момент блока элементов И 9 и далее с выходов последнего через группу элементов ИЛИ 1 на входы регистра 5. Вследствие это|го содержимое каждого из разрядов второй группы разрядов регистра 5 равно поразрядной логической сумме контрольных разрядов результата и соответствумщих разрядов адреса перехода.

Таким образом, появляется возможность организации условных переходов без введения специальной команды, причем на модификацию адреса перехода не затрачивается время (кроме задержки на элементах ИЛИ). В качестве контрольных могут служить любые разряды, в частности знаковый и младший.

Связь между выходами АЛБ и адресными входами блока оперативной памяти через блок модификации, содержащий элементы, выполняювдге поразрядную дизъюнкцию, позволяет модифицировать адрес перехода контрольными разрядс1ми результата. За счет этого появляется возможность организации условного перехода по результату выполнения любой команды без затрат времени. Таким образом повышается быстродействие устройства. Применени для реализации регистра адреса магнитных элементов с ППГ (например, магнитных переключателей или магнитно-полупроводниковых формирователей тока) позволяет выполнять операцию дизъюнкции разрядов адреса и контролных разрядов непосредственно на элементах регистра ащзеса, что предельно упрощает блок 1«эдификации. Отсутствие специальной команды условного перехода позволяет упростить МПА за .счет исключения соответствующих микропрограмм и сэкономить оперативную память.

Таким образом, возможно выполнени условного перехода в любой команде, результат которой находится в АЛБ. Для этого в коде операции задается признак условного перехода,который вявляется МПА.

Предлагаемое устройство используют в цифровых управляющих и вычислительных машинах с принудительной адресацией команд, когда последняя содержит адрес перехода и в системе команд отсутствует команда безусловного перехода.

Формула изобретения

1. Устройство управления последовательностью команд, содержащее

блок оперативной памяти, пеовая группа входов которого соединена с группой информационных выходов арифметико-логического блока, группа входов кода операции которого соединена с группой выходов кода операции-: блока оперативной памяти и группой входов кода операции микропрограммного автомата, группа выходов модифицированного адреса блока оперативной памяти соединена с группой входов мо0дифицированного адреса арифметикологического блока, группа адресных входов которого соединена с группой адресных выходов блока оперативной пс1мяти и с группой входов блока эле5ментов И, вход и группа выходов которого соединены соответственно с -первым управляющим выходом микропрогрс1Ммного автомата и с группой адресных входов регистра адреса, группа раз0рядных выходов которого соединена со вторюй группой входов блока оперативной памяти, группа выходов микропрограммного автомата соединена с группой управляющих входов арифметико-логического блока, отличающе5еся тем, что, с целью повьваения быстродействия и упрощения устройства, оно содержит блок модификации, причем группа контрольных входов и группа входов модифицированного адре0са блока модификации соединена соответственно с группой контрольных вы ходов арифметико-логического блокаис группой выходов модифицированного адреса блока оперативной памяти, пер5вый и второй управляющие входы блока модификации соединены соответственно с первым и вторым управляющикм выходами микропрограммного автомата, группа выходов блока модификации сое0динена с группой контрольных входов регистра а дреса.

2.Устройство ПОП.1, отличающееся тем, что блок модификации содержит, два блока элементов И и группу элементов ИЛИ, причем

5 группы входов первого и второго блоков элементов И соединены соответственно с группами контрольных входов и входов модифицированного адреса блока, входы первого и второго

0 блоков элементов И соединены соответственно со вторым и первым управляющими входами блока, первые входы элементов ИЛИ группы соединены с соответствующиквс выходами первого

5 блрка элементов И, вторые входы элементов ИЛИ группы соединены с соответствующими йыходами второго блока элементов И, вйходы- элементов ИЛИ группы соеди нены с группой выходов

0 блока/.

3.Устройство по п. 1, отли чающееся тем, что микропрограммный автомат содерзхит два блока элементов И, регистр кода операции,

5 блок памяти микрокоманд, регистр

«1икрокоманды, группу дешифраторов микрооперации и дешифратор, причем группа входов первого блока элементов И соединена с группой входов кода операции автомата, группа выходов и вход первого блока элементов И соединены соответственно с группой входов регистра кода операции и р певым выходом второго блока элементов Ти, группа разрядных выходов регистра кода операции соединена с первой группой входов блока памяти микрокоманд, вторая группа входов которого соединена с первой группой разрядных выходов регистра микрокоманды, группы входов дешифраторов микроопераций групгал соединены с соответствуюгцими группами разрядных выходов регистра микрокоманды, группа входов второго блока элементов И соединена с группами выходов дешифраторов .микроопераций группы, выход признака модификации регистра кода операции соединен с первым входом дешифратора, второй вход и выход которого соединены соответственно со вторым выходом второго блока элементов И и с вторым управляющим выходом автомата; выход блока памяти микрокоманд соединен со входом регистра микрокоманд все выходы второго блока элементов И KjJoMe второго, соединены с группой выходов автомата, второй выход второго блока элементов И является первым управляющим выходом .втомата.

Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании 1269321, кл. G 4 А, 1976.

2.Авторское свидетельство СССР 542995, кл. G Об F 9/00, 1976 (прототип).

1L

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для выполнения математических операций | 1986 |

|

SU1381533A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство для программного управления | 1981 |

|

SU1016783A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1084793A1 |

f

20

6

I 17 I rjn J 17 I

йй-й bu

№jg

t f f

0

8

15

Iff

a

Авторы

Даты

1981-11-23—Публикация

1980-03-14—Подача