управляющим входом блока, а их вторые входы соединены с информационным входом блока, с информационным выходом которого соединены выходы второго и четвертого элементов И, с управляющим входом блока соединены вторые входы второго и четвертого элементов и.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Процессор с динамическим микро-пРОгРАММНыМ упРАВлЕНиЕМ | 1979 |

|

SU849223A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

1. УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее блок управления, блок оперативной памяти, регистр адреса кс «анды, регистр адреса данных и регистр адреса памяти, причем выход регистра адреса па.М;яти-Соединенс адресным входом блока оперативной памяти, выход которого через числовую магистраль соединен с информационными входами реглйтра адреса данных и блока управления, информационные выходы блока управления через числовую магистраль соедиг йены с информационными входами ре-, гистра адреса команды, выходу регистров адреса команды и адреса данных соединены соответственно с первьши и вторыми информационными входами регистра адреса памяти, с первого по пятый выходы блока управления соединены с управляющими входами регистра адреса команды, регистра адреса данных, блока оперативной памяти и первым и вторым управляквдими входами регистра адреса памяти, отличающееся тем, что, с целью упрощения и повьнирния быстродействия устройства, введены операционный блок и шифратор, выход которого соединен с третьим информационным входом регистра адреса памяти, вход шифрато ра и третий управляющий вход регистра адреса памяти соединены с шестым выходом блока управления,информационный вход операционного блока через числовую магистраль соединен с выходами блока оперативной памяти, выход операционного блока: через числовую магистраль соединен с входом блока оперативной памяти и заходом блока управления, управляющий вход операционного блока соединен с седьмым выходсм блока управления. 2. Устройство по п.1, отличающееся тем, что операционный блок содержит п кана1лов, четыре элемента И, одвигатель и элемент НЕ, причем каждый канал состоит из регистра, четырех элементов И и элемента ИЛИ, первые входы первого и . j второго элементов И и элемента ИЛИ каждого канала соединены с соответ(Л ствувхцими выходами регистра, первый .и вторсй информационные входы которого соединены с выходами первого элемента И и эле /юнта ИЛИ своего канала, второй вход второго элементами каждо-5 го канала соединен с управляющим вхо.дом блока, а выход второго элемента И каждого канала соединен с управляющим входом блока, выход второго элемента и каждого канала - с выхоСП) дом блока, втсфые входы первого эл леита И и элемента ИЛИ каждого 00 оо канала сое;1этнены соответственно с выходами третьего и четвертого элементов И своего канала, первые входы которых соединены с информационным входом блока, вторые входы третьего и четвертого элементов И и вход установки в нуль регистра каждого канала соединены с управляющим входом блока, вход и выход сдвигателя соединены соответственно с выходом . пёрвЪго и первым входом второго элемента И, вход и выход элемента НВ соединены соответственно с выходами третьего и первым четвертого элементов И, первые входы первого и третьего эл 4енто$ И соединены с

Изобретение относится к вычислительной технике и может использоват ся в цифровых вычислительных и управляющих машинах, работающих по программе, хранящейся в оперативной памяти. Известно устройство содержащее арифметическо-логический блок, буферный регистр, блок хранения данных, блок управления, блок ввода и вывода и блок микропрограммного управления, происходит обработка да ных, содержащихся в .блоке хранения данных, буферном регистре или же поступаквдих с блока ввода и вывода. Для хран.ения промежуточных результа тов обработки используются буферный регистр и блок хранения данных. Выбор промежуточных результатов осуществляется отдельной командой, фор мируемой блоком микропрограммного управления f11. Наиболее близким по технической сущности к изо.бретению является уст ройство, содержащее блок управления, блок оперативной памяти, регистр адреса команды,регистр адреса данных и регистр адреса памяти С 2. В данном устройстве результат за письшается в память по адресу одног из операндов. При необходимости сох ранения операнда он пересылается в рабочую ячейку по специальной коман де, что удлиняет программу. Цель изобретения - упрощение уст ройства и повышение быстродействия. Указанная цель достигается за счет того, что в устройство для программного управления, содержащее блок управления, блок оперативной памяти, регистр адреса командам, регистр адреса данных и регистр адрес памяти, причем выход регистра адреса памяти соединен с ещресным входом блока оперативной памяти, выход которого через числовую магистраль соединен с информационными входс1ми регистра адреса данных и Олока управления, информационные выходы блока управления через числовую магистраль соединены с информационными входами регистра адреса команды, выходы регистров адресу команды и адреса данных соединены соответственно с первы ми и вторыми информационными входами регистра адреса памяти,с первого по пя тый выходы блока управления соединены с управляющими входами регистра адреса команды, perijtcTpa адреса данных, блока оперативной памяти и первым и вторым управляющими входами регистра адреса памяти, введены onejpaционный блок и шифратор, выход которого соединен с третьим информационным входом регистра адреса памяти, вход шифратора и третий управляющий вход регистра ещреса памяти соединены с шестым выходом блока управления, информационный вход операционного блока через числовую магистраль соединен с выходами блока оперативной памяти, выход операционного блока через числовую магистраль соединен с входом блока оперативной памяти и выходом -блока управления, управляющий вход операционного блока соединен с седьмым выходом блока управления. Кроме того, операционный блок содержит п каналов, четыре элемента И, сдвигатель и элемент НЕ, причем каждый канал состоит из регистра, четырех элементов И и элемента ИЛИ, первые входы первого и второго элементов И и элемента ИЛИ каждого канала соединены с соответствующими выходами регистра, первый и второй информационные входы которого соединены с выходами первого элемента И и элемента ИЛИ своего канала, нх.орой вход второго элемента И каждого канала соединен с управляющим входом блока, а выход второго элемента И каждого канала соединен с управляющим входом блока, выход второго элемента И каждого канала с выходом блока, вторые входы первого элемента и и элемента ИЛИ каждого канала соединены соответственно с выходами третьего и четвертого элементов И своего канала, первые входы которых соединены с информационным входом блока, вторые входы третьего и четвертого элементов И и вход установки в нуль регистра каждого канала соединены с управляющим входом блока, вход и выход сдвигателя соединены соответственно с выходом первого и первым входом второго элементов И, вход и выход элемента НЕ соединены соответственно с выходами третьего и первым входом четвертого элементов И, первые входы первого и третьего элементов И соединены с управляющим входом блока, а их вторые входы соединены с информациониь1м входом блока, с информационным выходом которого соединены также выходы второго и четвертого элементов И, с управляющим входом блока соединены вторые входы второго и четвертого элементов И.

Таким образом, появляется возмож.ность Записи результата, выраба- тываемого операционным блоком в фиксированную ячейку оперативной памяти без указания в выполняемой команде адреса фиксированной ячейки. Обращение к ней осуществляется обычным способом через регистр адреса, памяти, т.е. результат, записанный в фиксированную ячейку, может в дальнейшем использоваться любой командой основного формата.

В данном устройстве сокращаются объем и время выполнения программ, поскольку результат выполнения команды записывается в оперативную память, а операнды сохраняются без предварительного размножения.

В данном устройстве сокращается объем и время выполнения программ за счет исключения команд передачи результата из регистра в память и обратно.

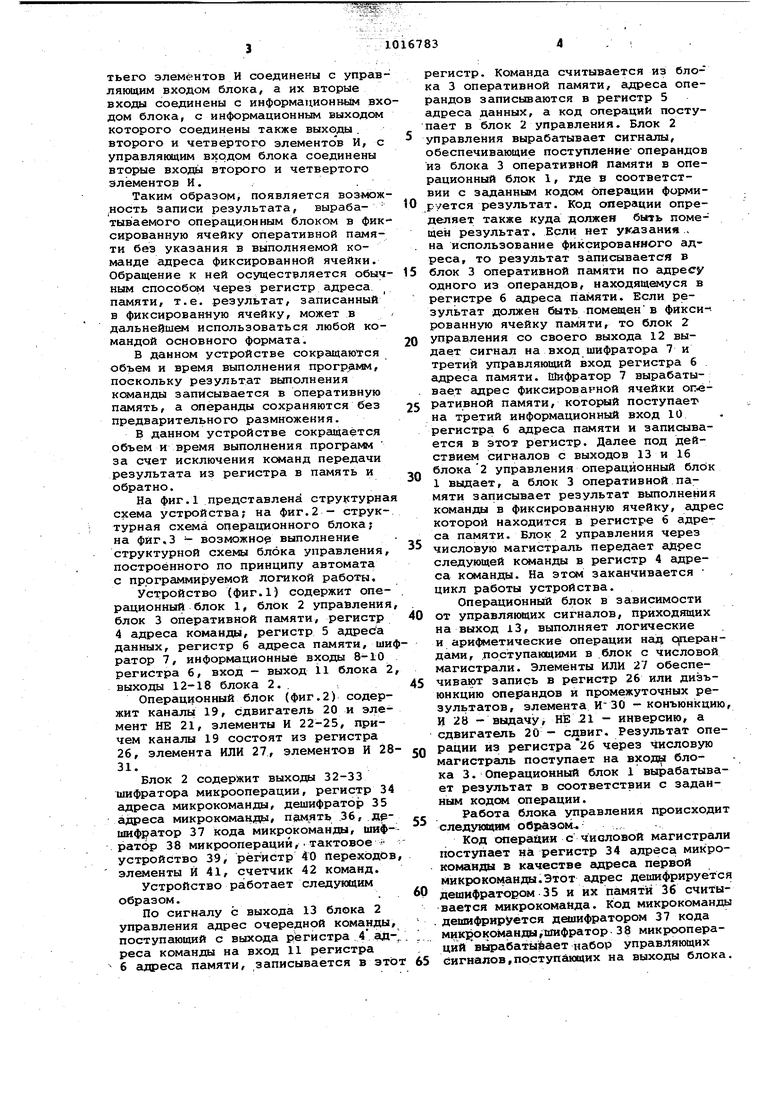

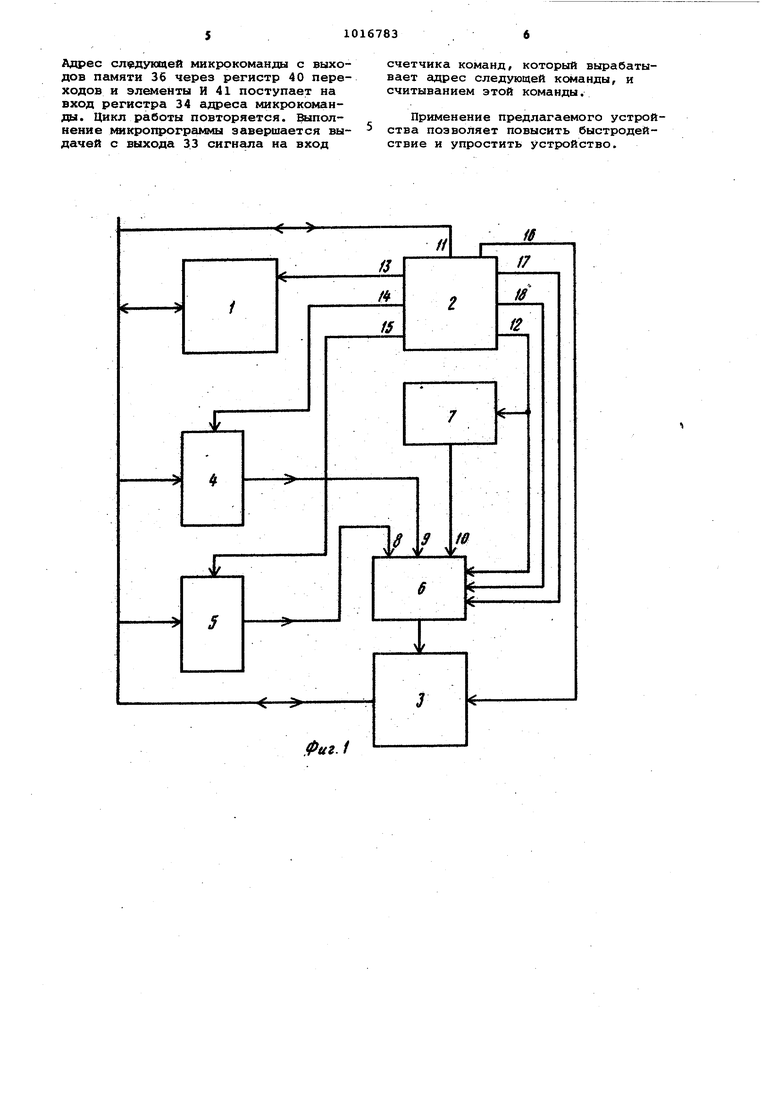

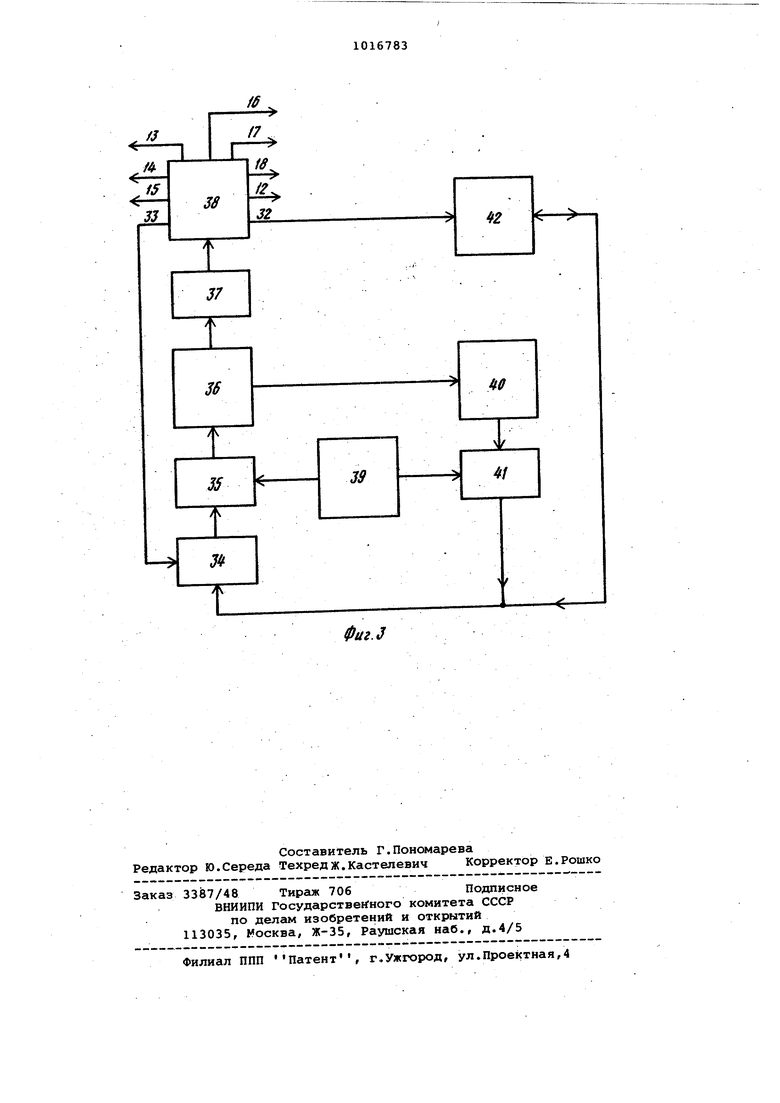

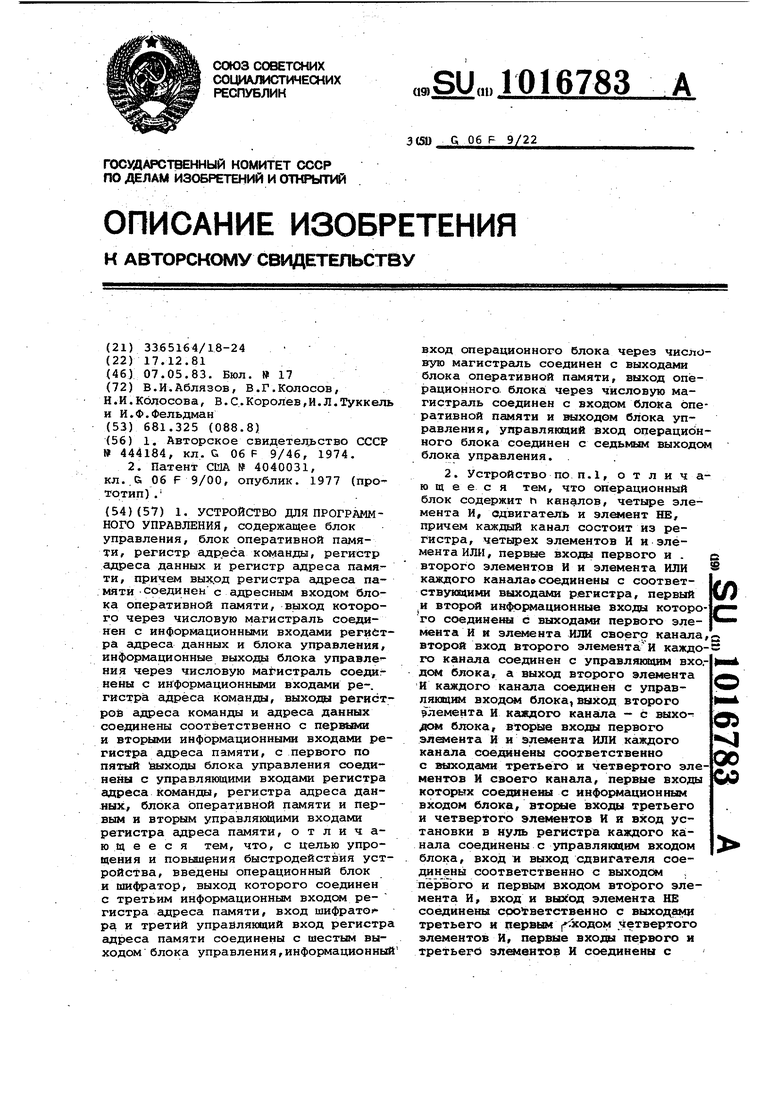

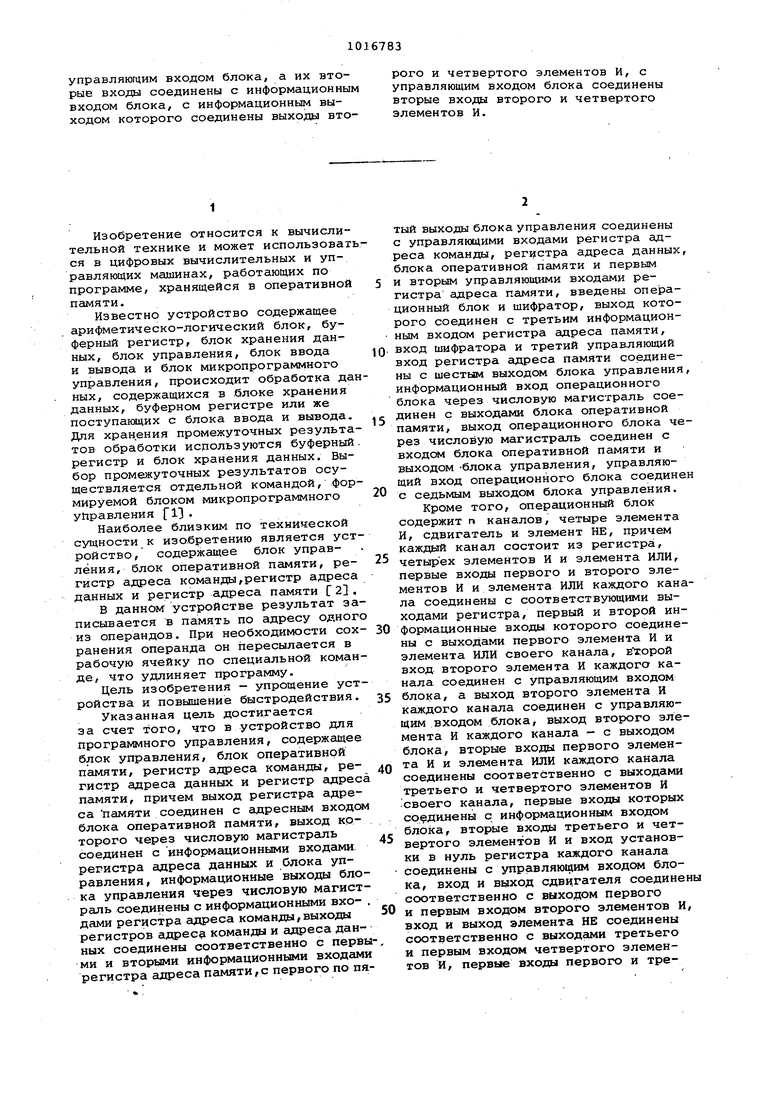

На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема операционного блока; на фйг.З возможно выполнение структурной схемы блока управления, построенного по принципу автомата с программируемой логикой работы.

Устройство (фиг.1) содержит one- . рационный блок 1, блок 2 упрайления, блок 3 оперативной памяти, регистр 4 адреса команды, регистр 5 адреса данных, регистр б адреса памяти, шифратор 7, информационные входы 8-10 регистра 6, вход - выход 11 блока 2, выходы 12-18 блока 2..

Операционный блок (фиг.2) содержит каналы 19, сдвигатель 20 и элемент НЕ 21, элементы И 22-25, причем каналы 19 состоят из регистра 26, элемента ИЛИ 27, элементов И 2831.

Блок 2 содержит выходы 32-33 шифратора микрооперации, регистр 34 адреса микрокоманды, дешифратор 35 адреса микрокоманды, память 36, дршифратор 37 кода микрокоманды, шиф-ратбр 38 микроопераций,Тактовое « устройство 39, 40 переходов, элементы И 41, счетчик 42 команд.

Устройство работает следующим образом.

По сигналу с выхода 13 блока 2 управления адрес очередной команды, поступающий с выхода регистра 4ад-/, реса команды на вход 11 регистра 6 ащреса памяти, записывается в этот

регистр. Команда считывается из блока 3 оперативной памяти, адреса операндов записываются в регистр 5 адреса данных, а код операций поступает в блок 2 управления. Блок 2 управления вырабатывает сигналы, обеспечивающие поступление операндов ив блока 3 оперативной памяти в операционный блок 1, где в соответствии с заданным кодом операции форми0руется результат. Код операции определяет также куда должен быть помещен результат. Если нет указания . на использование фиксированного адреса, то результат записывается в

5 блок 3 оперативной памяти по с1дресу одного из операндов, находящемуся в регистре 6 сщреса памяти. Если результат должен быть помещен в фикси-рованную ячейку Псмяти, то блок 2 управления со своего выхода 12 вы0дает сигнал на вход шифратора 7 и третий управляющий вход регистра 6 . адреса памяти. Шифратор 7 вырабатывает адрес фиксированной ячейки оп.еративной памяти, который поступает

5 на третий информационный вход 10 регистра 6 адреса памяти и записывается в этот регистр. Далее под действием сигналов с выходов 13 и 16 блока2 управления операционный блок

0 1 выдает, а блок 3 оперативной памяти записывает результат выполнения команды в фиксированную ячейку, адрес которой находится в регистре 6 адреса памяти. Блок 2 управления через

5 числовую магистраль передает адрес следующей команды в регистр 4 адреса команды. На этом заканчивается цикл работы устройства.

Операционный блок в зависимости

0 от управляющих сигналов, приходящих на выход 13, выполняет логические и арифметические операции над ргшрандами, .поступающими в блок с числовой магистрали. Элементы ИЛИ 27 обеспечивают запись в регистр 26 или дизъ5юнкцию операндов и промежуточных результатов, элемента И- 30 - конъюнкцию, И 28 - выдачу, НЕ .21 - инверсию, а сдвигатель 20 - сдвиг. Результат операции из регистра 26 через числовую

0 магистраль поступает на вход блока 3. Операционный блок 1 вырабатывает результат в соответствии с заданным кодом операции.

Работа блока управления происходит

5 следующим образом

Код onepaiftHH с числовой магистрали поступает на регистр 34 адреса микрокоманды в качестве адреса первой микрокоманды.Этот сщрес дешифрируется

0 дешифратором 35 и их памяти 36 считывается микрокоманда. Код микрокоманды . дешифрируется дешифратором 37 кода микрокоманды шифратор 38 микроопераций вырабатывает набор управляющих сигналов,поступающих на выходы блока.

5

Адрес сп пукпеЛ микрокоманды с выходов памяти 36 через регистр 40 переходов и элементы И 41 поступает на вход регистра 34 адреса микрокоманды. Цикл работы повторяется, исполнение кткропрограммы завершается выдачей с выхода 33 сигнала на вход

.иг. /

счетчика команд, который вырабатывает адрес следующей команды, и считыванием этой команды.

Применение предлагаемого устройства позволяет повысить быстродействие и упростить устройство.

16

//

//

iS

f2

«- е

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обработки информаций | 1971 |

|

SU444184A1 |

| С, 06 F 9/46, 1974 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4040031, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1983-05-07—Публикация

1981-12-17—Подача