.;I , Изобретение относится к области вы-числительной техники и может быть использовано для проверки на четкость или в декодирующих устройствах яла определения веса в кодовых комбинациях корре тирующих кодов, принимаемых в параллельТном коде. Известно устройство Для контроля (ДВОИЧНОГО кода на четность, содержащее информационные входы, соединенные че- pea элементы И и элемент ИЛИ со входом счетного триггера и управляемые распределителем l1. Недостаток этого устройства заключается в сравнитедьно низком быстродей ствии, определяемом тем, что тактовая частота распределителе должна в И раз (где и - длина информационного кода) .превышать тактовую частоту входной .информации. Наиболее близким техническим решением к изобретению является устройство для опрецеления четности информации, содержащее регистр, элементы И, элемент ИЛИ и триггер со счетным входом 2. Недостаток, его в том, что сигналы опроса состояния регистра проходят по сравнительно длинной цепочке последовательно соединенных элементов И, вносящих задержку, что снижает быстродейст- . вне устройства особенно при больших зна ченнях разрядности информационного кода и высокой тактовой частоте поступления информации. Действительно, при наличие I, например, только в последнем разряде регистра сигнал опроса дополнительно проходит ( И-1) последовательно вклю. чанных элементов И, а при наличии в предпоследнем разряде - (Vi-2) последовательно включенных элементов И и т.д. Поэтому общая дополнительная суммарная задержка прохождения сигналов только через логические элементы (без учета времени срабатывания триггеров) может составлять несколько тактов информационной частоты, что существенно снижает

быстродействие устройства, особенно при больших значениях Y ,

Цель изобретения - повышение быстродействия устройства.

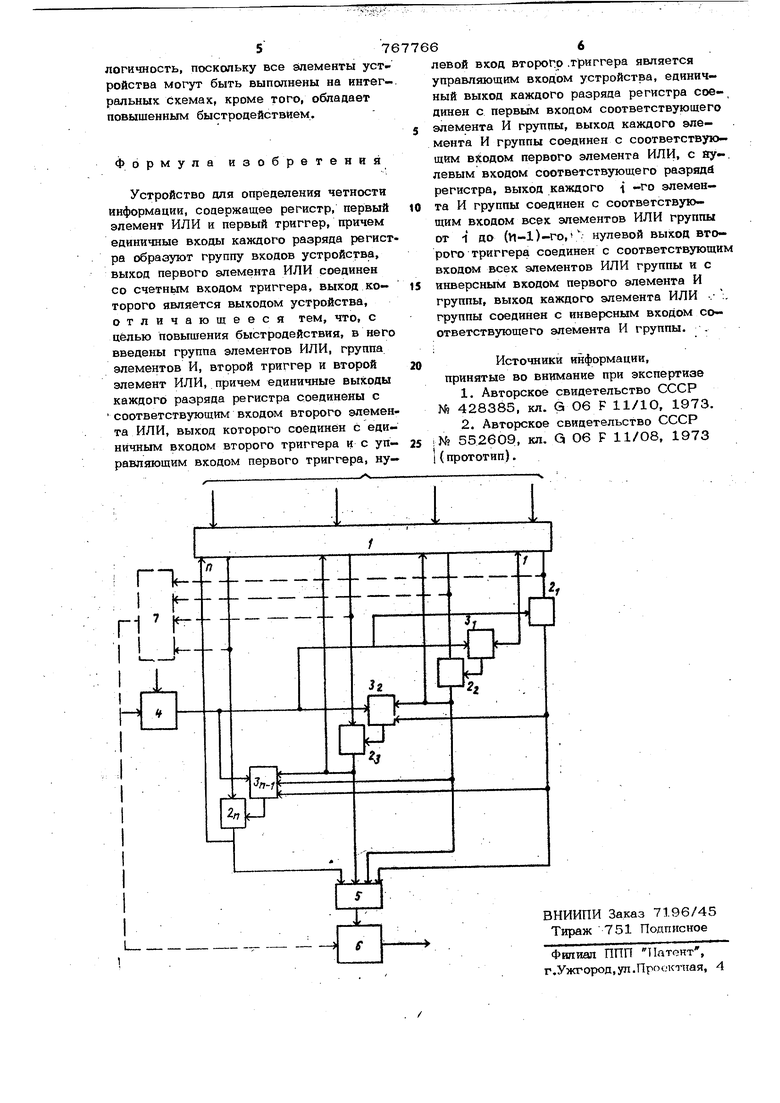

Указанная цель достигается тем, что в устройство для определения четности информации, содержащее регистр, первый элемент ИЛИ и первый триггер, причем единичные входы каждого разряда регистр образуют группу входов устройства, выкод первого элемента ИЛИ соединен со счетным входом триггера, выход которого является выходом устройства, введены группа элементов ИЛИ, группа элементов И, второй триггер и второй элемент ИЛИ При этом единичные выходы каждого разряда зегистра соединены с соответствующим входом второго элемента ИЛИ, выход которого связан с единичным входом второго тригг ера и с управляющим входом первого триггера. Нулевой вход второ(о триггера является управляющим входом устройства. Единичный выход каждого разряда регистра соединен с первым входом соответствующего элемента И группы выход каждого элемента И группы - с соответствующим входом первого элемента ИЛИ, с нулевым входом соответствую- щего разряда регистра, а выход каждого i -го элемента И группы - с соатветст- вующим входом всех элементов ИЛИ группы от i до (n-D-ro. Нулевой выход второго триггера соединен с соответствую- щим входом всех элементов ИЛИ группы и с инверсным входом первого элемента И группы, выход каждого элемента ИЛИ группы - с инверсным входом соответствующего элемента И г эуппы.

В результате этого существенно сокращается длина логических цепей опроса состояний разрядов регистра сдвига, что повышает быстродействие устройства.

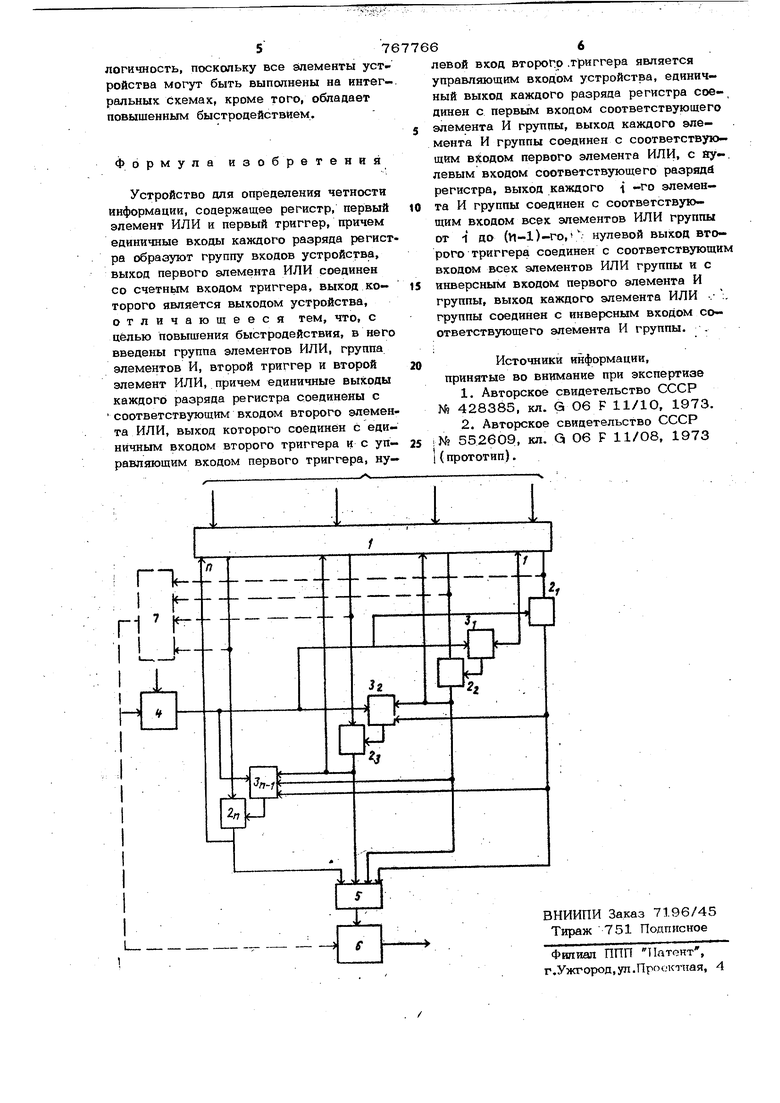

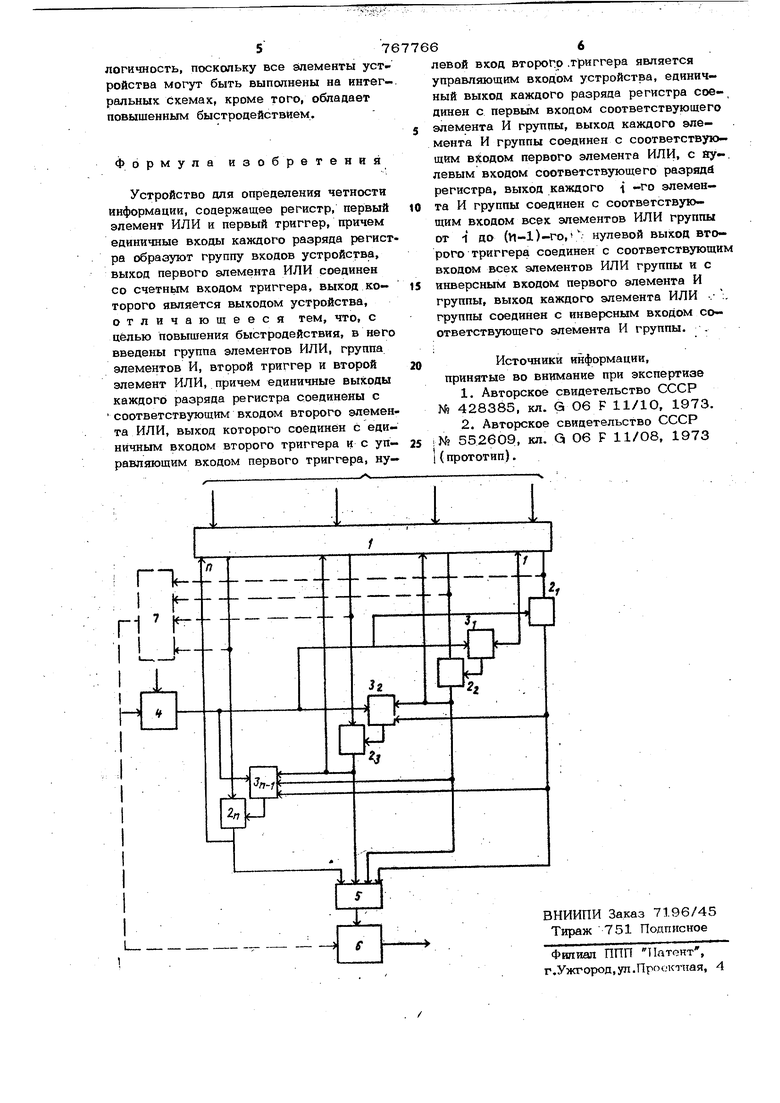

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит регистр 1 с вы- ходами разрядов, соединенных с группой элементов И 2 - 2 , к. инверсным входам которых подключены соответствующие элементы ИЛИ 3 - 3 ly.) , второй триггер 4, элемент ИЛИ 5, первый триггер 6, второй элемент ИЛИ 7, соединенный со входами установки триггеров 4 и 6.

Работает устройство следующим образом.

Входная двоичная информация поступает в н- разрядный регистр 1 в параллельном коде. После окончания записи информации второй триггер сигналом управляющего входа устройства переводится в

нулевое состояние, при котором через группу элементов ИЛИ 3 - снимаеся запрещающий потенциал на инверсных входах группы элементов И 2 ) - 2 j . Если в первом разряде регистра записана 1, то сигнал с выхода элемента 2 запрещает прохождение сигналов через элементы 2„- 2 более старших разрядов регистра и одновременно через первый элмент ИЛИ 5 поступает на вход первого триггера 6. Этот сигнал по цепи обрат. ной связи также осуществляет стирание i в первом разряде регистра.

В результате снижается запрет на последующем элементе И и, следовательно, обеспечивается возможность прохож-, дения сигнала со следующего разряда, где была записана 1.

В дальнейшем работа устройства осуществляется аналогичным образом. Для определения момента времени окончания работы устройства к регистру подключен второй элемент ИЛИ 7, срабатывающий при обнулении регистра 1. Появление нулевого сигнала на выходе элемента ИЛИ 7 дает возможность обеспечить считывание показаний триггера 6 и установку триггера 4 в исходное состояние. При необходимости устройство может быть использовано для определения числа единичных сигналов, например, в кодах постоянного веса. Для этого достаточно в устройство вместо триггера 6 включить обычный двоичный счетчик, фиксирующий заданный вес в анализируемых кодовых комбинациях.

Время, затрачиваемое на фиксацию каждой i на триггере 6, постоянно для всех разрядов регистра 1, так как длина цепи Для прохождения сигналов счета одинакова и минимальна. Это время в основном определяется быстродействием переключения триггеров ввиду того, что задержкой при прохождении с сигналов через логические элементы И и ИЛИ в данном случае можно пренебречь. При этом на анализ разрядов регистра с записанным О времени фактически не затрачивается. Поэтому время проверки информации на четность будет определяться только числом единиц, хранящихся в регистре, и не будет зависеть от его длины И , что позволяет повысить быстродействие устройства.

Устройство для определения четности информации, сохраняя все достоинства ;прототипа, такие как отсутствие синхровизируемых генераторов, высокая техноч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Устройство для определения четности информации | 1981 |

|

SU1019453A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля параллельного кода на четность | 1979 |

|

SU883910A1 |

| Устройство для определения количества единиц в двоичном числе | 1982 |

|

SU1084797A1 |

| Устройство для контроля двоичного кода на нечетность | 1981 |

|

SU1012261A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1363224A1 |

| Устройство для контроля параллельного кода на четность | 1983 |

|

SU1100626A1 |

Авторы

Даты

1980-09-30—Публикация

1978-10-13—Подача