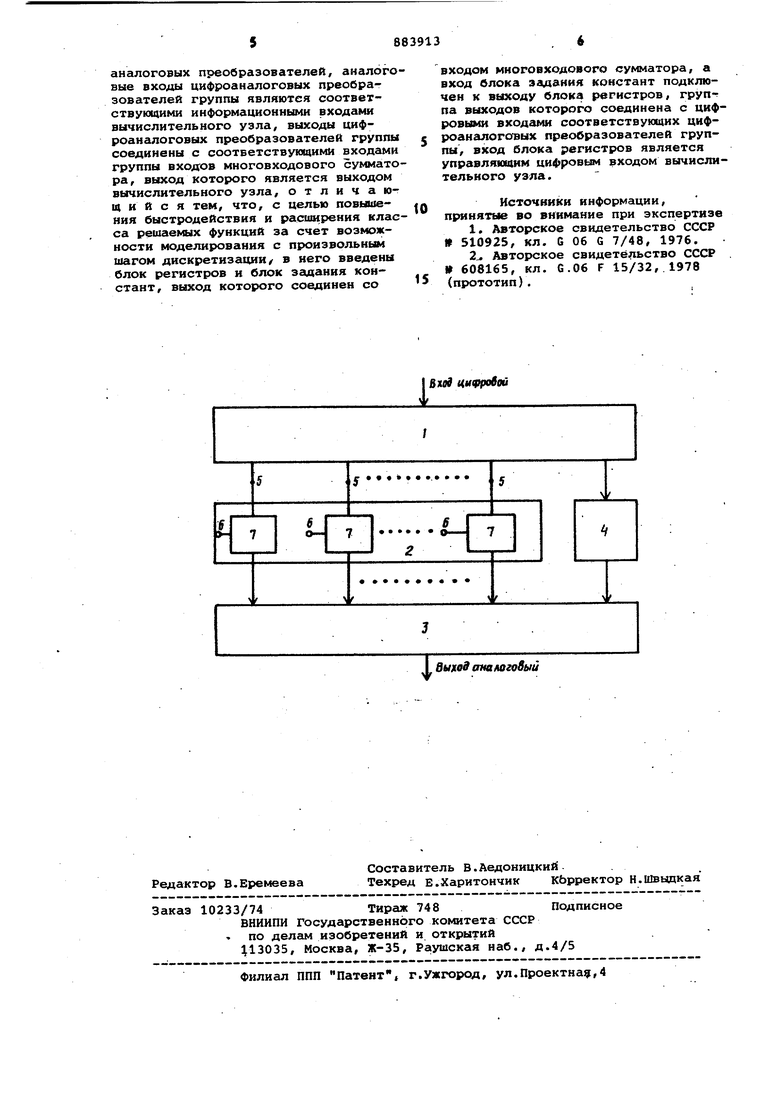

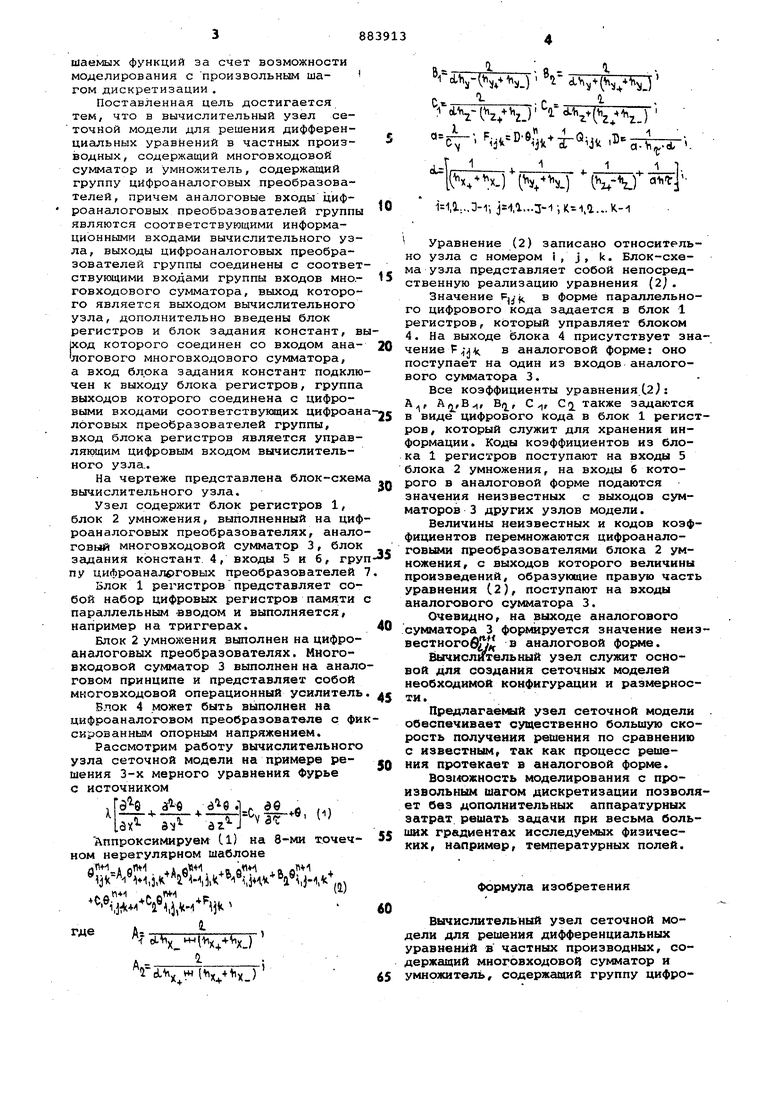

шаемых функций за счет возможности моделирования с произвольным ша- гом дискретизации , Поставленная цель достигается тем, что в вычислительный узел сеточной модели для решения дифференциальных уравнений в частных производных, содержащий многовходовой сумматор и умножитель, содержащий группу цйфроаналоговых преобразователей, причем аналоговые входы цифроаналоговых преобразователей группы являются соответствующими информационными входами вычислительного узла, выходы цифроаналоговых преобразователей группы соединены с соответ ствующими входами группы входов мно,говходового сумматора, выход которого является выходом вычислительного узла, дополнительно введены блок регистров и блок згщания констант, в |ход которого соединен со входом аналогового многовходового сумматора, а вход блока зещания констант подклю чен к выходу блока регистров, группа выходов которого соединена с цифровыми входами соответствукяцих цифроан лбгсвых преобразователей группы, вход блока регистров является управляющим цифровым входом вычислительного узла.. На чертеже представлена блок-схем вычислительного узла. Узел содержит блок регистров 1, блок 2 умножения, выполненный на циф роаналоговых преобразователях, анало говый многовходовой сумматор 3, блок задания констант 4, входы 5 и 6, гру пу цифроанал)говых преобразователей БЛОК 1 регистров представляет собой набор цифровых регистров памяти параллельным вводом и выполняется, например на триггерах. Блок 2 умножения вьтолнен на цифроаналоговых преобразователях. Многовходовой сумматор 3 выполнен на анало говом принципе и представляет собой многовходовой операционный усилитель Блок 4 может быть выполнен на цифроаналоговом преобразователе с фи сированным опорным напряжением. Рассмотрим работу вычислительного узла сеточной модели на примере решения 3-х мерного уравнения Фурье с источником ГаЧ.а. .аа9.Ц||,, ,, Аппроксимируем CD на 8-ми точечном нерегулярном шаблоне ,4+ I om-l ,л й«+1 ,а .в iii-Vw,j/4«HiA v;;i:,.,,, ...( f, -W .i,j., ) Q. TcL (N y ) 4. - iMVVj ) с. ..г- 1 oLV zJ .) 57- srbdTV .(TV) (N/V) IVVf ,a,,.:-r, j-iA-.-j-i .к-ч - Уравнение (2) записано относительно узла с номером i, j, k. Блок-схема узла представляет собой непосредственную реализацию уравнения (2) . Значение Pjjj. в форме параллельного цифрового кода задается в блок 1 регистров, который управляет блоком 4. На выходе блока 4 присутствует значение в аналоговой форме: оно поступает на один из входов аналогового сумматора 3. Все коэффициенты уравненияС2 : А, А,В, B/I, С , С0 также задаются в виде цифрового кода в блок 1 регистров , который служит для хранения информации. Коды коэффициентов из блока 1 регистров поступают на входы 5 блока 2 умножения, на входы б которого в аналоговой форме подаются значения неизвестных с выходов сумматоров 3 других узлов модели. Величины неизвестных и кодов коэффициентов пере шожаются цифроаналоговыми преобразователями блока 2 умножения, с выходов которого величины произведений, образующие правую часть уравнения (2), поступают на входы аналогового сумматора 3. Очевидно, на выходе аналогового сумматора 3 формируется значение нензвестногоб/у аналоговой форме. Вычислительный узел служит основой для создания сеточных моделей необходимой конфигургщии и размерности. . Предлагаемый узел сеточной модели обеспечивает существенно большую скорость получения решения по сравнению с известным, так как процесс решения протекает в аналоговой форме. Воз14ожность моделирования с произвольным шагом дискретизации позволяет без дополнительных аппаратурных затрат решать задачи при весьма больших градиентах исследуемых физических, например, температурных полей. Формула изобретения Вычислительный узел сеточной модели для решения дифференциальных уравнений в частных производных, содержащий многовходовой сумматор и умножитель, содержащий группу цифроаналоговых преобразователей, аналоговые входы цифроаналоговых преобразователей группы являются соответствующими информационными входами вычислительного узла, выходы цифроаналоговых преобразователей группы соединены с соответствующими входами группы входов многовходового сумматора , выход которого является выходом вычислительного узла, отличающийся тем, что, с целью повышения быстродействия и расширения класса решаемых функций за счет возможности моделирования с произвольным шагом дискретизации/ в него введены блок регистров и блок задания констант, выход которого соединен со

входом многовходового сумматора, а вход блока задания констант подключен к выходу блока регистров, группа выходов которого соединена с цифровыми входами соответствующих цифроаналогавых преобразователей группы, вход блока регистров является управляющим цифровым входом вычислительного узла.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 510925, кл. G 06 G 7/48, 1976.

2 Авторское свидетельство СССР . 608165, кл. G.06 F 15/32, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел для решения уравнений теплопроводности | 1983 |

|

SU1112379A1 |

| Устройство для решения нелинейных дифференциальных уравнений теплопроводности | 1983 |

|

SU1151985A1 |

| Вычислительный узел сеточной модели для решения нелинейных уравнений теплопроводности | 1986 |

|

SU1388912A1 |

| Вычислительный узел сеточной модели для решения нелинейных уравнений теплопроводности | 1984 |

|

SU1229783A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Вычислительный узел гибридного сеточного процессора для решения нелинейных задач теории поля | 1988 |

|

SU1635202A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

ВтЛ цм рровай

1

I выю9 аналоговый

Авторы

Даты

1981-11-23—Публикация

1980-03-20—Подача