динен со входом дешифратора, первый выход которого подключен ко входу блока управления, второй выход которого соединен с третьим входом блока долговременной памяти, второй выход которого подключен к первому входу коммутатора, второй вход которого соединен с третьим -выходом блока управления, третий вход коммутатора подключен ко второму выходу дешифра тора, третий выход которого соединен с первым входом блока памяти, второй вход которого подключен к выходу первого арифметического блока, первый вход которого соединен с первым выходом коммутатора, второй выхо которого подключен ко входу второго арифметического блока, выход которого соединен со вторым входом первог арифметического блока, выход блока памяти подключен ко входу регистратора результата. Кроме того, блок управления содержит первый и второй аналогоцифровые преобразователи, выходы которых соединены с выходами переключателя, .первого, второго одновибраторов и являются первым ВЕЛХОдом блока управления, пульт, первый выход которого соединен со входом первого одновибратора и с первым управляющим входом лентопротяжного механизма, второй управляющий вход которого подключен ко второму выходу пульта и связан со входом второго одновибратора, третий выход пульта подключен к первым входам первого и второго триггеров, выходы которых соединены соответственно с третьим и четвертым управлякядими входами лентопротяжного механизма, выход которого , подключен ко входу третьего одновибратора и является вторялм выходом блока управления, выходы первого и второго триггеров соединены с третьим выходом блока управления, выход . третьего одновибратора подключен к первым входам первого и второго элементов И, выходы которых соединены соответственно со вторыми входами первого и второго триггеров, вторые входы элеА4ентов И соединены и подключены ко входу блока управления. Кроме того, блок памяти содержит перйый и второй регистры, выходы которы подключены соответственно ко входам первого и второго дешифраторов выходы которых соединены со входами запоминающего устройства, выход которого подключен ко входу арифметического блока,выход которого является выходом блока памяти, входа первого и второго регистров подключены соответственно к первому и второму входам блока памяти.

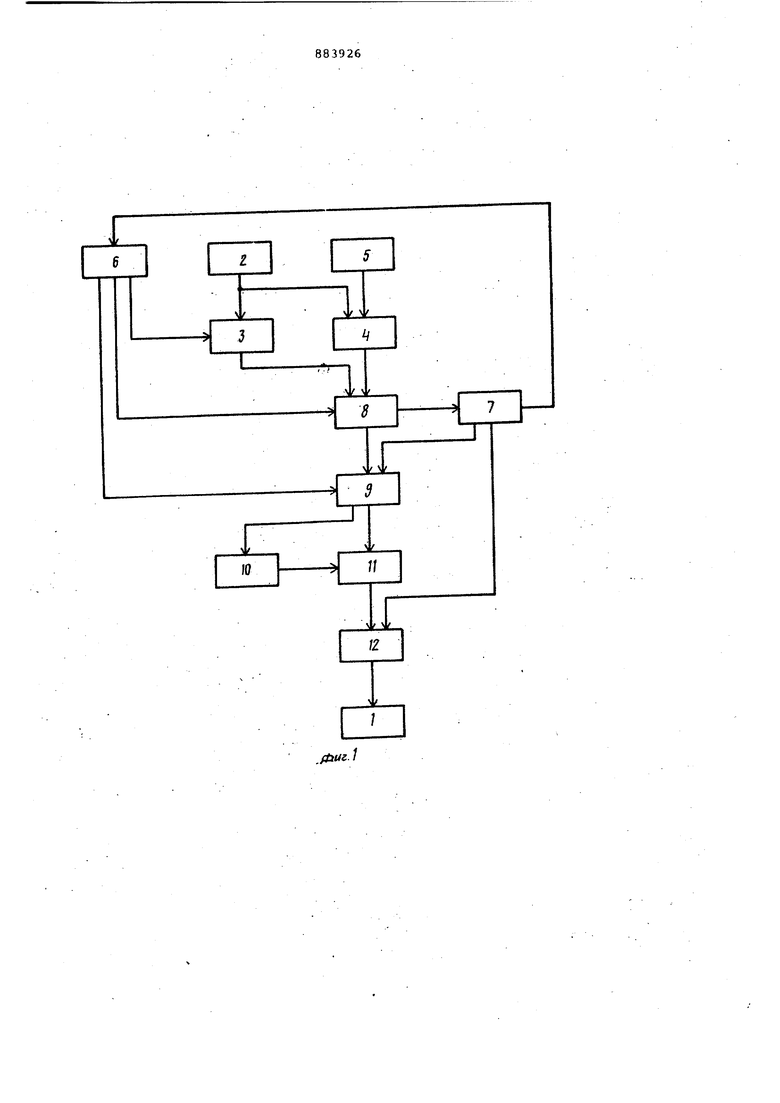

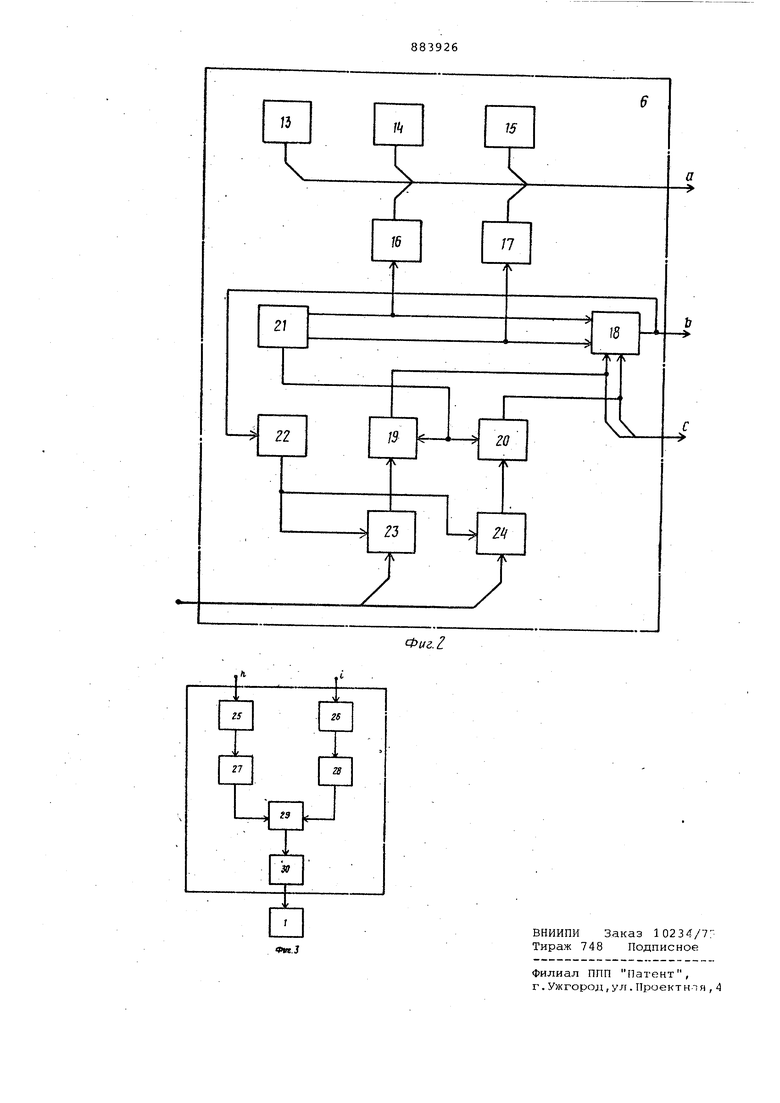

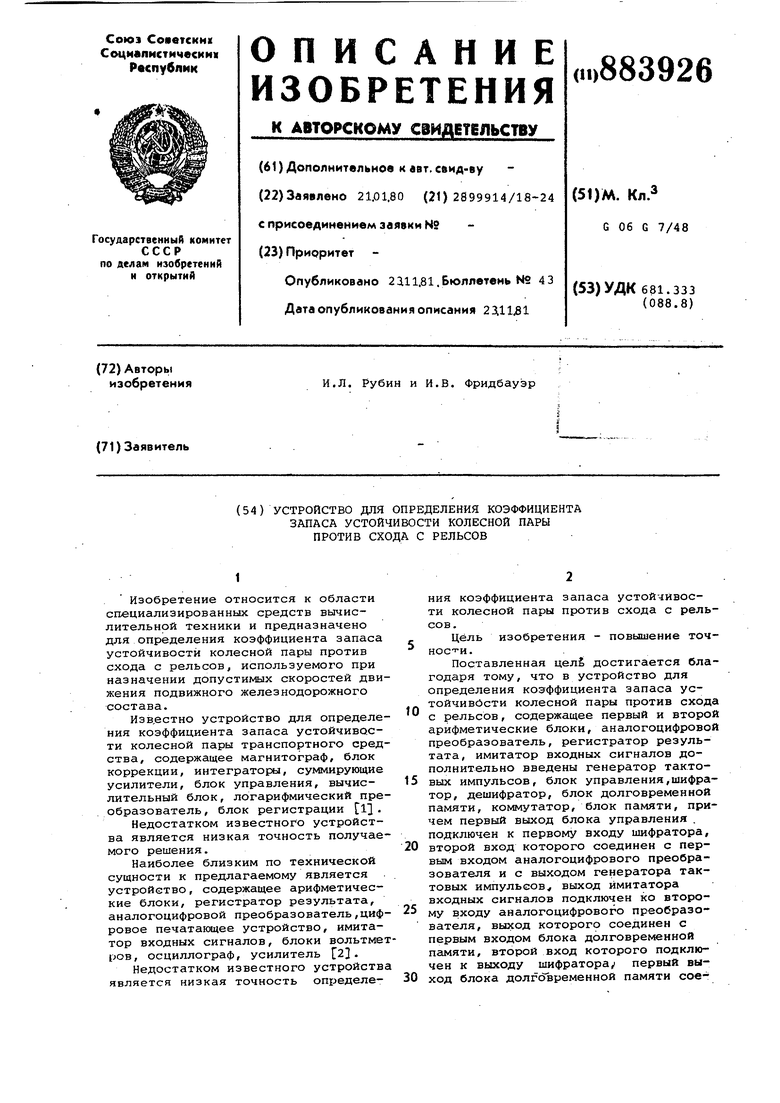

На фиг. 1 представлено предлагаемое устройство; на фиг. 2 - схема блока управления/ на фиг. 3 - то же, памяти.

Устройство содержит регистратор результатов 1, генератор тактовых импульсов 2, шифратор служебных признаков 3, аналогоцифровой преобразователь 4, имитатор входных сигналов 5, блок управления 6, дешифратор кодов служебных признаков 7, блок долговременной памяти 8, коммутатор 9, арифметические блоки 10 и 11,. блок памяти 12.

Блок управления 6 (фиг. 2) содержит аналогоцифровые преобразователи 13 и 14, переключатель 15, (кодов служебных признаков, одновибраторы 16 и 17, лентопротяжный механизм 18 триггеры 19 и 20, пульт(управления 21, одновибратор 22, элементы И 23 и 24.

Лентопротяжный механизм 18 работает в соответствии с таблицей.

Блок памяти 12 (фиг. 3) содержит регистры 25 и 26, дешифраторы 27 и 28, запоминающее устройство 29,арифметический блок 30.

Устройство.работает следующим образом.

В реж-име Запись блок долговременной памяти 8 запоминает значения кодов входных сигналов, поступающих с выхода аналогоцифрового преобразователя 4, и синхронно с ними значения кодов служебных признаков,поступающих с- выхода шифратора служебных признаков 3. Вычисление распределений мгновенных значений коэффициента устойчивости и сортировка реализаций по значениям служебных признаков реализуется в два этапа режима Воспроизведение блока долговременной памяти 8. На первом этапе коды мгновенных значений входных сигналов поступают с первого выхода коммутатора 9 на вход арифметического блока 10, реализующего функцию

+ пАп

d+i

П+-1

где ) - математическое ожидание массива из п (п+1) числа,

Хм -

текущее значение ла п(п+1)

количество чисел в массиве,

в том случае, если на втором выходе дешифратора кодов служебных признаков 7 присутствует сигнал, соответствующий движению исследуемого объекта по прямолинейному (стационарному) участку пути. Математическое ожидание входных сигналов, вычисленное на первом этапе, принима ется за нулевой уровень входных сигналов. .Первый этап заканчивается тогда, когда на первом выходе дешифратора кодов служебных признаков 7 появляется сигнал, соответствующий признаку Конец реализации, по которому блок уп равления 6 осуществляет для обрабаты ваемой реализации повторную выборку данных из блока долговременной памяти 8 и передачу их с помощью коммута тора 9 на первый вход арифметического блока 11 реализующего вычисления функции вида .« Ai(X,ytA,(X/;-x)4& (Ха-Х5)+(Х4-54) если (Х,,-Хз)ЧЧ-Ч)° Aa.( (, CtAM(X,,-X)+()tt-X4.KO I, - коэффициент устойчивости , АЛ - заданные численные коэффициенты, завися щие от парс метров ко лесной пары, Х .Xj, ,Х j, текущие коды, соответствующие мгновенным значениям вход ных сигналов, X,X-,Xj,X V- математические ожидания мгновенных значений входных сигналов В - коистанта, зависящая от пара- метров средства, и использующего .для вычисления мгновенных значений коэффициента устойчивости значение нулевого уровня входных сигналов и мгновенные значения входных сигналов. В продолжение второго этапа коды мгновенных, значений коэффициента устойчивости и соответствующие им коды служебных признаков воспринимаются блоком памяти 12 в качестве адреса ячейки памяти, содержимое которой увеличивается на единицу. Второй этап заканчивается тогда, когда на первом выходе дешифратора кодов служебных признаков 7 вновь появляется сигнал, соответствующий признаку Конец реализации, в соответствии с которым блок управления 6 осуществляет для следующей реализации выборку данных по первому этапу режима Воспроизведение блока долговременной памяти 8. В результате процесса обработки в блоке памяти 12 накапливаются распределения мгновенных значений коэффициентов устойчивости, причем Кс сдому коду служебньк признаков и, следовательно, каждой комбинации условий ходовых испытаний соответствует своя область памяти. Введение новых блоков и связей между ними позволяет повысить точность определения коэф| ициента запаса, устойчивости колесной пары против схода с рельсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения коэффициента запаса устойчивости колесной пары против схода с рельсов | 1983 |

|

SU1144125A1 |

| Устройство для ввода информации от датчиков | 1983 |

|

SU1134932A1 |

| Контролируемый пункт телемеханической системы | 1981 |

|

SU955157A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Измерительная информационная система контроля состояния окружающей среды | 1978 |

|

SU746667A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

| Устройство для лексического анализа метатранслятора | 1983 |

|

SU1153329A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

Формула изобретения Устройство для определения коэффициента запаса устойчивости колесной пары против схода с рельсов, содержгицее первый и второй арифметичес кие блоки, аналогоцифровой преобразователь, регистратор результата,ими татор входных сигналов, отличающееся тем, что, с целью повышения точности определения коэффициента запаса устойчивости, в устройство дополнительно введены генератор тактовых импульсов, блок управления, шифратор, дешифратор, блок долговременной памяти, коммутатор, блок памяти, причем первый выход блока управления подключен к первому входу шифратора, второй вход которого соединен с первым входом ангшогоцифрового преобразователя и с выходом -генератора тактовых импульсов, выход имитатора входных сигналов подключен ко второму входу аналргоцифрового преобразователя, выход которого соединен с первьт входом блока

долговременной памяти, второй вход которого подключен к выходу шифратора, первый выход блока долговременной памяти соединен со входом дешифратора, первый выход которого под-. ключен ко входу блока управления, второй выход которого соединен с третьим входом блока долговременной памяти, второй выход которого подключен к первому входу коммутатора,второй вход которого соединен с третьим выходом блока управления,третий вход коммутатора подключен к второму выходу дешифратора, третий выход которого соединен с первым входом блока памяти, второй вход которого подключен к выходу первого ариф- . метического блока, первый вход которого соединен с .первым выходом коммутатора, второй выход которого подключен ко входу второго арифметического блока, выход которого соединен со вторым входом первого арифметического блока, выход блока памяти подключен ко входу регистратора результата.

к первым входам первого н второго триггеров, выходы которых соединены соответственно с третим и четвертым управляющими входами лентопротяжного механизма, выход которого подключен ко входу третьего одновибратора и является вторым выходом блока управления, выходы первого и второго триггеров соединены с третьим выходом блока управления, выход третьего одновибратора подключен к первым входам первого и второго элементов И, выходы которых соединены соответственно со вторыми входами первого и второго триггеров, вторые входы элементов И соединены и подключены ко входу блока управления.

Источники информации, принятые во внимание при экспертизе

./fti/e. /

Авторы

Даты

1981-11-23—Публикация

1980-01-21—Подача