Изобретение относится к запоминающим устройствам и может быть использовано в автоматизированных системах управления, контроля и обработки информации.

По основному авт. св. № 590825 известен шифратор, содержащий ячейки памяти , выходы которых подключены к первому входу соответствующих элементов считывания, вторые входы которых подключены к шине разрешения считывания, формирователи сигналов сброса, выходы которых подключены к входэм соответствующих ячеек памяти, дешифратор, формирователи входных сигналов, входы которых подключены к выходам соответствующих элементов считывания, а выходы - к входам деШ1 ратора и входам соответствующих формирователей сигналов сброса, и ;элементы ИЛИ,первые входы которых соединены с выходами соответствующих ячеек памяти, кроме первой, второй вход первого элемента ИЛИ соединен с выходом первой ячейки памяти и с третьим входом последующего элемента считывания, а выходы всех элементов ИЛИ соединены с вторыми входами последуюгцих элементов ИЛИ и с третьими

входами последующих элементов считывания l .

При использовании этого шифратора в устройствах автоматизированных систем управления, контроля и обработки информации не достоверно контролируется информация, поступающая на вход шифратора в процессе работы в связи с тем, что при несоответствии прошлой

10 информации эталонным данным невозможно принять решение о том, вызвано ли ненормальное состояние сигналов на выходе шифратора неисправностью шифратора или неверно сформированной ин15формацией, поступающей на входы шифратора.

Указанные обстоятельства снижают надежность шифратора.

Цель изобретения - повышение на20дежности шифратора.

Поставленная цель достигается тем, что шифратор содержит триггер, элементы НЕ, две групы элементов И и дополнительные элементы ИЛИ, причем

25 вчоды триггера подключены к одним из ьходов шифратора,а выход триггера соединен с первыми входами элементов И первой группы и входом одного из элементов КЕ,выход которого подключен к

30

первым входам элементов И второй группы, вторые входы которых соединены с другими входами шифратора и входами других элементов НЕ, выходы которых подключены ко вторым входам элементов И второй группы, выходы элементов И подключены к входам дополнительных элементов ИЛИ, выходы которых соединены со входами ячеек памяти.

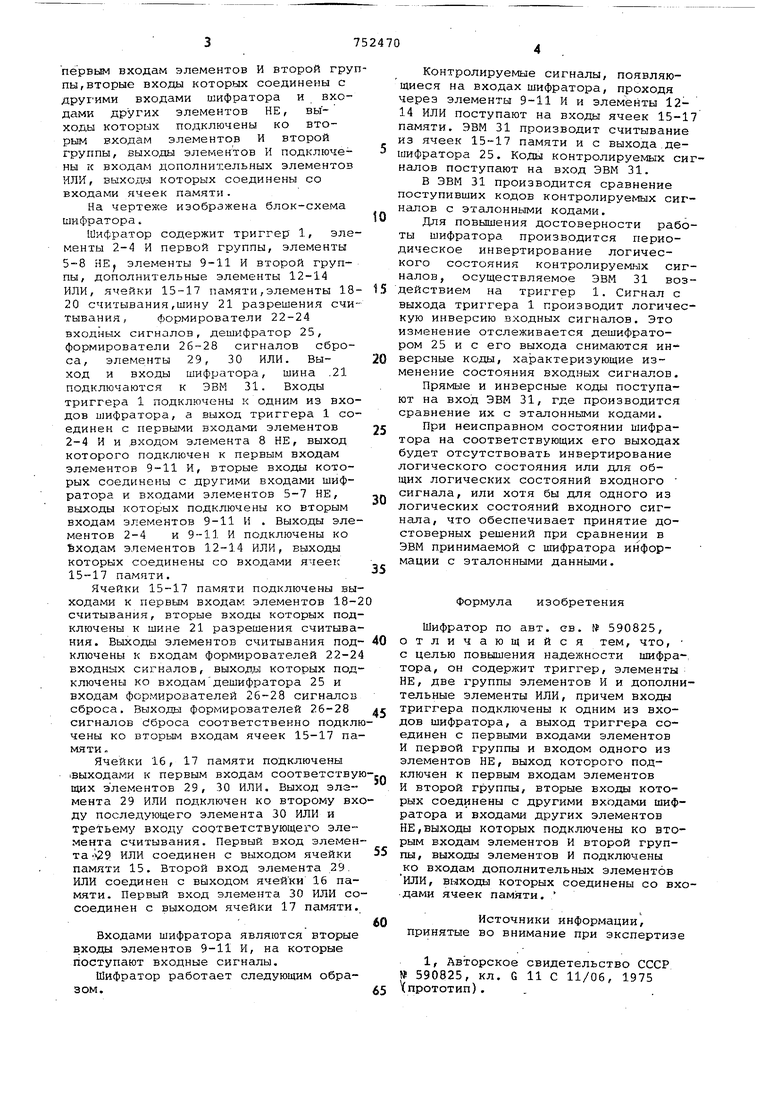

На чертеже изображена блок-схема шифратора.

Шифратор содержит триггер 1, элементы 2-4 И первой группы, элементы 5-8 НЕ, элементы 9-11 И второй группы, дополнительные элементы 12-14 ИЛИ, ячейки 15-17 памяти,элементы 1820 считывания,шину 21 разрешения считывания, формирователи 22-24 входных сигналов, дешифратор 25, формирователи 26-28 сигналов сброса, элементы 29, 30 ИЛИ. Выход и входы шифратора, шина .21 подключаются к ЭВМ 31. Входы триггера 1 подключены к одним из входов шифратора, а выход триггера 1 соединен с первыми входами элементов 2-4 И и входом элемента 8 НЕ, выход которого подключен к первым входам элементов 9-11 И, вторые входы которых соединены с другими входами шифратора и входами элементов 5-7 НЕ, выходы которых подключены ко вторым входам элементов 9-11 И . Выходы элементов 2-4 и 9-11 И подключены ко бходам элементов 12-14 ИЛИ, выходы которых соединены со входами ячеек 15-17 памяти..

Ячейки 15-17 памяти подключены выходами к первым входам элементов 18-2 считывания, вторые входы которых подключены к шине 21 разрешения считывания. Выходы элементов считывания подключены к входам формирователей 22-24 входных сигналов, выходы которых подключены ко входамдешифратора 25 и входам формирователей 26-28 сигналов сброса. Выходы формирователей 26-28 сигналов (Сброса соответственно подключены ко вторым входам ячеек 15-17 памяти.

Ячейки 16, 17 памяти подключены выходами к первым входам соответствую щих элементов 29, 30 ИЛИ. Выход элэмента 29 ИЛИ подключен ко второму вхду последующего элемента 30 ИЛИ и третьему входу соответствующего элемента считывания. Первый вход элемента ) ИЛИ соединен с выходом ячейки памяти 15. Второй вход элемента 29. ИЛИ соединен с выходом ячейки 16 памяти. Первый вход элемента 30 ИЛИ сосоединен с выходом ячейки 17 памяти.

Входами шифратора являются вторые входы элементов 9-11 И, на которые поступают входные сигналы.

Шифратор работает следующим образом.

Контролируемые сигналы, появляющиеся на входах шифратора, проходя через элементы 9-11 И и элементы 1214 ИЛИ поступают на входы ячеек 15-17 памяти. ЭВМ 31 производит считывание из ячеек 15-17 памяти и с выхода,дешифратора 25. Коды контролируемых сигналов поступают на вход ЭВМ 31.

В ЭВМ 31 производится сравнение поступивших кодов контролируемых сигналов с эталонными кодами.

Для повышения достоверности работы шифратора производится периодическое инвертирование логического состояния контролируемых сигналов, осуществляемое ЭВМ 31 воздействием на триггер 1. Сигнал с выхода триггера 1 производит логическую инверсию входных сигналов. Это изменение отслеживается дешифратором 25 и с его выхода снимаются инверсные коды, характеризующие изменение состояния входных сигналов.

Прямые и инверсные коды поступают на вход ЭВМ 31, где производится сравнение их с эталонными кодами.

При неисправном состоянии шифратора на соответствующих его выходах будет отсутствовать инвертирование логического состояния или для общих логических состояний входного сигнала, или хотя бы для одного из логических состояний входного сигнала, что обеспечивает принятие достоверных решений при сравнении в ЭВМ принимаемой с шифратора информации с эталонными данными.

Формула изобретения

Шифратор по авт. св. № 590825, отличающийся тем, что, с целью повышения надежности шифратора, он содержит триггер, элементы НЕ, две группы элементов И и дополнительные элементы ИЛИ, причем входы триггера подключены к одним из входов шифратора, а выход триггера соединен с первыми входами элементов И первой группы и входом одного из элементов НЕ, выход которого подключен к первым входам элементов И второй группы, вторые входы которых соединены с другими входами шифратора и входами других элементов НЕ,выходы которых подключены ко вторым входам элементов И второй группы, выходы элементов И подключены ко входам дополнительных элементов ИЛИ, выходы которых соединены со вхдами ячеек памяти.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР № 590825, кл. G 11 С 11/06, 1975 прототип).

I I I . 1 I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1981 |

|

SU1005187A2 |

| Шифратор | 1985 |

|

SU1298801A2 |

| Шифратор | 1985 |

|

SU1298802A2 |

| Шифратор | 1980 |

|

SU920835A1 |

| Шифратор | 1980 |

|

SU886048A2 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-31—Подача