(54) ШИФРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1985 |

|

SU1298801A2 |

| Шифратор | 1980 |

|

SU886048A2 |

| Шифратор | 1980 |

|

SU920835A1 |

| Шифратор | 1978 |

|

SU752470A2 |

| Шифратор | 1985 |

|

SU1298802A2 |

| ПРИБОР ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПАРАЗИТНЫХ ИМПУЛЬСНЫХ ВОЗМУЩЕНИЙ В СЕТЯХ ЭЛЕКТРОПИТАНИЯ С ПЕРЕМЕННЫМ НАПРЯЖЕНИЕМ | 2002 |

|

RU2239201C2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

Изобретение относится к запоминающим, устройствам и может быть использовано в автоматизированных.системах управления, контроля и обработки информации.

По основному авт.св. № 590825, известен шифратор, содержащий ячейки памяти, выходы которых подключены к первому входу соответствующих элементов считывания, вторые входы которых подключены к шине разрешения считывания, выходы элементов считывания соединены соответственно с входами формирователей входных сигналов, выходы которых подключены к дешифратору и вхоДам формирователей. сигналов сброса, выходы которых подключены к входам соответствующих ячеек памяти, и элементы ИЛИ, первые входы которых соединены с выходами соответствующих ячеек памяти, кроме первой, второй вход первого элемента ИЛИ соединен с выходами первой ячейки памятии с третьим входом последующего элемента -считывания, выходы всех элементов ИЛИ соединены с вторыми входами последующих элементов ИЛИ и с третьими входами последующих элементов считывания. Входом устройства являются ячейки

памяти, на которые поступают входные сигналы,а выходом - дешифратор, с его выхода снимаются кодовые сигналы адресов ячеек памяти, на которые поступили входные сигналы.

При использовании этого шифратора в устройствах автс 1атизированных систем управления, контроля и обработки информации он не может

10 обеспечить прием сигналов разной формы положительной и отрицательной полярности, что сужает область применения шифратора.

Целью изобретения является расши15рение области применения шифратора за счет обеспечения возможности его работы с импульсными сигналами.

Поставленная цель достигается тем, ;что в шифратор введены генера тор модулирующих импульсов, источник пороговых напряжений, элемент НЕ и входные каналы, выходы которых подключены соответственно ко входам ячеек памяти, информационные входы

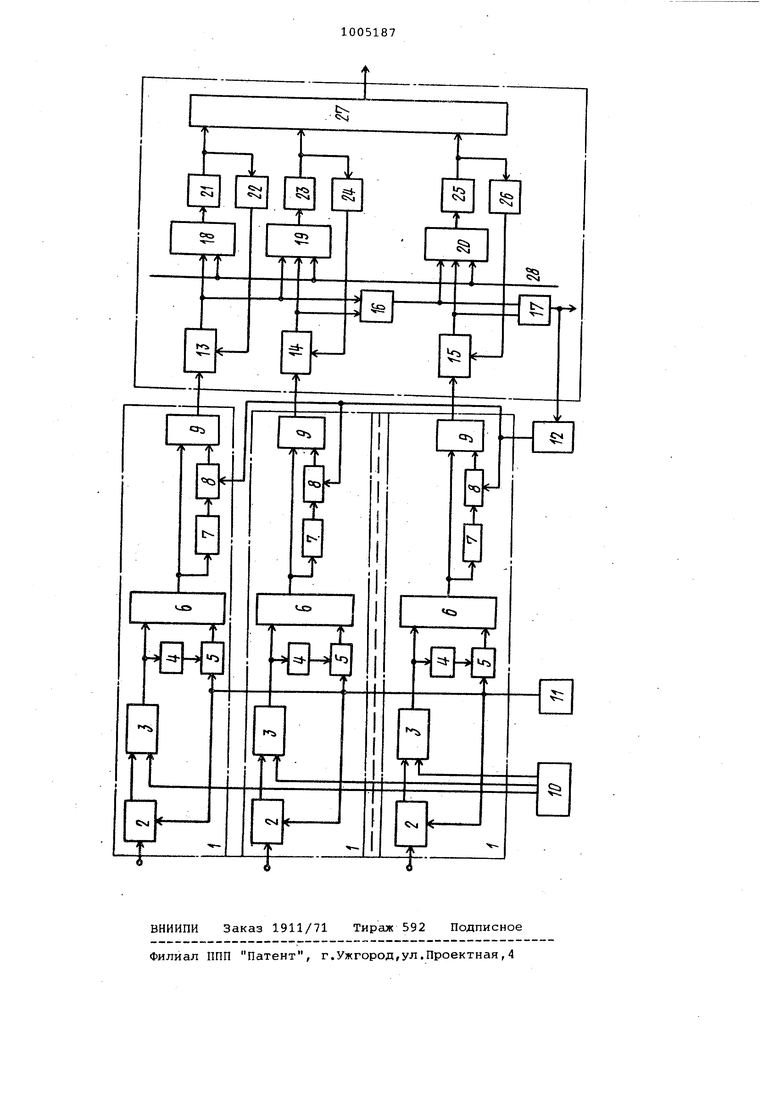

25 являются входами шифратора, а управляющие входы соединены с выходами источника пороговых напряжений, гв нератора модулирующих сигналов и элемента НЕ, вход которого подклю3Gчен к выходу одного из элементов ИЛИ. Каждый входной канал содержит амплитудный модулятор, компаратор, первые и вторые триггеры, дополнительные элементы НЕ и элементы И, причем первый вход первого триггера к вход первого дополнительного элемента НЕ подключены к выходу компаратора, первый вход которого соедине с выходом амплитудного модулятора, второй вход первого триггера подключен к выходу первого элемента И, пер вый вход которого соединен с выходом первого дополнительного элемента НЕ, первый вход второго триггера и вход второго дополнительного элемента НЕ подключены к выходу первого триггера второй вход второго триггера соедине с выходом второго элемента И, первый вход которого подключен к выходу вто рого дополнительного элемента НЕ, вы ход второго триггера является выходом канала, информационным входом ко торого является .первый вход амплитуд ного модулятора, а управляющими входами являются вторые входыамплитудного модулятора элементов И и компаратора. На чертеже представлена структурная схема шифратора.,, Шифратор содержит входные каналы 1-11 (где К - число входов шифратора , каждый из которых состоит из амплитудного модулятора 2, компаратора 3, первого дополйительного элемента НЕ 4, первого элемента И 5, первого триггера 6, второго дополнительного элемента НЕ 7, второго элемента И 8 и второго триггера 9, источник 10 пороговых напряжений, генератор 11 модулирующих импульсов, элемент НЕ 12. Шифратор также содер шт ячейки 13-15 памяти, элементы ) ИЛИ 16, 17, элементы 18-20 считывания, формирователи 21-26; входных сигналов (21,23,25) и сигналов сбро са (22,24,26), дешифратор 27. Шифратор имеет вход 28 Разрешение считывания Устройство работает следующим образом. Входные сигналы поступают . одни из входов амплитудных модуляторов2, на другие входы которых поступает последовательность модулирующих импульсов с выхода генератора 11 модулирующих импульсов Амплитудный модулятор 2 обеспечивает преобразование входных сигналов разной полярности в последовательность ё1мплитудно-модулированных импульсов без постоянной составляющей. Амплитудно-модулированная последовательность импульсов подается на входы компаратора 3, где происходит сравнение амплитуды каждого импульса с величиной порогового напряжения, которое задается источником 10 пороговых напряжений. Каждый компаратор 3 имеет выходной сигнал с двумя состояниями. Выходной сигнал компаратора 3 принимает первое состояние, если входной аналоговый сигнал больше, чем сигнал с источника 10 пороговых напряжений, а если входной аналоговый сигнал меньше, чем сигнал с источника 10, то выходной сигнал компаратора 3 принимает второе состояние. На выходе кс 4паратора 3 в момент равенства уровня входного сигнала с уровнем сигнала источника 10 происходит перепад выходного сигнала компаратора из первого во второе состояние, и наоборот. На выходе компаратора 3 формируется последовательность импульсов, характеризующих превышение импульсов амплитудно-модулированной последовательности над величиной установленного порогового напряжения. Указанные последовательности импульсов поступают на один из входов триггеров 6, устанавливая их в единичное состояние. Одновременно последовательность импульсов через элементы НБ 4 и элементы И 5 запрещает прохождение мЬдулирующих импульсов генератора 11 на .другие входы триггеров 6. При пропадании импульсов с выходов компараторов 3 запрет на прохождение модулирующих импульсов снимается и они устанавливают триггеры 6 в нулевое состояние. Таким образом происходит вьщеленне прямоугольной огибающей последовательности импульсов с выхода компаратора 3, характеризующей длительность превышения величины входного сигнала над величиной порогового напряжения. Для того, чтобы исключить пропуск импульсов длительностью, меньшей времени считывания, применены триггеры 9, на которые подаются сигналы с выходов триггеров 6, устанавливая их в единичное состояние, исключая пропуски коротких импульсов входного сигнала. Сброс триггеров 9 в исходное состояние и фо1 «ирование перепада снятия сигнала со входа Шифратора осуществляется потенциалом с выход91 элемента ИЛИ 17 через элемент НЕ 12. Указанный сигнал проходит на вход триггеров 9 в том случае, если сигнал снялся с выхода триггеров 6, т.е. триггеры 6 через элементы НЕ 7 и элементы И 8 сняли запрет на его прохождение на вход триггеров 9. Сигнал с выхода элемента НЕ 12 появляется после считывания всех появившихся сигналов с ячеек памяти 13-15. Ячейки памяти 13-15 фиксируют эти перепады и выходными сигналами открывают элементы считывания 18-20. При подаче сигнала на вход 28 Ра: решение считывания сигнал проход через элемент 18 считывания и поступает на формирователь 21 входных сигналов. Выходной сигнал с формирователя 21 подается на дешифратор 27 и на формирователь 22 сигнала сброса. На дешифраторе 27 сигнал превращается в код адреса ячейки 13 памяти и поступает с Егыхрда дешифратора 27 на выход шифратора. Сигнал ,с выхода формирователя 22 сигнала сброса попадает на вход ячейки 13 па мяти и устанавливает ее в состояние О. Сигнал считывания со входа 28 Раэраиение считывания через элемен ты считывания 19, 20 ае. проходит, так как они закрыты запрещающим сигналом, поступающим на их вход. После установки в- О ячейки 13 памяти элемент 19 считывания отк1 ашается и сигнал со входа Разрешение считывания 28 проходит через формярователи 23 и 24 и дешифратор 27 аналогично сигналу чэт элемента 18 считывания. После считывания адреса ячейки 14 памяти происходит аналогич ный процесс считывания адреса ячейки 15 памяти. Если на ячейку памяти входной сигнал не поступил, соответ ствукнций элемент считывания не откры вается, и код сцфеса соответствующий ячейк;и памяти на выходе дешифра тора 27 отсутствует. faKwt образом, факт появления си нала на входе шифратора преобразует ся в коды адресов на есо выходе. ,Технико-экономическое преиму1кест во предлагаемого шиф ратора перед про тотипом заключается в том, что он позволяет обеспечить прием сигналов постоянного тока отрицательной полярно ти, переменного напряжения ; и импульсных сигналов разной полярное ти на каждом из входов шифратора. изобретения 1. Шифратор по авт.ев; 590825, отличающийся тем, что, с целью расширения области применени шифратора за счет обеспечения возможности его работы с импульсными сигналами, в него введены генератор модулирующих импульсов, источник пороговых напряжений, элемент НЕ и входные каналы, выходы которых подключены соответственно к входам ячеек памяти, информационные входы являются входами шифратора, а управляющие входы соединены с выходами источника .пороговых напряжений, генератора модулирующих сигналов и элемента НЕ, вход которого подключен к выходу одного из элементов ИЛИ,2. Шифратор по П.1, о т ли ч а ющ и и с я тем, что каждый входнбй канал содержит амплитудный модулятор, компаратор, первые и вторые триггеры, дополнительные элементы НЕ и элементы И, причем первый вход первого триггера и вход первого дополнительного элемента НЕ подключены к выходу Koj napaTopa, первый вход которого соединен с выходом амплитудного модулятора, второй вход первого триггера подключен к выходу первого элемента И, первый вход которого соеди нен с выходом первого дополнительного элемента НЕ, первый вход второго триг гера и вход второго дополнительного элемента НЕ подключены к выходу пер вого триггера, второй вход второго триггера соединен с выходом второго элемента И, первый вход которого пoдкJшчeti к выходу второго дополнительного элемента НЕ, выход второго триггера является выходом канала, информационным входом которого является первый вход ё№шлитудного модулятора, а управляющими вхрдами являются BTOiMie входы амплитудного модулятора, а управляющими входами являются вторые входы амплитудного модулятора, элементов И и компаратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР . 590825, кл. G 11 С 11/06, 1975 (прототип).

Авторы

Даты

1983-03-15—Публикация

1981-07-29—Подача