Изобретение относится к вычислительной технике, может быть использовано в автоматизированной системе управления, контроля и обработки информации и является усовершенствованием изобретения по авт. св. ЛГо 590825.

Цель изобретения - расширение функциональных возможностей шифратора, а именно возможность его использования не только Д.ЛЯ фиксирования факта появления сигнала, но и для преобразования в код уровня и селекцию по величине входных сигналов на его шинах.

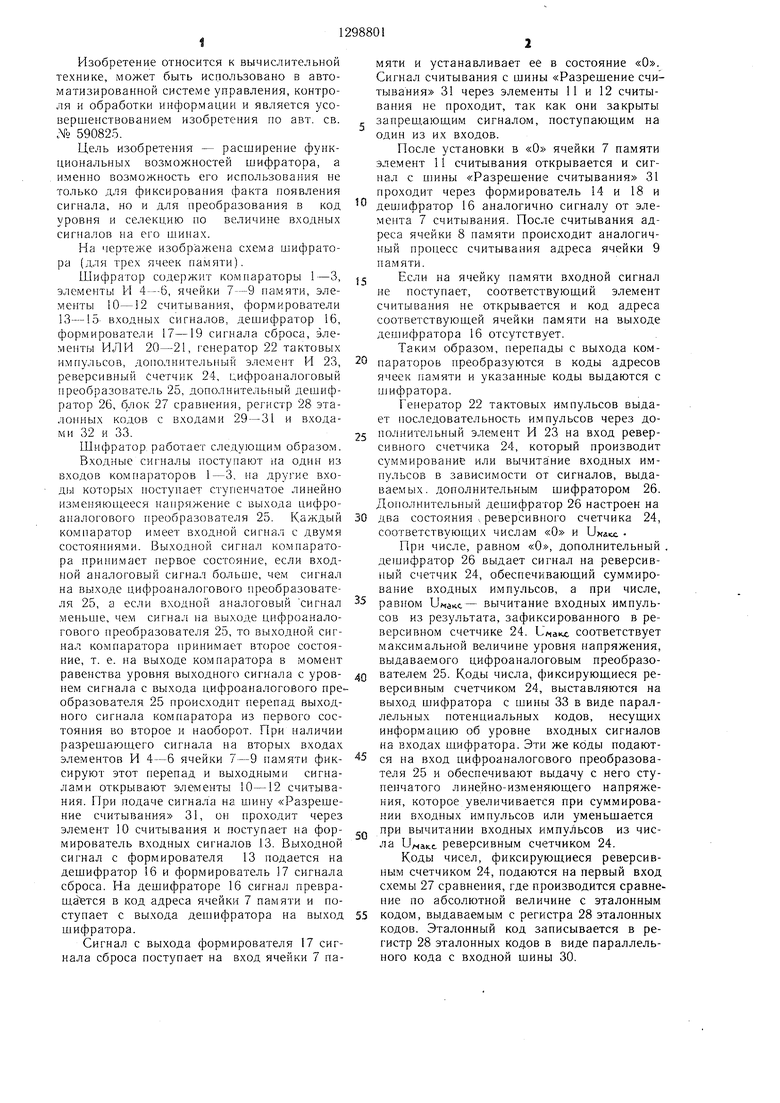

На чертеже изображена схема шифратора (для трех ячеек памяти).

Шифратор содержит компараторы 1-3, элементы И 4--6, ячейки 7-9 памяти, элементы 10-12 считывания, формирователи 13-15 входных сигналов, дешифратор 16, формирователи 17-19 сигнала сброса, эле- .менты ИЛИ 20-21, генератор 22 тактовых импульсов, дополнительный элемент И 23, реверсивный Счетчик 24, цифроаналоговый преобразователь 25, дополнительный дешифратор 26, б/iOK 27 сравнения, регистр 28 эта- „ юнных кодов с входами 29 - 31 и входами 32 и 33.

Шифратор работает следующим образом.

Входные сигналы поступают на один из входов компараторов 1-3. на другие входы которых поступает ступенчатое линейно измеияюн 1ееся напряжение с выхода цифро- аналогового преобразователя 25. Каждый компаратор имеет входной сигнал с двумя состояниями. Выходной сигнал компаратора припи.мает первое состояние, если входной аналоговый сигнал больше, чем сигнал на выходе цифроаналогового преобразователя 25, а если входной аналоговый сигнал меньше, чем сигнал па выходе цифроаналогового преобразователя 25, то выходной сигнал компаратора принимает второе состояние, т. е. на выходе компаратора в момент равенства уровня выходного сигнала с уровнем сигнала с выхода цифроаналогобого преобразователя 25 происходит перепад выходного сигнала компаратора из первого состояния во второе и наоборот. При наличии разрешаюпдего сигнала на вторых входах

мяти и устанавливает ее в состояние «О. Сигнал считывания с шины «Разрешение считывания 31 через элементы 11 и 12 считывания не проходит, так как они закрыты J. запреш,ающим сигналом, поступающим на один из их входов.

После установки в «О ячейки 7 памяти элемент 11 считывания открывается и сигнал с шины «Разрешение считывания 31 проходит через формирователь 14 и 18 и

дешифратор 16 аналогично сигналу от элемента 7 считывания. После считывания адреса ячейки 8 памяти происходит аналогичный процесс считывания адреса ячейки 9 памяти.

55 Если на ячейку памяти входной сигнал не поступает, соответствующий элемент считывания не открывается и код адреса соответствующей ячейки памяти на выходе дешифратора 16 отсутствует.

Таким образом, перепады с выхода ком20 параторов преобразуются в коды адресов ячеек памяти и указанные коды выдаются с п ифратора.

Генератор 22 тактовых импульсов выдает 11оследовательность импульсов через до25 полнительный элемент И 23 на вход реверсивного счетчика 24, который производит сум.мировапие или вычитание входных импульсов в зависимости от сигналов, выдаваемых, дополнительным шифратором 26. Дополнительный дешифратор 26 настроен на

30 два состояния ., реверсивного счетчика 24, соответствующих числам «О и Uxa«. .

При числе, равно.м «О, дополнительный дешифратор 26 выдает сигнал на реверсивный счетчик 24, обеспечивающий суммирование входных импульсов, а при числе,

35 равном ,- вычитание входных импульсов из результата, зафиксированного в реверсивном счетчике 24. Ьмакх соответствует максимальной величине уровня напряжения, выдаваемого цифроаналоговым преобразо40 вателем 25. Коды числа, фиксирующиеся реверсивным счетчиком 24, выставляются на выход шифратора с шины 33 в виде параллельных потенциальных кодов, несущих информацию об уровне входных сигналов на входах шифратора. Эти же коды подаютэлементов И 4-6 ячейки 7-9 памяти фик- 5 ся на вход цифроаналогового преобразовасируют этот перепад и выходными сигналами открывают элементы 10-12 считывания. При подаче сигнала на шину «Разрешение считывания 31, он проходит через элемент 10 считывания и поступает на формирователь входных сигналов 13. Выходной сигнал с формирователя 13 подается на дещифратор 16 и формирователь 17 сигнала сброса. На дешифраторе 16 сигнал превращается в код адреса ячейки 7 памяти и но50

теля 25 и обеспечивают выдачу с него сту- пе)чатого линейно-изменяющего напряжения, которое увеличивается при суммировании входных импульсов или уменьшается при вычитании входных импульсов из числа реверсивным счетчиком 24.

Коды чисел, фиксирующиеся реверсивным счетчиком 24, подаются на первый вход схемы 27 сравнения, где производится сравнение по абсолютной величине с эталонным

ступает с выхода дешифратора на выход 55 кодом, выдаваемым с регистра 28 эталонных шифратора.кодов. Эталонный код записывается в регистр 28 эталонных кодов в виде параллельного кода с входной шины 30.

Сигнал с выхода формирователя 17 сигнала сброса поступает на вход ячейки 7 памяти и устанавливает ее в состояние «О. Сигнал считывания с шины «Разрешение считывания 31 через элементы 11 и 12 считывания не проходит, так как они закрыты запреш,ающим сигналом, поступающим на один из их входов.

После установки в «О ячейки 7 памяти элемент 11 считывания открывается и сигнал с шины «Разрешение считывания 31 проходит через формирователь 14 и 18 и

дешифратор 16 аналогично сигналу от элемента 7 считывания. После считывания адреса ячейки 8 памяти происходит аналогичный процесс считывания адреса ячейки 9 памяти.

Если на ячейку памяти входной сигнал не поступает, соответствующий элемент считывания не открывается и код адреса соответствующей ячейки памяти на выходе дешифратора 16 отсутствует.

Таким образом, перепады с выхода компараторов преобразуются в коды адресов ячеек памяти и указанные коды выдаются с п ифратора.

Генератор 22 тактовых импульсов выдает 11оследовательность импульсов через дополнительный элемент И 23 на вход реверсивного счетчика 24, который производит сум.мировапие или вычитание входных импульсов в зависимости от сигналов, выдаваемых, дополнительным шифратором 26. Дополнительный дешифратор 26 настроен на

два состояния ., реверсивного счетчика 24, соответствующих числам «О и Uxa«. .

При числе, равно.м «О, дополнительный , дешифратор 26 выдает сигнал на реверсивный счетчик 24, обеспечивающий суммирование входных импульсов, а при числе,

равном ,- вычитание входных импульсов из результата, зафиксированного в реверсивном счетчике 24. Ьмакх соответствует максимальной величине уровня напряжения, выдаваемого цифроаналоговым преобразователем 25. Коды числа, фиксирующиеся реверсивным счетчиком 24, выставляются на выход шифратора с шины 33 в виде параллельных потенциальных кодов, несущих информацию об уровне входных сигналов на входах шифратора. Эти же коды подаются на вход цифроаналогового преобразова

теля 25 и обеспечивают выдачу с него сту- пе)чатого линейно-изменяющего напряжения, которое увеличивается при суммировании входных импульсов или уменьшается при вычитании входных импульсов из числа реверсивным счетчиком 24.

Коды чисел, фиксирующиеся реверсивным счетчиком 24, подаются на первый вход схемы 27 сравнения, где производится сравнение по абсолютной величине с эталонным

При величине кода числа с реверсивного счетчика 24 меньшем по абсолютной величине эталонного кода, блок сравнения 27 не выдает разрешающий сигнал ка первые входы соответствующих элементов И 4-6, запрещая прохождение сигналов компараторов 1-3 на вход ячеек 7-9 памяти, осуществляя селекцию по уровню выходных сигналов шифратора.

При величине кода числа с реверсивного счетчика 24 большем или равным по абсолютной величине эталонного кода, блок сравнения 27 выдает разрешающий сигнал на первые входы соответствующих элементов И 4-6, разрешая прохождение сигналов на вход ячеек 7-9 памяти.

В момент равенства уровней одного или нескольких входных сигналов величина напряжения, выдаваемого цифроаналоговым преобразователем 25, с одного или нескольких компараторов 1-3 снимаются перепа10

15

ности импульсов через дополнительный элемент И 23, и шифратор продолжает процесс преобразования в код уровней и селекцию входных сигналов шифратора.

Таким образом, с выхода устройства считывается код адреса входа шифратора с кодом величины уровня входных сигналов.

Формула изобретения

Шифратор по авт. св. № 590825, отличающийся тем, что, с целью расширения функциональных возможностей шифратора за счет преобразования в код уровня и селекции по величине сигналов на входных шинах шифратора, в него введены компараторы, группа элементов И, генератор тактовых импульсов, элемент И, реверсивный счет чик, дополнительный дешифратор, регистр эталонного кода, блок сравнения и цифроды выходных сигналов, которые при наличии 20 аналоговый преобразователь, выход которо- разрешающего сигнала с блока 27 сравне-го соединен с первыми входами компаратония на первых входах соответствующих эле-ров, вторые входы которых являются информационными входами шифратора, выходы компараторов соединены с первыми входаментов И 4-6 фиксируются ячейками 7-9 памяти, и сигналы, снимаемые с них через

элемент ИЛИ 21, дают запрет на прохожде- ,5 соответствующих элементов И группы.

ние последовательности импульсов с генератора 22 тактовых импульсов через дополнительный элемент И 23 на вход реверсивного счетчика 25, который останавливает счет и фиксирует свое состояние. При подавыходы которых соединены с соответствующими входами ячеек памяти, выход генератора тактовых импульсов соединен с первым входом элемента И, второй вход которого соединен с выходом последнего элеменче сигналов «Разрешение считывания про- 30 та ИЛИ, а выход - со счетным входом

изводится последовательная выдача кода адреса входов шифратора, на которых произошло равенство уровней входных сигналов с напряжением цифроаналогового преобразователя 25 и считывание на выходе

реверсивного счетчика, управляющие входы которого соединены с выходами дополнительного дещифратора, вход которого соединен с входом цифроаналогового преобразователя, выходом реверсивного счетчика.

шифратора кода уровня входного сигнала. 35 первым входом блока сравнения и является

Останов цифроаналогового преобразователя 25 производится до тех пор, пока не произойдет считывание всех адресов ячеек памяти, изменивших свое состояние.

После считывания элемент ИЛИ 21 сниодним из выходов шифратора, выход блока сравнения соединен с вторыми входами элементов И группы, второй вход блока сравнения соединен с выходом регистра эталонных кодов, вход которого является управляющим входом шифратора. ,

мает запрет на прохождение последовательности импульсов через дополнительный элемент И 23, и шифратор продолжает процесс преобразования в код уровней и селекцию входных сигналов шифратора.

Таким образом, с выхода устройства считывается код адреса входа шифратора с кодом величины уровня входных сигналов.

Формула изобретения

Шифратор по авт. св. № 590825, отличающийся тем, что, с целью расширения функциональных возможностей шифратора за счет преобразования в код уровня и селекции по величине сигналов на входных шинах шифратора, в него введены компараторы, группа элементов И, генератор тактовых импульсов, элемент И, реверсивный счет чик, дополнительный дешифратор, регистр эталонного кода, блок сравнения и цифровыходы которых соединены с соответствующими входами ячеек памяти, выход генератора тактовых импульсов соединен с первым входом элемента И, второй вход которого соединен с выходом последнего элеменреверсивного счетчика, управляющие входы которого соединены с выходами дополнительного дещифратора, вход которого соединен с входом цифроаналогового преобразователя, выходом реверсивного счетчика.

первым входом блока сравнения и является

одним из выходов шифратора, выход блока сравнения соединен с вторыми входами элементов И группы, второй вход блока сравнения соединен с выходом регистра эталонных кодов, вход которого является управляющим входом шифратора. ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1980 |

|

SU886048A2 |

| Шифратор | 1980 |

|

SU920835A1 |

| Шифратор | 1981 |

|

SU1005187A2 |

| Шифратор | 1985 |

|

SU1298802A2 |

| Шифратор | 1978 |

|

SU752470A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2028730C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ, ОТОБРАЖЕНИЯ И ОБРАБОТКИ ПЕРЕХОДНЫХ ПРОЦЕССОВ В КОНТАКТНОЙ ЦЕПИ МАГНИТОУПРАВЛЯЕМЫХ ПРИБОРОВ | 1990 |

|

RU2060552C1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться в авто.матизированных системах управления и контроля. Целью изобретения является расширение функциональных возможностей шифратора. Он используется не только для фиксации появления сигнала, но и для преобразования в код уровня и селекцию по величине входных сигналов па его шинах. Поставленная цель достигается тем, что в устройство вводятся компараторы 1-3, элементы И 4-6, генератор тактовых импульсов 22, дополнительный элемент И 23, реверсивный счетчик 24, цифроаналоговый пре- образовате,яь 25, дополнительный дешифратор 26, блок сравнения 27, регистр эталонных кодов 28. Изобретение позволяет увеличить достоверность обрабатываемой информации за счет сравнения ее с эталонными значениями, что исключает прием недостоверной информации. ил. ,29, (С N5 СО ас ас Го 32 33 30 31

| Шифратор | 1975 |

|

SU590825A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-22—Подача