рому выходу схемы сравнения и к Тре-г тьему выходу блока управления, четвертый вход четвертого форьг рователя сигналов соединен со вторым выходом второго фоЕ 1ирователя сигналов и третьим входом преобразователя кодов, четвертый вход и выход которого прдключены соответственно к выходу переключателя и ко второму входу бло1ка управления, первый выход которого соединен со входами второго и третьего регистров, выходы которых подключе ны соответственно ко второму и к третьему входам схемы сравнения, выход преобрааователя кодов является выходом устройства.

2. Устройство по П.1, отличаю Т е е с я тем, что блок задает ния режимов контроля,содержит первый и третий триггеры, пятый и шестой формирователи сигналов, первый и второй элементы задержки, причем первый и второй единичные входы первого триггера подключены соответственно к первым выходам пятого и шестого .формирователей сигналов, вторые выходы которых подключешл соответственно к первому и второму единичным вхот дам второго триггера и первому Нулезому входу первого триггера, второй нулевой вход которого соединен с третьим выходом шестого формирователя сигналов, первым нуЙевЕлм входом второго триггера и единичным входом третьего триггера, выход первого триггера подключен ко входу первого элемента задержки, выход которого соединен со вторым нулевым входом второго триггера и пёрвь 1 нулевым входом третьего триггера, второй нулевой вход которого подключен к выходу второго элемента задержки, вход которого соединен с выходом второго триггера, первым входом пятого формирователя сигналов и выходом третьего

триггера, первый вход шестого формирователя сигналов и второй вход пятого формирователя сигналов являются .соответственно первым и вторым входами блока, второй вход шестого фор 1ирователя сигналов и третий вход пятого формирователя сигналов объединены и являются третьим входом блока, выходом которого являются выходы триггеров.

, 3. Устройство по пп 1 и 2, о т л и ч а ю,щ е е с я тем, что блок местного уп эавления содержит четвертый, пятый и шестой триггеры, третий элемент задержки, элемент ИЛИ и элементы И, первые входы которых соединены с выходом четвертого триггера, причем второй вход первого элемента И подключен к выходу пятого триггера, вторые входы второго и третьего элементов И соединены соответственно с единичнь и с нулевым В14ходами шестого триггера, единичный вход которого подключен к выходу четвертого элемента И, нулевые входы триггеров соединены с выходом элемента ИЛИ, первый вход которого подключен к выходу трет ье го элеме нт а. з адержк и, вход которого соединен с выходом первого элементам, второй вход четвертого элемента И и единичш вход пятого триггера объединены и являются первым входом блока, третьи входы первого, второго и третьего элементов И объединены и являются вторым входе блока, единичный вход Четвертого триггера и второй вход элемента ИЛИ объединены и являются третьим входом блока, выходы второго и третьего элементов И объединены и являются первъгм выходом блока, выход первого элемента И н выход етвертого триггера объединены и являются вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля электрического монтажа | 1987 |

|

SU1455347A1 |

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для управления прошивкой постоянных накопителей | 1979 |

|

SU894788A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство со считыванием без разрушения информации | 1979 |

|

SU773724A1 |

| Устройство для программного управления | 1987 |

|

SU1474595A1 |

| Многоканальное устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1980 |

|

SU868742A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

1. УСТРОЙС ВО ДЛЯ КОНТРОЛЯ БЛОЮШ ,содержащее первый комму -атор, первый и. второй формирователи сигналов, датчик напряжений, первый регистр, счетчйк, накопитель г переключатель, дешифратор адреса, схему сравнения и блок управления, первый выход которого соединен с первыми входами накопителя, счетчика и первого регистра, причем первый выход первого формирователя сигналов подключен к первому входу второго формирователя сигналов, второй вход которого соединен со вторым выходом блока управления, а третий .вход с первым входом блока управления и первьм выходом схемл сравнения, первый вход которой подключен к выходу счетчика, пер8С 4у входу переключателя и второму входу первого регистра, выход которого соединен со втойлм Входом переклоочателя, выход которого подключен к первому входу дешифратора адреса, выход которого соединен с первым входомпервого коммутатора, первые входы датчика напряжений и первого формирователя сигналов соединесо с выходом накопителя, второй вход первого коммутатора является входом устройства, отгл я дающееся тем, .что, с целью повьгиения быстродействия и упрснчение устройства, в него введены блок .эгшания реждагов контроля, второй -Коммутатор, шифратор, второй и третий регистры, трег , тий и четвертый форм(фователи сигна-Vлов, преобразователь кодов и блок местного управления, причем первый и второй вхОдаа преобразователя кодов подключены соответственно к. перйому выходу датчика напряжений и к первому выходу блока местного управления, первый вход которого соединен со вторым выходом датчика напряжений, первый вход третьего формирователя сигналов подключен к выходу блока задания режимов контроля , первому входу шифратора, второму входу накопителя и первому входу четвертого формирователя сигналов, первый выход и второй вход которого ;соединены соответственно с третьим входом накопителя, вторьмй входами блока местного управления и шифратора и со вторым выходом блока местного управления, третий вход которого подключен к выходу третьего формирователя сигналов, второму входу дешифратора адреса, второму входу счетчика, третьему входу первого регистра, третьему входу переключателя и первому входу второго коммуtv9 татора, второй вход и выходкотрро-СО го соединены соответственно с К1ходом-. первого коммутатора и со вторслм BxoV со о дом датчика напряжений, третий вхоД| вторрго коммутатора подключен ко втрСХ) рому выходу первого форм{(ррвателя сигналов, второй вход которого соединен с выходом шифратора и,третьим входе датчика напряжений, четвертый вход которого подключен к третьему входу первого фося ирователя сигналов и второму выходу четвертого формирователя сигналов, третий вход которого соединен с первш выходом второ- . то формирователя сигналов, вторым вхо дом третьего формирователя сигналов и, первым входс 1 блока задания режимов контроля, второй и третий входы кото рого подключен соответственно ко

Изобретение относится к вычислительной технике и может быть использовано для контроля блоков постоянной памяти, а также для контроля логических блоков.

Известно устройство для контроля блоков памяти, содержащее блок ввода информации, блок управления, адре ный блок, блок синхронизацииj блок сравнения, коммутатор ij .

Недостатком этого устройства является низкая достоверность контроля

Наиболее близким техническим решением к данному изобретению является устройство для контроля блоков

памяти, содержащее адресный коммута тор, блок анализа неисправностей и логической обработки, блок оперативной памяти, блок управления, блок

5 генерации стимулирую 1их воздействий, блок памяти неисправностей, блок выявления неисправностей .

Недостатками известного устройства являются его сложность, большая трудоемкость контроля и низкое быстродействие, обусловленные применением программ для процесса контроля, вводом программ с перфолент в оператив:ную память устройства и необходивмс 5 тью частой смены програкм.

Цель изобретения - повышение быстродействия и упрощение устройства. Поставленн я цель достигается тем, что в устройство для контроля блоков памяти, содержащее первый коммутатор, первый и второй формирователи сигна- 5 лов, датчик напряжений, первый pef гистр, .счетчик, накопитель, переключатель, дешифратор адреса, схему сра:внения и блок управления, первый выход которого соединен с первыми вхо- 10 дами накопителя, счетчика и первого регистра, причем первый выход первого формирователя сигналов подключен к первому входу второго формирователя сигналов, второй вход которого соединен 15 со вторым выходом блока управления, а третий вход ,- с первЕвд входом блока управления и первьм выходом cxeNM сравнения, первый вход которой подклю-. чен к выходу счетчика, первому входу 20 переключателяигвторому входу первого регистра, выход .которого соединен со BTOpEiM входом переключателя, выход которого подключен к первс 4у входу дешифратора адреса, выход которого сое- 25 динен с первым входом первого комлутатора, первые входы датчика напряжений и первого формирователя сигналов соединегал с выходом накопителя, второй вход первого коммутатора яв- -ляется входом устройства, введены блок задания режимов контроля, второй кс лмутатдр, шифратор, второй и третий регистры, третий и четвертый формирователи сигналов, преоораэова- тель кодов и блок местного управле- ния, причем первый и второй входы tipe(Образователя кодов подключены соответственно к. первому выходу датчика напряжений и к первому выходу блока местного управления, первый вход 40 которого соединен со вторым выходом датчика напряжений первый вход третьего формирователя сигналов подклкгчен к выходу блока задания режимов контроля, первомучвходу шифратора, 45 второму входу накопителя и первому входу четвертого формирователя сигналов, первый выход и второй вход которого соединены соответственно с третьим входом накопителя г вторыми вхо- ы дами блока местного управления и ашфpaTOt и со вторым выходом блока местного управления, третий вход кото- рогр подключен к выходу третьего форт мирователя сигналов, второму входу дешифратора адреса, второму входу счетчика, третьему входу первого ре,гистра, третьему входу переключателя 1и первому входу второго коммутатора, второй вход и выход которого соединены соответственно с выходом первогобО коммутатора и со вторым входом датчика напряжений, третий вход второго коммутатора подключен ко второму выходу первого формирователя сигналов, второй вход которого соединен 65

с выходом шифратора и третьим входсм датчика напряжений, четвертый вход которого подколочен к третьему входу первого формирователя сигналов и второму выходу четвертого формирователя сигналов, третий вход которого соединен с первым выходом второго формирователя сигналов, вторым входо третьего формирователя сигналов и первым входсм блока задания режимов тсонтроля, второй и третий входы коаброго подключены соответственно ко второму выходу схемы сравнения и к третьему выходу блока управления, четвертый вход четвертого формирователя сигналов соединен со вторым выходом второго рмирователя сиг.налов и третьим входом преобразователя кодов, четвертый вход и выход которого подключены соответственно к выходу переключателя и ко второму входу блока управления, первый выход которого соединен со входами второго и третьего регистров, выходш которых подключены соответственно ко второму и к третьему входам сх:емы сравнения, выход преобразователя кодов является выходом устройства

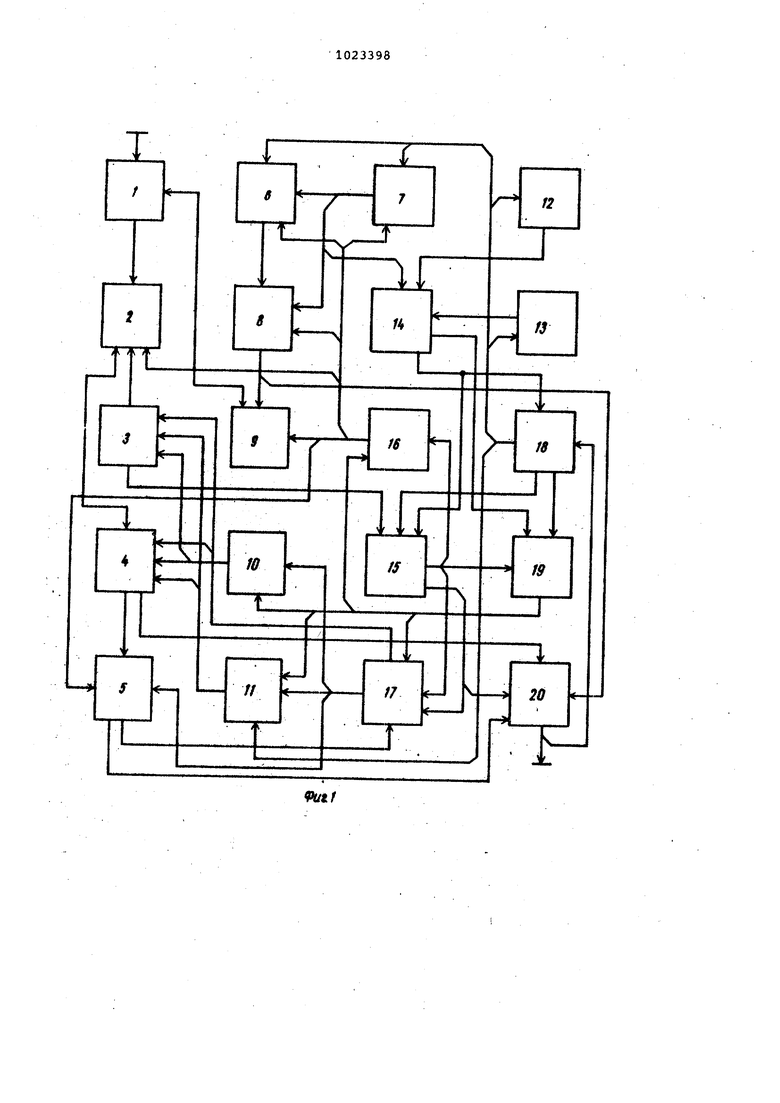

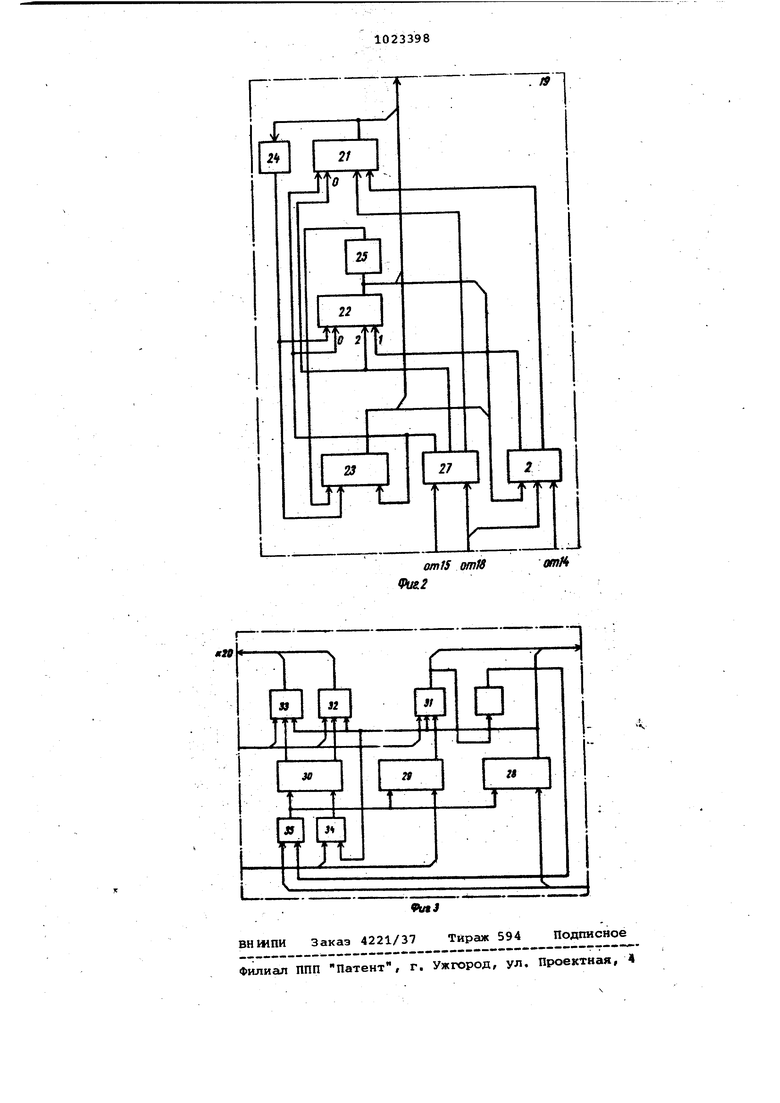

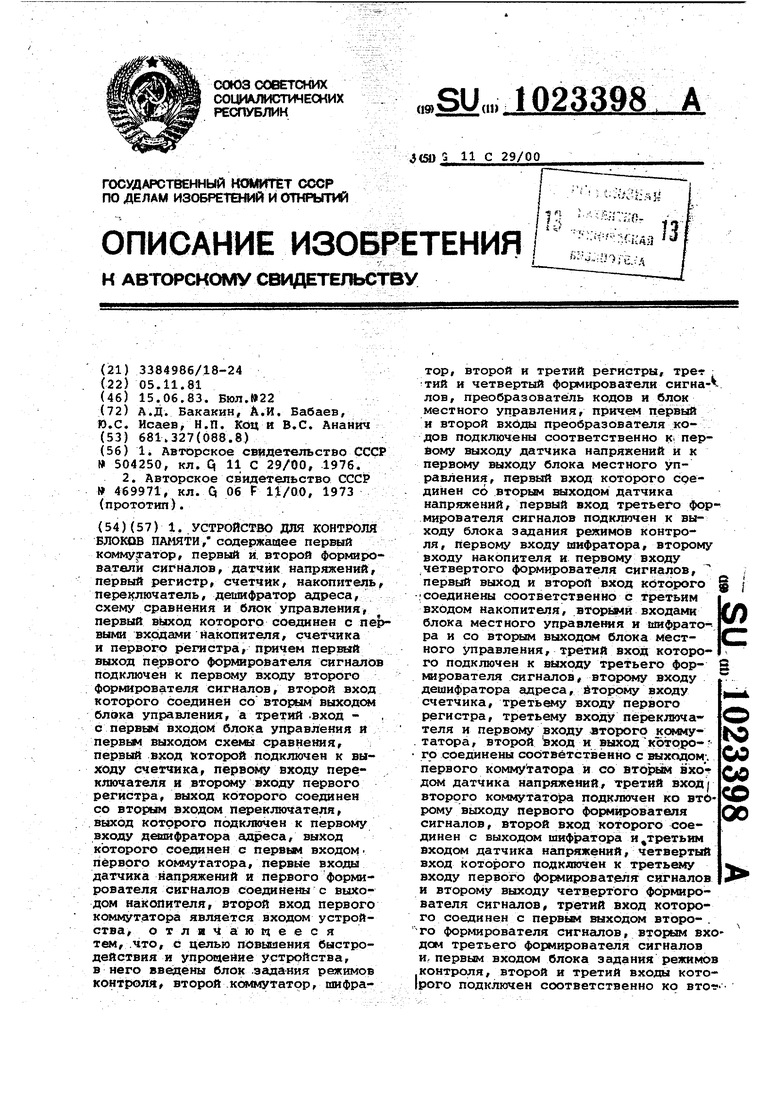

Кроме того, блок задания режийов контроля содержит первый, второй и третий триггеры, пятый и шестой формирователи сигналов, первый и второй эл 4енты задержки, причем первый и второй единичные входы первого триггера подключены соответственно к первым выходам пятого и шестого формирователей сигналов, вторые выходы которых подключены соответст вено к первому и второму единичньм входам второго триггера и первому нулевому входу первого триггера, второй нулевой вход которого соеди г нен с третьим выходом шестого формирователя сигналов, первым нулевым входом второго триггера и единичньм входом третьего триггера, выход первого триггера подключен ко входу первого элемента задержки, выход которого соединен со вторым нулевым входом второго триггера и первым нулевым входом третьего триггера, второй нулевой вход которого подключен к выходу всорого элемента задержки, вход которого соединен с выходом второго триггера, первый входом пятого формирователя сигналов и .выходом третьего триггера, первый вход шестого Формирователя сигналов и второй вход пятого формирователя сигналов являются соответственно первым и вторым входам блока, втЪрюй вход шестого Формирователя сигналов и третий вход пятого формирователя сигналов объединены и являются третьим входом блка, выходом KOifoporo являются выход триггеров. Блок местного управления содержит четвертый, пятый и шестой триг-, геры, третий элемент задержки, элемент ИЛИ и элементы И, первые входы которых соединены с выходом четвертого триггера, причем второй вход первого элементна И подключен к ааыходу пятого триггера, вторые входы второго и третьего элементов И соединены соответственно с единичиьм и с нулевым выходом шестого триггера, единичный вход которого подключен к выходу четвертого элемента И, нулевые входы триггеров соединены с выходом элемента ИЛИ, первый вход которого подключен к выходу третьего элемента задержки, вход которого соединен с выходом первого элемента И, второй вход четвертого элемента И и единичный вход пятого триггера объединены .и являются первым входом блока, третьи входы первого, второго и третьего элементов И объединены и являются вторым, входом блока, единич ный вход четвертого триггера и второй вход элемента ИЛИ объеди нены и являются третьим входом блока выходы второго и третьего элементов oбъeди eны и являются первым выходом блока, выход первого элемента И и выход четвертого триггера объединены и являются вторым выходом блока. На фиг.1 представлена функциональная схема предложенного устройства; на фиг. 2 и 3 - соответственно функциональные блока эгшания режимов Ко.нтроля и блока местного хшравления Устройство содержит (фиг.1) первый 1 и второй 2.коммутаторы, первый формирователь 3 сигналов, датчик напряжений 4, блок 5 местного управления, первый регистр 6, счетчик 7, переключатель 8, дешифратор 9 а,цреса, шифратор 10, накопитель 11, второй 12 и третий 13 регистры, схему сравнения 14, второй формирователь 15 сигналов предназначенный для формирования упра ляющих команд, третий формирователь 16 сигналов, предназначенный для фор;мтфования тактовых сигналов, четвертый (формирователь 17 сигналов, предназначенный для формирования измерительны и управляющих сигналов, блок.18 управ ления, блек 19 задания режимов KOHTpo ля и преобразователь 20 кодов. Блок задания режимов контроля содержит (фиг.2) первый 21, второй 22 и третий 23 триггер, первый 24 и второй 25 элементы задержки, пятый 26 и шестой 27 формирователи сигналов. Блок местного управления содержит (фиг.j) четвертый 28, пятый 29 и шестой 30 триггеры, первый 31, второй 32, третий 33 и четвертый 34 элементы И и элемент ИЛИ 35. Устройство, работает сл.едующим образом. Перед началом проверки оператор через блок 18 фиг.1 вводит данные в накопитель 11 и таким образом задает виды проверки, по которым будет контролироваться проверяемый блок памяти. Видами проверки объекта контроля ОК , может, например, быть измерение сопротивления изоляции разобщенных цепей, определение наличия перемычек, прямого и обратного сопротивления переходов диода, падения напряжения на элементе и Т.д. Перед началом работы оператор кроме данных, определяющих контролируемые параметры ОК, должен задать количество контролируемых цепей посредством ввода числа в регистры 12 и 13. При этом в схеме сравнения 14 по достижении соответствующей точки формируется сигнал, который переключает устройство на следующий вид проверки . Начало контроля осуществляется пуском через блок 18, при этом формируется сигнал включения вида контроля в блоке 19 и включается формирователь 15 сигналом по второму входу. Формирователь 15 генерирует тактовые сигналы для синхроиизации дальнейшей работы устройства, продвижение кото рых может быть прервано сигналом на третьем входе формирователя-15. Тактовые сигналы определяют последовательность команд, составляющих алгоритм проверки по каждому виду контроля. Последовательностью команд, например, может быть опрос дешифратора 9 для подключения выбранной точки, включение реле в коммутаторе 1, включение реле в KONwyTaTope 2, перевод кода адреса из счетчика 7 в регистр 6, включение формирователя 17 и т.д. При включении формирювателя 17 ра.боты формирователя 15 прерывается и управление передается формирователю 17, КОТО1Ж1Й формирует последовав тельность сигналов, поступающих на первый вход шифратора Ю. Одновременно с сигналом, из которого формирует ся код операции в шифраторе 10, формируется импульс сопровождения, которий определяет принадлежность кода датчику 4 или формирователю 3. Управление формирователем 3 и датчиком 4 осуществляется кодом, поступающим с выхода шифратора 10 на вход формирователя 3 и вход датчика 4. пя распознания принадлежности соответствующему блоку код сопровождается импульсом сопровождения, поступаквдим с выхода формирователя 17 на . вход датчика 4 и вход формирователя 3.i Формирование кода на выходе Шифратора 10 осуществляется таким образом, что на кажда1й импульс опера дии, поступающий с формирователя 17 на первый

вход шифратора 10, на его шлходе фot)мируется пятиразрядный двоичный код. Работа шифратора 10 управляется сигналами из блока 19, задающего вид контроля.

Объект контроля подключается на вход коммутатора 1. Подключение контролируемых точек производится при включении реле в коммутаторе 1 сигналом, поступакхцим с дешифратора 9. Адрес точки задается счетчиком 7 или регистром 6 через переключатель 8. BiperHCTp 6 адрес может быть задан оператором или переводится из счет-. чика 3 в процесс работы. Подключение точки объекта контроля может быть произведено включением коюлута;тора 1 одного реле на один из двух каналов или двумя, одновременно.

Количество воздействий определяется требованиями объекта контроля. Датчик 4 может работать в двух режима : сравнение с эталонной величиной допусковый контроль или непосредственно измерение оконтролируемой величины. Работа датчика 4 контролируется блоком 5, на вход которого поступают из датчика 4 сигналы Готовность, Конец измерения и Выход ноль-органа. Во время измерения с выхода блока 5 в формирователь 17 поступает сигнал прерывания работы формирователя 17.. Запрет снимается сигналом конца .мерения по сигналу результата Норма. При отсутствии сигнала Норма с выхода блока 5 на вход преобразования кода в регист преобразователя 20 вводится код «адреса проверяемых чек объекта контроля с выхода переключателя 8 и код результата контроля, с выхода датчика 4, которые выводятся на выход преобразователя 20.

Таким образом, в предложенном устройстве для процесса контроля не требуется грокюздких программ, отсутствуют блоки считывания информации с перфоленты, а введение формирователей 16 и 17, шифратора 10 блока 19 и блока 5 позволяет сократить примерно в тридцать раз время на проверку одного блока памяти.

Технико-экономические преимущеси,ва предложенного устройства заключаются в его упрощении и более высоком быстродействии по сравнению с прототипом.

19

V

mVt

om15 omlS Pus.2

Авторы

Даты

1983-06-15—Публикация

1981-11-05—Подача