(54) УСТРОЙСТВО УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1980 |

|

SU1005039A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Множительно-сдвиговое устройство | 1982 |

|

SU1013951A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

1

Изобретение относите} к вычислительной технике.

Известно устройство умножения/ содержащее регистр множимого, регистр множителя, дешифратор множителя и многоразрядную суммирующую схему 1 .

Наиболее близким техническим решением к изобретению является устройство для контроля арифметического блока по модулю, содержащее блок сравнения контрольных кодов, подключенный входами к первому выходу блока управления, выходу блока сложения контрольных кодов, подключенного первым входом к второму выходу блока управления/ и выходу блока умножения контрольных кодов/ один из вхоДов которого соединен с первым . выходом регистра множителя, второй выход которого подключен к первому входу блока управления, соединенному третьим выходом через блок элементов И с вторым входом блока сложения контрольных кодов, третий вход которого подключен к выходу блока свертки, подключенного входгили к четвертому выходу блока управления, одному из выходов сумматоров, подключенного другим входом и выходом

к блоку управления/ злемент И подключен к пятому выходу блока управлечкя, элемент ИЛИ подключен входом к выходу элемента И и шестому входу блока уп1)айления и соединенный выходами с вторыми входами блока элементов И, схема совпадения соединена выходом с вторым входом элемента И, логический блок подключен входами к

10 третьему выходу регистра множимого и выходу схемы совпадения и соединенным выходдм с вторым входом блока умножения L21.

Целью изобретения является повы15шение достоверности результата.

Для достижения поставленной цели устройство умножения, содержащее регистр множимого, регистр множителя/ блок суммирования и дешифратор мно20жителя, при этом выход регистра множимого подключен к первому входу блока суммирования, второй вход которого подключен к выходу дешифратора множителя, вход которого соединен с выхо25дом регистра множителя, первый выход блока суммирования является выходом устройства-, блок подсчета коли чества переполнений, блок определения положительного результата и блок 30 определения количества отрицательных

частичных произведений, при этом выход блока суммирования подключен к входу блока подсчета количества переполнений, выход которого соединен с первым входом блока определения положительного результата, выход которого является выходом устройства, выход блока определения количества отрицательных частичных произведений подключен к входу блока определения положительного результата, второй выход дешифратора множителя соединен с входом блока определения количества отрицательных частичных произведений, с вторым выходом многорядной суммирукндей схемы, а выход с первым входом блока определения положительного результата, вход блока определения количества отрицательных частичных произведений соединен с вторым выходом дешифратора множителя, а выход - с вторым входом блока -определения положительного результата, выход которого является выходом устройства умножения.

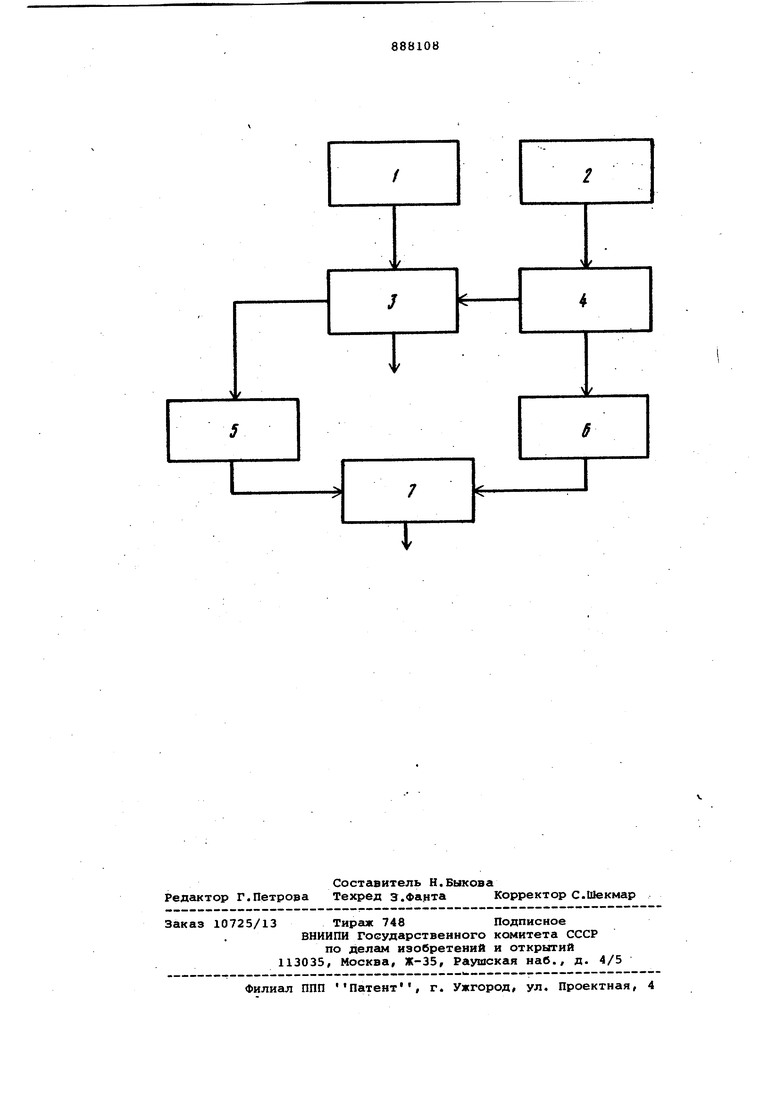

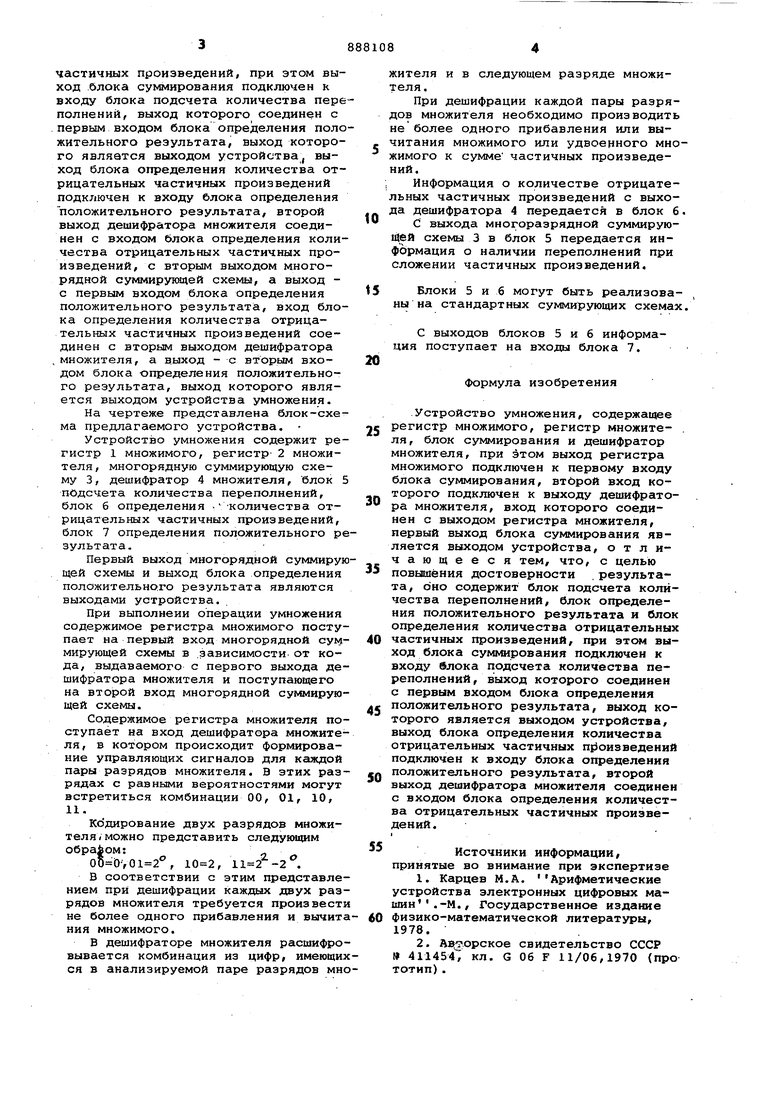

На чертеже представлена блок-схема предлагаемого устройства.

Устройство умножения содержит регистр 1 множимого, регистр 2 множителя, многорядную суммирующую схему 3, дешифратор 4 множителя, блок 5 подсчета количества переполнений, блок б определения . -количества отрицательных частичных произведений, блок 7 определения положительного результата.

Первый выход многорядной суммирующей схемы и выход блока определения положительного результата являются выходами устройства.

При выполнеии операции умножения содержимое регистра множимого поступает на первый вход многорядной суммирующей схемы в .зависимости- от кода, выдаваемого с первого выхода дешифратора множителя и поступающего на второй вход многорядной суммирующей схемы.

Содержимое регистра множителя поступает на вход дешифратора множителя, в котором происходит формирование управляющих сигналов для каждой пары разрядов множителя. В этих разрядах с равными вероятностями могут встретиться комбинации 00, 01, 10, 11.

Кодирование двух разрядов множителя «можно представить следующим образом: о

, , -2 . В соответствии с этим представлением при дешифрации каждых двух разрядов множителя требуется произвести не более одного прибавления и вычитания множимого.

В дешифраторе множителя расшифровывается комбинация из цифр, имеющихся в анализируемой паре разрядов множителя и в следующем разряде множителя.

При дешифрации каждой пары разрядов множителя необходимо производить не более одного прибавления или вычитания множимого или удвоенного множимого к сумме частичных произведений.

Информация о количестве отрицательных частичных произведений с выхода дешифратора 4 передается в блок 6

С выхода многоразрядной суммирующей схемы 3 в блок 5 передается информация о наличии переполнений при сложении частичных произведений.

15 Блоки 5 и б могут быть реализованы на стандартных суммирующих схемах.

с выходов блоков 5 и 6 информация поступает на входы блока 7.

Формула изобретения

Устройство умножения, содержащее 5 регистр множимого, регистр множите- . ля, блок суммирования и дешифратор множителя, при этом выход регистра множимого подключен к первому входу блока суммирования, втброй вход которого подключен к выходу дешифратора множителя, вход которого соединен с выходом регистра множителя, первый выход блока суммирования является выходом устройства, отличающееся тем, что, с целью

повышения достоверности . результата, оно содержит блок подсчета количества переполнений, блок определения положительного результата и блок определения количества отрицательных

0 частичных произведений, при этом выход блока суммирования подключен к входу блока подсчета количества переполнений , выход которого соединен с первым входом б;1ока определения

f положительного результата, выход которого является выходом устройства, выход блока определения количества отрицательных частичных п{3оизведений подключен к входу блока определения

Q положительного результата, второй выход дешифратора множителя соединен с входом блока определения количества Отрицательных частичных произведений .

Источники информации,

принятые во внимание при экспертизе

0 физико-математической литературы, 1978.

W 411454, кл. G Об F 11/06,1970 (про тотип).

Авторы

Даты

1981-12-07—Публикация

1979-06-29—Подача