Изобретение относится к вычислительной технике и может найти применение в специализированных цифровых вычислительных машинах.

Известны устройства для умноже- . ния f содержащие дешифратор множителя;, (или блоки умножения сомножителей немаксимального формата), коммутаторы частичных произведений, инверторы кода и преобразователь многорядного кода в двухрядный или однорядный, в которых множитель разбивается на группы, каждой из которых соответствует частичное произведение, равное множимому определенной кратности со знаком плюс или минус 11 и С2.

Недостатком этих устройств являются значительные аппаратурные затраты, связанные с увеличением количества одноразрядных сумматоров, необходимых для удлинения в старших частях частичных произведений сумматоров преобразователя многорядного кода для суммирования отрицательных частичных произведений, подаваемых через инвертор кода с дополнительной единицей младшего разряда.

Наиболее близким к предлагаемому является устройство для умножения , содержащее дешифратор множителя, блок суммирования частичных произведений (матрицу сумматоров представляющую собой сумматоры с запоминанием переносов ), коммутаторы, заменяющие сумматоры старших частей частичных произведений в каждом слое

10 суммирования, блок формирования кратных множимого, .выходной сумматор. Каждый коммутатор выполняет функции суммирования старших разрядов одного частичного произв едения со знаковыми

15 разрядами двух других, сдвинутых в сторону младших разрядов 3 J.

Недостатком такого устройства является большое количество слоев суммирования в связи с использова20нием сумматоров с запоминанием переносов . .

Цель изобретения - упрощение устройства.

Для достижения поставленной цели

25 устройство для умножения, содержащее блок формирования кратных множимого, коммутаторы кратных множимого, дешифраторы групп разрядов мнoжитeля блоки инверсии, блок суммирования

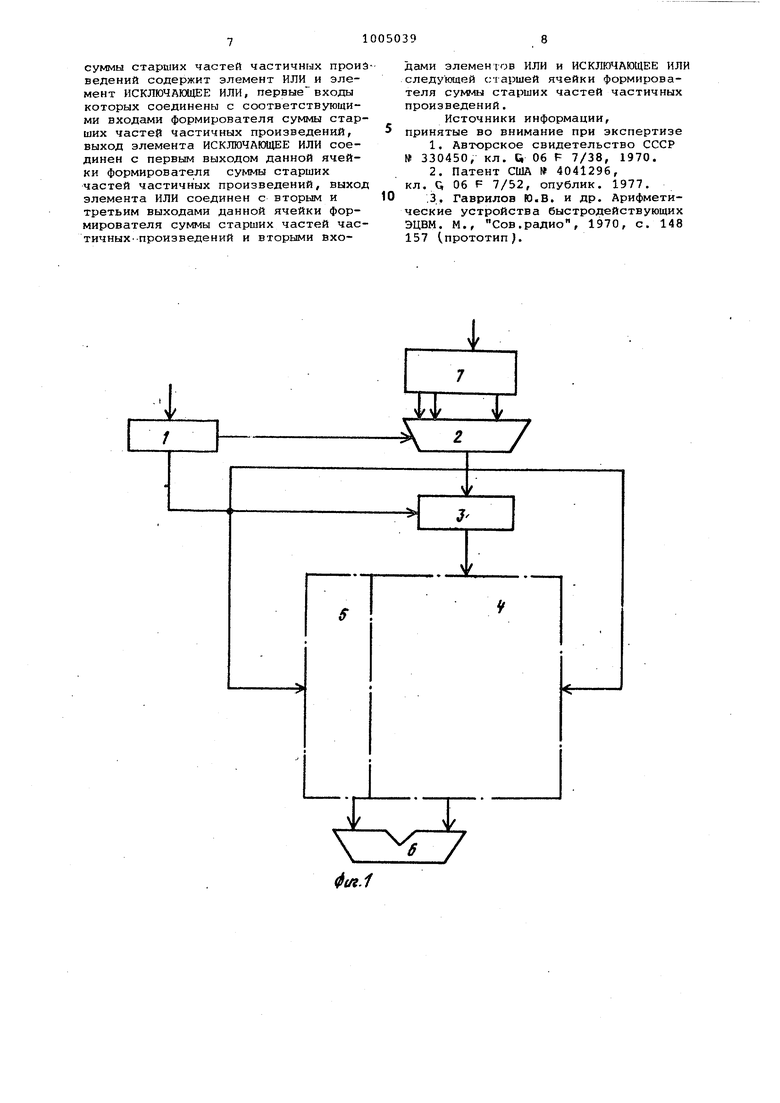

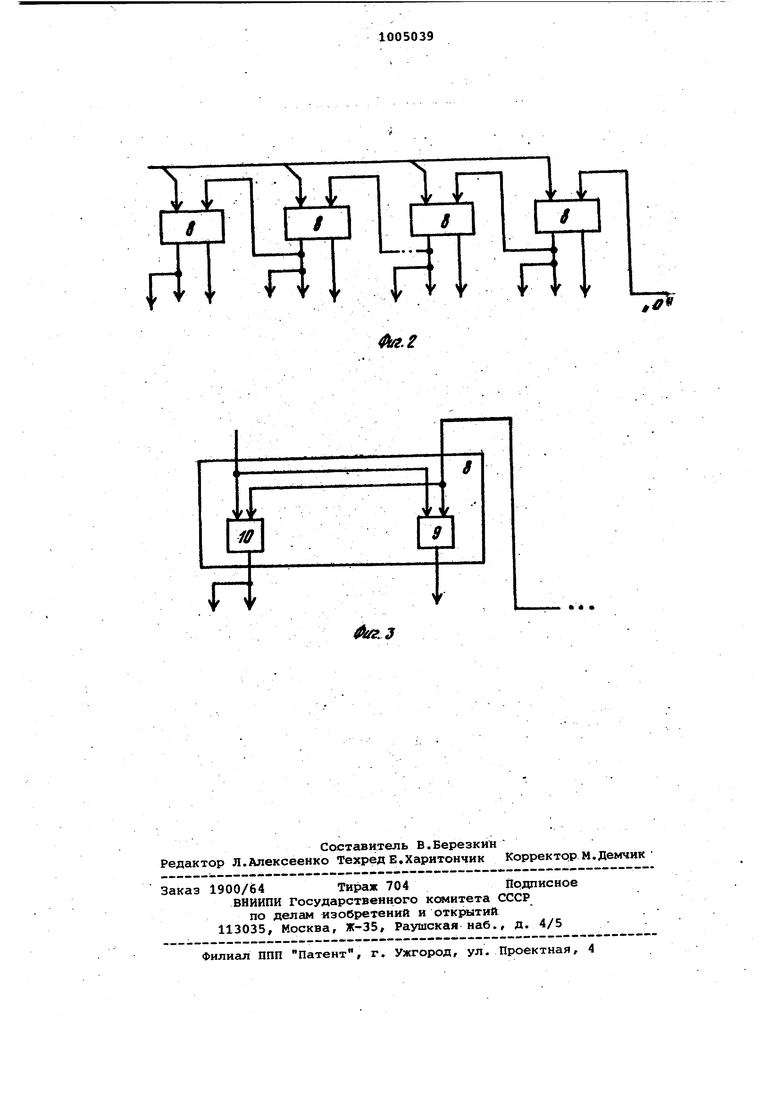

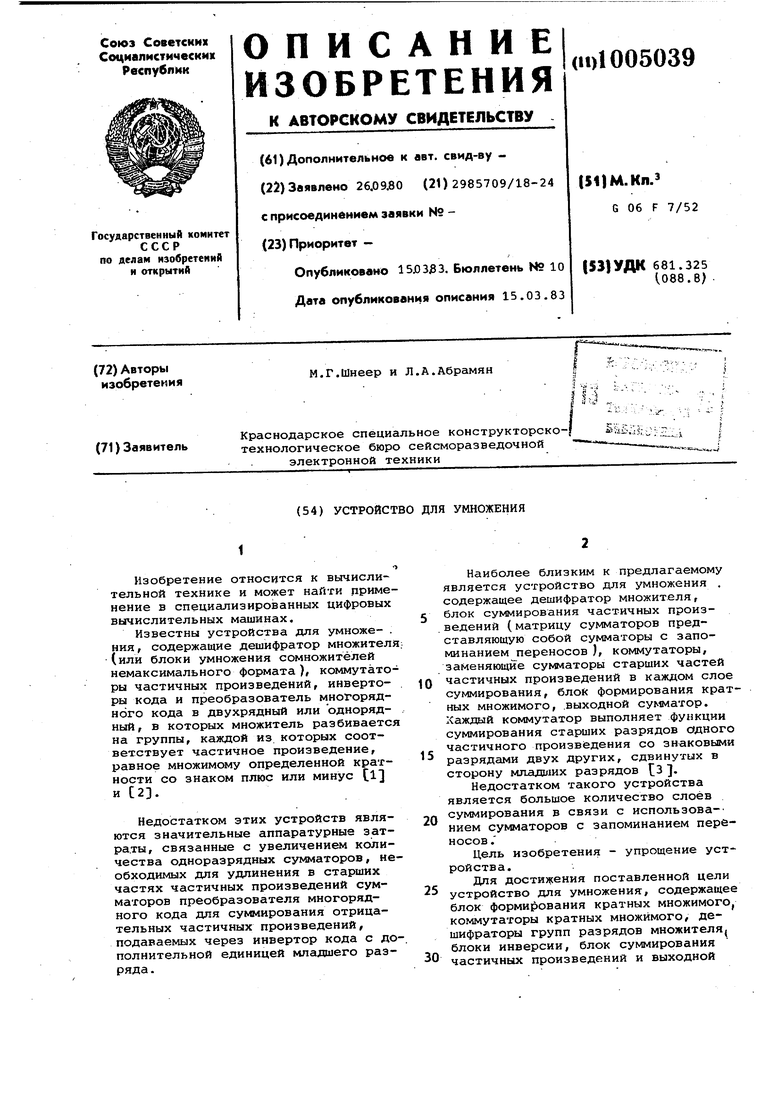

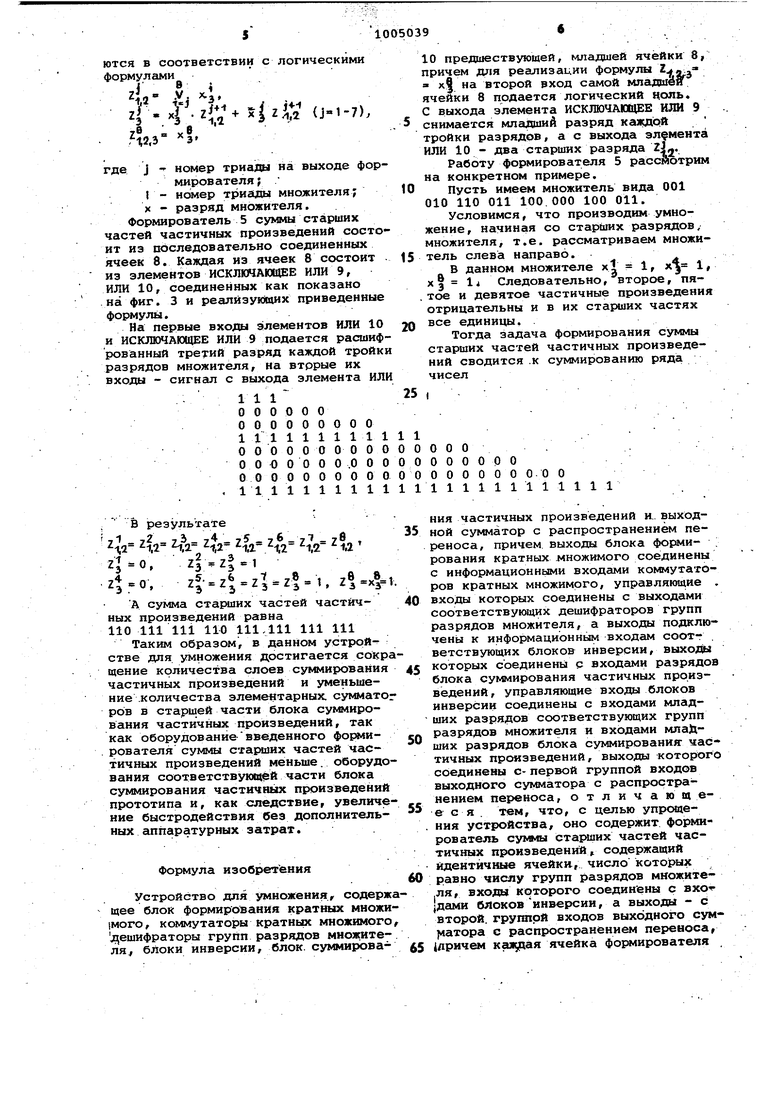

30 частичных произведений и выходной сумматор с распространением переноса, причем выходы блока формировани кратных множимого соединены с инфор мационными входами коммутаторов кратных множимого, управляющие вход которых соединены с выходами- соответствующих дешифраторов групп разрядов множителя, а выходы подключены к информационным входам соответствующих блоков инверсии, выходы (оторых соединены с входами разрядо бЛока суммирования частичных йроизведений, управляющие входы блоков . инверсии соединены с входами гдладших разрядов соответствующих групп разрядов множителя и входами младших разрядов блока суммирования час тичных произведений, выходы которог соединены с первой группой входов выходного сумматора с распространением переноса,содержит формирователь суммы ст-арших частей частичных произведений, содержгичий идентич-ные ячейки, число которых равно чис лу групп множителя, входы которого соединены с входами блоков инверсии а выходы - с второй группой входов -выходного сумматора с распространением переноса, причем каждая ячей ка формирователя суммы старших частей частичных произведений содержит элемент ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ И первые входы которых соединены с соответствующими входами формирователя суммы старших частей частичных произведений, выход элемента ИСКЛЮ-ЧАЩЕЕ ИЛИ соединен с первьви выходо данной ячейки формирователя суммы старших частей частичных произведен.ий, выход элемента ИЛИ соединен с вторым и третьим выходами данной ячейки формирователя суммы старших частей частичных произведений и вто рыми входами элементов ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ следующей старшей ячейки формирователя суммы старших частей частичных произведений. На фиг. 1 показана блок-схема устройства для умножения; на фиг.2 схема формирователя суммы старших частей частичных произведений, на фиг. 3 - схема одной ячейки формирователя суммы старших частей части ных произведений. Устройство содержит дешифраторы групп разрядов 1 множителя,коммутаторы 2 кратных множимого, блоки 3 инверсии, блок 4 суммирования частичных произведений (выполненный в виде, матрицы сумматоров с piacnpoстранением переноса ), формирователь суммы старших частей частичных про.изведений, выходной сумматор б с распространением переноса, формирую щий окончательное произведение, блок 7 формирования кратных множимого . Блок 5 содержит идентичные ячейки 8, число которых равно числу групп разрядов множителя, каждая из ячеек 8 содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и элемент ИЛИ 10. Назначение дешифратора 1 состоит в определении кратности множимого в зависимости от группы разрядов множителя, для которых выбирается частичное произведение. Количество разрядов в группе может быть любым. Рассмотрим работу устройства на примере, использующем алгоритм МакСорли с выборкой частичного произведения из множества 2,4,6,8 в зависимости от тройки разрядов множителя и младшего разряда старшей триады. Дешифратор 1 расшифровывает третий разряд каждой тройки разрядов и посылает сигнал на управляющий вход соответствующего блока 3. Если этот сигнал равен нулю (число положительно), то кратное множимого с соответствующего коммутатора 2 ,проходит через блок 3 в прямом коде на блок 4. Если он равен единице ( число отрицательное), то кратное множимого инвертируется в блоке 3 и в обратном коде поступает на блок 4, а в младший разряд блока 4 добавляется единица для представления числа в дополнительном коде. Блок 4 складывает частичные произведения, сдвинутые на 3 разряда относительно друг друга и имеющие длину, равную длине множимого. CyNwa старших (знаковых ) частей частичных произведений, имеющих неравную длину, кратную трем, формируется формирователем 5. В блоке 4 при двадцатичетырехразрядном множителе суммируются девять частичных произведений, восемь из которых - соответствующие кратные множимого, а девятое - -либо ноль, в случае четности последней триады множителя, либо однократное множимое со знаком минус, обусловленное тем, что при выборе кратных используются только четные числа, а девятое число служит для компенсации избыточности восьмого числа. Сумма девяти частичных произведений поступает на вход сумматора б, где складывается с суммой старших частей частичных прои ведений, поступающей из -формирователя 5 на другой вход сумматора 6. Рассмотрим работу формирователя 5. В зависимости от знака частичного произведения старше разряды могут содержать либо все нули (.плюс), либо все единицы (минус), что соответствует обратному коду старшей части сдвинутого, частичного произведения.It V V Разряды триад Z|, Z |, Z|,(j 1-8) на выходе формирователя 5 формируются в соответствии с логическими формулами

4

У. х,

ь j--7b

2,3° 3

где j - номер триады на выходе формирователя ;

I - нЬмер триашл множителя; X - разряд множителя.

Формирователь 5 суммы старших частей частичных произведений состоит из последовательно соединенных ячеек 8. Каждая из ячеек 8 состоит из элементов ИСКЛЮЧАКХЦЕВ ИЛИ 9, ИЛИ 10, соединенных как показано на фиг. 3 и реалйзукших приведенные формулы.

На первые входы элементов ИЛИ 10 и ИСКЛЮЧАЮЩЕЕ ИЛИ 9 подается расшифрованный третий разряд каждой тройки разрядов множителя, на втррые их входы - сигнал с выхода элемента ИЛИ

..

000000 000000000

1 11 1111111

0000000000 0000000000

о о о о о о о о о а . 1111111111

, в результате

i г|2 4.Z{2 Z5 4 i/T 2«

ZI 0 ,

3 - u, z|- z| z 1 z 1. z x 1

zt 0,

3 , .

A сумма старших частей частичных произведений равна 110 111 111 110 111,111 111 111

Таким образом, в данном устройстве для умножения достигается сокращение количества слоев суммирования частичных произведений и уменьшение .количества элементарных, сумматог ров в старшей части блока суммирования частичных произведений, так как оборудованиевведенного формирователя суммы старших частей частичных произведений меньше. оборудования соответствукяц й части блока суммирования частичных произведений прототипа и, как следствие, увеличение быстродействия без дополиительных аппаратурных затрат.

Формула изобретения

Устройство для умножения, содержащее блок формирования кратных множи)мого, коммутаторы кратньос множимого, л ешифраторы групп разрядов множителя, блоки инверсии, блок, суммирова10 предшествующей, младшей ячейки 8, причем для реализации формулы 3 х§ на второй вход самой младшей, ячейки 8 подается логический цоль. С выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 снимается младшиА разряд каждой тройки разрядов, а с выхода элемента ИЛИ 10 - два старших разряда ZJM.

Работу формирователя 5 рассмотрим на конкретном примере.

Пусть имеем множитель вида 001 010 110 011 100 000 100 011.

Условимся, что производим умножение, начиная со старших разрядов; множителя, т.е. рассматриваем множитель слева направо.

В данном множителе х1 1, х 1, Хз li Следовательно, второе, пятое и девятое частичные произведения отрицательны и в их старших частях все единигда.

Тогда задача формирования суммы старших частей частичных произведений сводится .к суммированию ряда чисел

I

000

000000

0000000.00

111111111111

ния частичных произведений и. выходной сумматор с распространением переноса, причем выходы блока форми- ; рования кратных множимого соединены с информационными входами ко№лутаторов кратных множимого, управляющие .

входы которых соединены с выходами соответствукнцих дешифраторов групп разрядов множителя, а выходы подключены к информационным входам соотг ветствующих блоков инверсии, выход$з1

которых соединены р входами разрядов блока суммирования частичных произведений, управляющие входы блоков инверсии соединены с входами младших разрядов соответствующих групп разрядов множителя и входами млаЛших разрядов блока суммирования- частичных произведений, выходы которого соединены с- первой группой входов выходного сумматора с распространением переноса, отличают ее с я . тем, что, с целью упреадения устройства, оно содержит формирователь старших частей частичных произведений, содержащий идентичные ячейки, число которых

равно числу групп разрядов множителя, входы которого соединены с вхо |дами блоков инверсии, а выходы - с второй, группой входов выходного сум атора с распространением переноса,

1лричем ячейка формирователя .

суммы старших частей частичных произведений содержит элемент ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первые ВХОДЫ которых соединены с соответствующими входами формирователя суммы старших частей частичных произведеннй, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым выходом данной ячейки формирователя суммы старших частей частичных произведений, выход элемента ИЛИ соединен с вторым и третьим выходами данной ячейки формирователя суммы старших частей частичных -произведений и вторыми входами элементов ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ следуюшей с;таршей ячейки формирователя суммы старших частей частичных произведений.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 330450, кл. Q 06 F 7/38, 1970.

2.Патент США № 4041296,

кл. Q 06 F 7/52, опублик. 1977.

.3, Гаврилов Ю.В. и др. Арифметические устройства быстродействующих ЭЦВМ. М., Сов.радио, 1970, с. 148 157 прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1977 |

|

SU695364A1 |

| Устройство для умножения в избыточной системе счисления | 1983 |

|

SU1124286A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для умножения | 1983 |

|

SU1129606A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Устройство для умножения | 1979 |

|

SU842799A1 |

i-n

LH

I

Л 7

/

Х

V t f

f f

I ГП

t

в

4 г ТУ

f f

Авторы

Даты

1983-03-15—Публикация

1980-09-26—Подача