(S) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1501047A1 |

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для умножения | 1987 |

|

SU1501045A1 |

| Матричное устройство для умножения чисел по модулю 2 @ -1 | 1985 |

|

SU1254471A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения по модулю М=2 @ -1 | 1986 |

|

SU1383339A1 |

| Устройство для умножения | 1986 |

|

SU1335983A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Комбинационный сумматор | 1979 |

|

SU800992A1 |

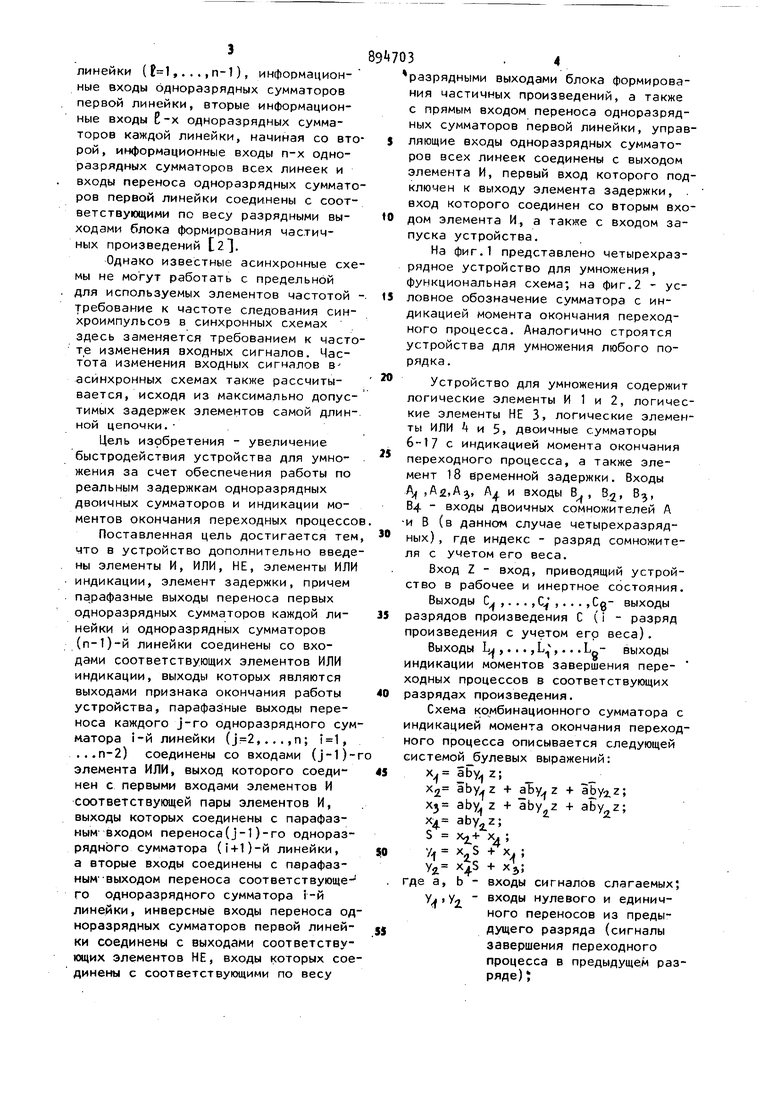

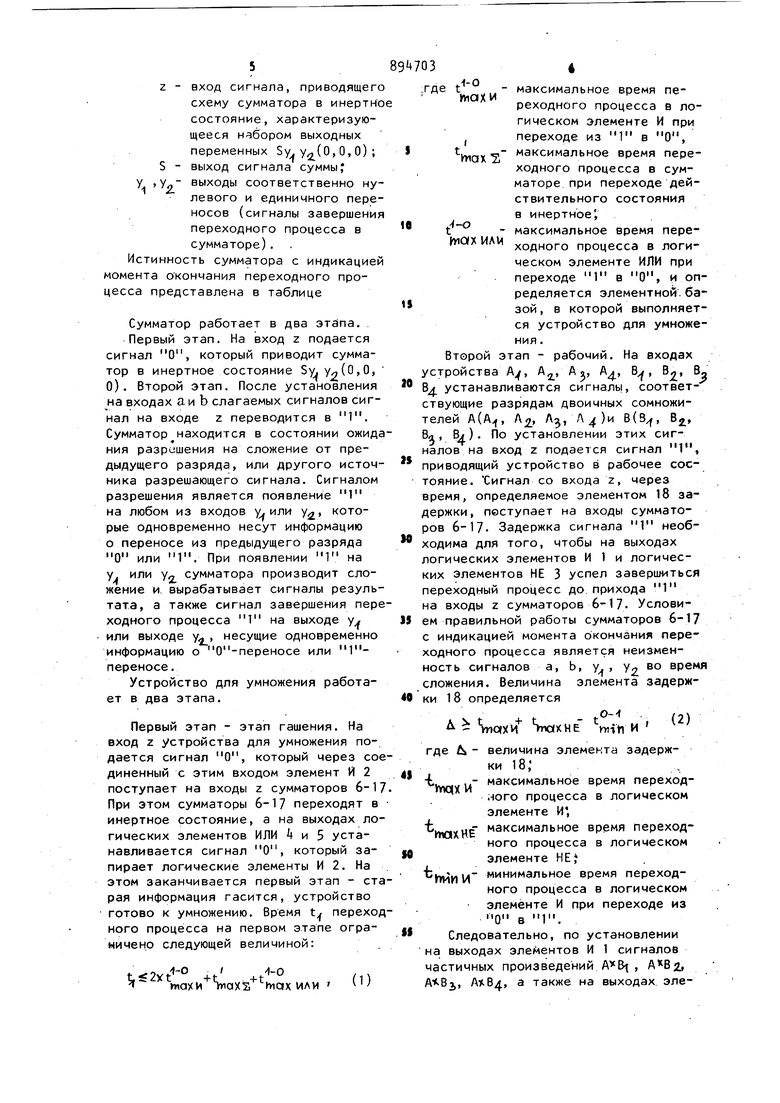

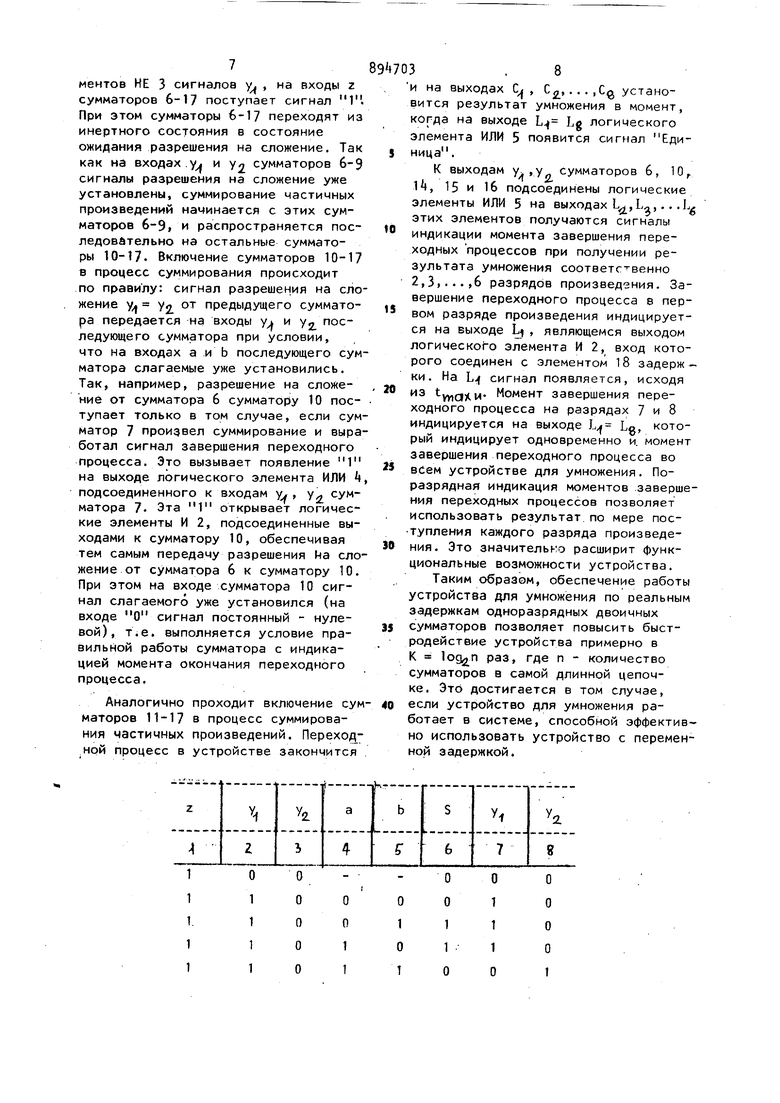

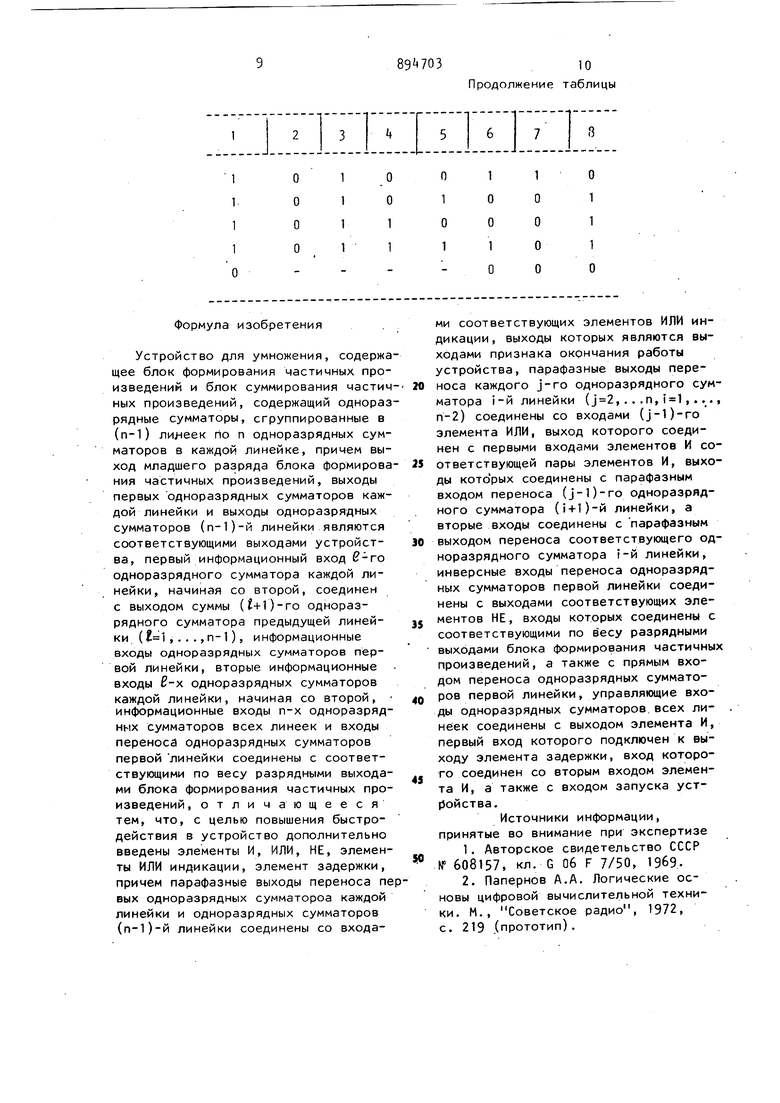

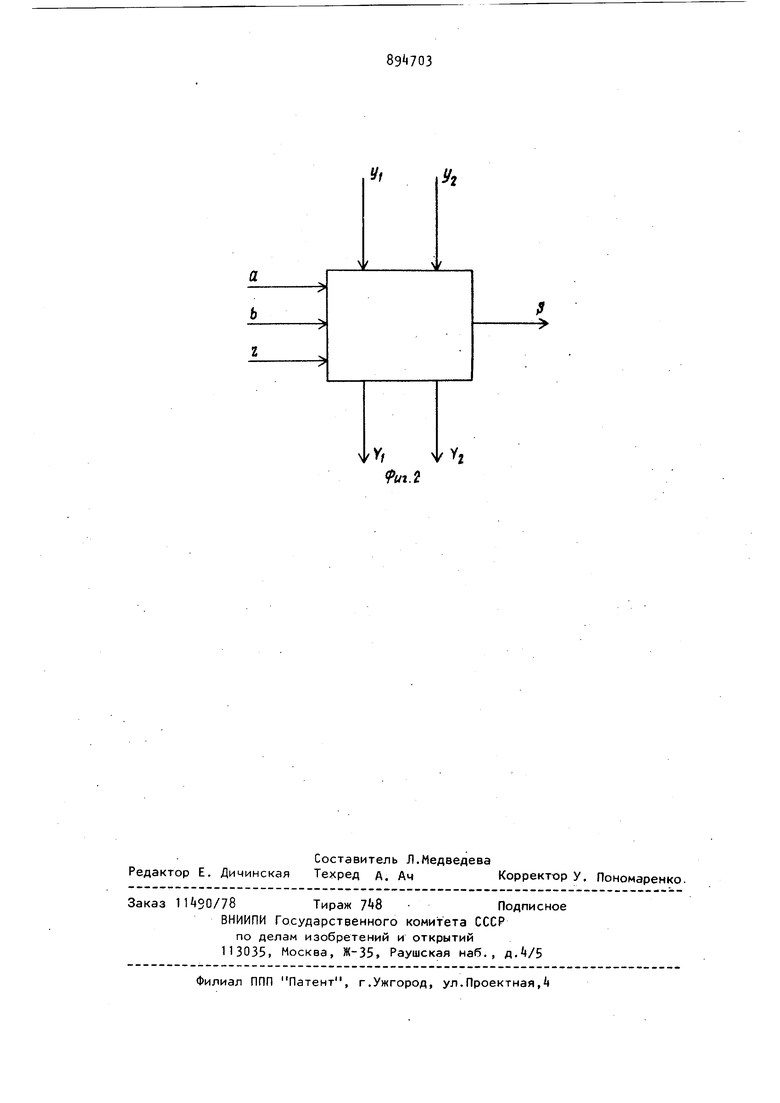

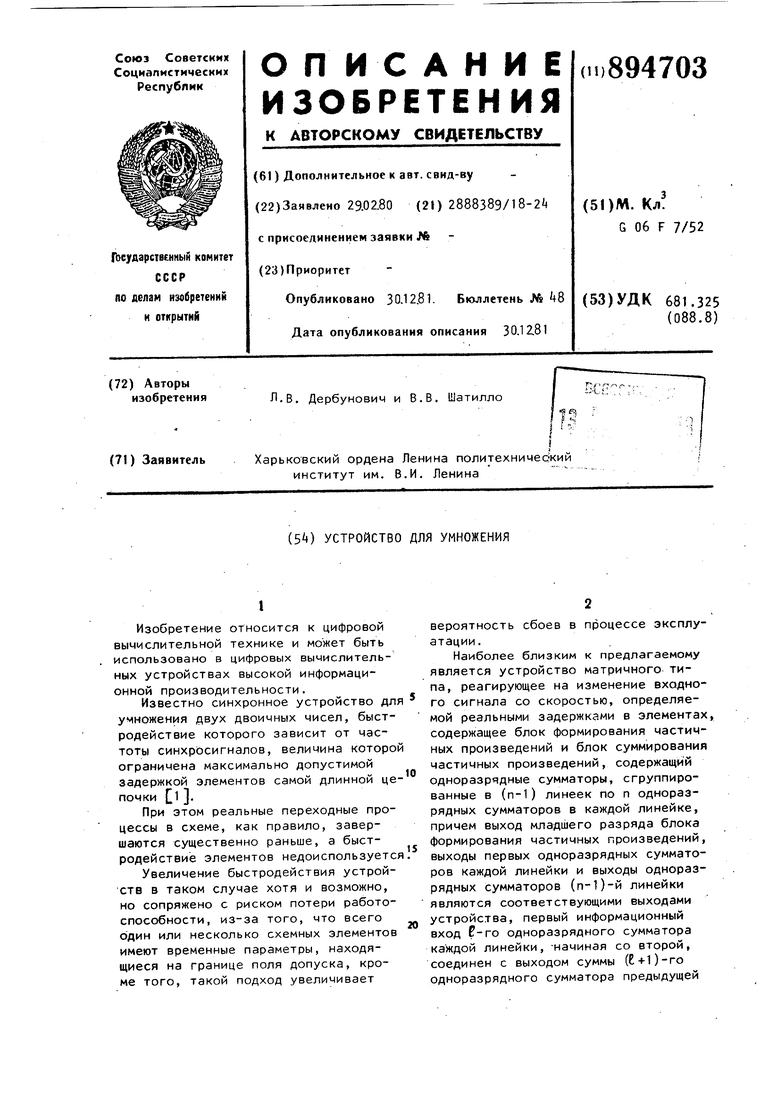

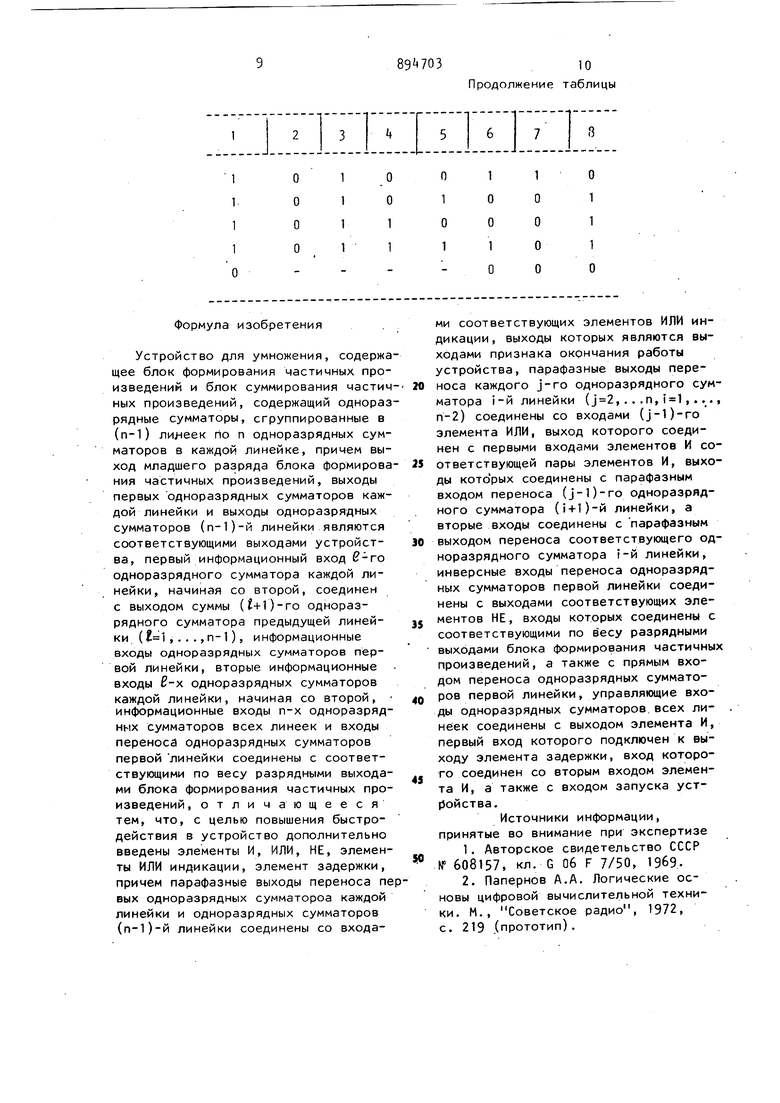

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых вычислительных устройствах высокой информационной производительности. Известно синхронное устройство дл умножения двух двоичных чисел, быстродействие которого зависит от частоты синхросигналов, величина которо ограничена максимально допустимой задержкой элементов самой длинной це почки i . При этом реальные переходные процессы в схеме, как правило, завершаются существенно раньше, а быстродействие элементов недоиспользуетс Увеличение быстродействия устройств в таком случае хотя и возможно, но сопряжено с риском потери работоспособности, из-за того, что всего Ьдин или несколько схемных элементов имеют временные параметры, находящиеся на границе поля допуска, кроме того, такой подход увеличивает вероятность сбоев в процессе эксплуатации . Наиболее близким к предлагаемому является устройство матричного типа, реагирующее на изменение входного сигнала со скоростью, определяемой реальными задержками в элементах, содержащее блок формирования частичных произведений и блок суммирования частичных произведений, содержащий одноразрядные сумматоры, сгруппированные в (п-1) линеек по п одноразрядных сумматоров в каждой линейке, причем выход младшего разряда блока формирования частичных произведений, выходы первых одноразрядных сумматоров каждой линейки и выходы одноразрядных сумматоров (п-1)-й линейки являются соответствующими выходами устройства, первый информационный вход Р-ГО одноразрядного сумматора каждой линейки, -начиная со второй, соединен с выходом суммы (Е+1)-го одноразрядного сумматора предыдущей линейки (1,...,n-1), информационные входы одноразрядных сумматоров первой линейки, вторые информационные входы Е-Х одноразрядных сумматоров каждой линейки, начиная со вто рой, информационные входы п-х одноразрядных сумматоров всех линеек и входы переноса одноразрядных суммато ров первой линейки соединены с соответствующими по весу разрядными выходами блока формирования частичных произведений 2. Однако известные асинхронные схе мы не могут работать с предельной для используемых элементов частотой требование к частоте следования синхроимпульсов в синхронных схемах здесь заменяется требованием к часто те изменения входных сигналов. Частота изменения входных сигналов васинхронных схемах также рассчитывается, исходя из максимально допустимых задержек элементов самой длинной цепочки, Цель изобретения - увеличение быстродействия устройства для умножения за счет обеспечения работы по реальным задержкам одноразрядных двоичных сумматоров и индикации моментов окончания переходных процессо Поставленная цель достигается тем что в устройство дополнительно введе ны элементы И, ИЛИ, НЕ, элементы ИЛИ индикации, элемент задержки, причем парафазные выходы переноса первых одноразрядных сумматоров каждой линейки и одноразрядных сумматоров (п-1)-й линейки соединены со входами соответствующих элементов ИЛИ индикации, выходы которых являются выходами признака окончания работы устройства, парафазные выходы переноса каждого j-ro одноразрядного сум матора i-й линейки (j-2,.,,,n; , ,,.п-2) соединены со входами (j-l) элемента ИЛИ, выход которого соединен с первыми входами элементов И соответствующей пары элементов И, выходы которых соединены с парафазным входом переноса(j-1)-го однораз рядного сумматора (|+1)-й линейки, а вторые входы соединены с парафазным выходом переноса соответствующе го одноразрядного сумматора i-й линейки, инверсные входы переноса о норазрядных сумматоров первой линей ки соединены с выходами соответству ющих элементов НЕ, входы которых со динены с соответствующими по весу 3 .4 разрядными выходами блока формирования частичных произведений, а также с прямым входом переноса одноразрядных сумматоров первой линейки, управляющие входы одноразрядных сумматоров всех линеек соединены с выходом элемента И, первый вход которого подключен к выходу элемента задержки, . вход которого соединен со вторым входом элемента И, а также с входом запуска устройства. На фиг,1 представлено четырехразрядное устройство для умножения, функциональная схема; на фиг,2 - условное обозначение сумматора с индикацией момента окончания переходного процесса. Аналогично строятся устройства для умножения любого порядка. Устройство для умножения содержит логические элементы И 1 и 2, логические элементы НЕ 3, логические элементы ИЛИ t и 5, двоичные сумматоры 6-17 с индикацией момента окончания переходного процесса, а также элемент 18 временной задержки. Входы Af ,A2,A, А и входы В , В, З, В4 - входы двоичных сомножителей А и В (в данном случае четырехразрядных) , где индекс - разряд сомножителя с учетом его веса. Вход Z - вход, приводящий устройство в рабочее и инертное состояния. Выходы Cj ,, , , , , , , , ,Cg- выходы разрядов произведения С (i - разряд произведения с учетом его веса), Выходы L ,..., L,... Lg- выходы индикации моментов завершения переходных процессов в соответствующих разрядах произведения. Схема комбинационного сумматора с индикацией момента окончания переходного процесса описывается следующей системой булевых выражений: -, iby Z + aiby z + aby z + aby,jZ; + Xj, S + X. ; S + Va -f где a, b входы сигналов слагаемых; входы нулевого и единич 4 i ного переносов из предыдущего разряда (сигналы завершения переходного процесса в предыдущем разряде) ; z - вход сигнала, приводящего схему сумматора в инертно состояние, характеризующееся набором выходных переменных Sy. , О, 0) ; S - выход сигнала суммы У Ул выходы соответственно нулевого и единичного переносов (сигналы завершения переходного процесса в сумматоре). . Истинность сумматора с индикацией момента окончания переходного процесса представлена в таблице Сумматор работает в два этйпа. . Первый этап. На вход z подается сигнал О, который приводит сумматор в инертное состояние .О, 0). Второй этап. После установления на входах аи b слагаемых сигналов сигнал на входе z переводится в 1. Сумматор находится в состоянии ожида ния разрешения на сложение от предыдущего разряда, или другого источника разрешающего сигнала. Сигналом разрешения является появление 1 на любом из входов у.или у которые одновременно несут информацию о переносе из предыдущего разряда О или 1. При появлении 1 на у. или УЛ сумматора производит сложение и. вырабатывает сигналы результата, а также сигнал завершения пере ходного процесса 1 на выходе у или выходе у, несущие одновременно информацию о 0 -переносе или 1 переносе. Устройство для умножения работает в два этапа. Первый этап - этап гашения. На вход z устройства для умножения подается сигнал О, который через сое диненный с этим входом элемент И 2 поступает на входы z сумматоров 6-17 При этом сумматоры 6-1 переходят в инертное состояние, а на выходах логических элементов ИЛИ k и S устанавливается сигнал О, который запирает логические элементы И 2. На этом заканчивается первый этап - ста рая информация гасится, устройство готово к умножению. Время t переход ного процесса на первом этапе ограниченр следующей величиной: +С или Vi nn ,где t .. максимальное время переходного процесса в логическом элементе И при , переходе из 1 а О, Кмах 2 м имальное время переходного процесса в сумматоре при переходе действительного состояния в инертное t - максимальное время переhiOX НАМ ходного процесса в логическом элементе ИЛИ при переходе 1 в О, и определяется элементной.базой , в которой выполняется устройство для умножения . Второй этап - рабочий. На входах устройства Ау, А, Aj, А, В, В., В В устанавливаются сигналь, соответствующие разрядам двоичных сомножителей А(А, А, А, А)и В(В, Bj, В/1, BJ). По установлении этих сигналов на вход z подается сигнал 1, приводящий устройство в рабочее состояние. Сигнал со входа Z, через время, определяемое элементом 18 задержки, поступает на входы сумматоров 6-17. Задержка сигнала 1 необходима для того, чтобы на выходах логических элементов И 1 и логических элементов НЕ 3 успел завершиться переходный процесс до.прихода 1 на входы z сумматоров 6-17. Условием правильной работы сумматоров 6-17 с индикацией момента окончания пере ходного процесса является неизменность сигналов а, Ь, у , У2 во время сложения. Величина элемента задержки 18 определяется Д VidXH ЧПОКНЕ и и где - величина элемента задержки 18; t - максимальное время переходного процесса в логическом элементе И; fnaxHE максимальное время переходного процесса в логическом элементе НЕ hMHH имальное время переходного процесса в логическом элементе И при переходе из О в 1. Следовательно, по установлении на выходах элементов И 1 сигналов частичных произведений , , А.В2,, , а также на выходах, элементов НЕ 3 сигналов , на входы z сумматоров 6-17 поступает сигнал 1. При этом сумматоры 6-17 переходят из инертного состояния в состояние ожидания разрешения на сложение. Так как на входах.уJ и У2 сумматоров 6-9 сигналы разрешения на сложение уже установлены, суммирование частичных произведений начинается с этих сумматоров 6-9, и распространяется последовательно на остальные сумматоры 10-17. Включение сумматоров 10-17 в процесс суммирования происходит по правилу: сигнал разрешения на сло жение у У2 от предыдущего сумматора передается на входы у и yg последующего сумматора при условии, что на входах а и b последующего сум матора слагаемые уже установились. Так, например, разрешение на сложение от сумматора 6 сумматору 10 поступает только в том случае, если сум матор 7 произвел суммирование и выра ботал сигнал завершения переходкого процесса. Это вызывает появление 1 на выходе логического элемента ИЛИ подсоединенного к входам у , -, сумматора 7. Эта 1 открывает логические элементы И 2, подсоединенные выходами к сумматору 10, обеспечивая тем самым передачу разрешения Иа сло жение от сумматора 6 к сумматору 10. При этом на входе сумматора 10 сигнал слагаемого уже установился (на входе О сигнал постоянный - нулевой), т.е. выполняется условие правильной работы сумматора с индикацией момента окончания переходного процесса. Аналогично проходит включение сум маторов 11-17 в процесс суммирования частичных произведений. Переходной процесс в устройстве закончится и на выходах С , С,... ,Cg установится результат умножения в момент, когда на выходе L Lg логического элемента ИЛИ 5 появится сигнал Единица. К выходам ,, сумматоров 6, 10 1, 15 и 16 подсоединены логические элементы ИЛИ 5 на выходах L.,L,.. .L этих элементов получаются сигналы индикации момента завершения переходных процессов при получении результата умножения соответс- венно 2,3,..,6 разрядов произведения. Завершение переходного процесса в первом разряде произведения индицируется на выходе Lj , являющемся выходом логического элемента И 2, вход которого соединен с элементом 18 задержки. На L сигнал появляется, исходя из tyy,g,l;,. Момент завершения переходного процесса на разрядах 7 и 8 индицируется на выходе Ц LQ, который индицирует одновременно и. момент завершения переходного процесса во всем устройстве для умножения. Поразрядная индикация моментов .завершения переходных процессов позволяет использовать результат по мере поступления каждого разряда произведения. Это значительно расширит функциональные возможности устройства. Таким образом, обеспечение работы устройства для умножения по реальным задержкам одноразрядных двоичных сумматоров позволяет повысить быстродействие устройства примерно в К раз, где п - количество сумматоров в самой длинной цепочке. Это достигается в том случае, если устройство для умножения работает в системе, способной эффективно использовать устройство с переменной задержкой.

1

Формула изобретения

Устройство для умножения, содержащее блок формирования частичных произведений и блок суммирования частичных произведений, содержащий одноразрядные сумматоры, сгруппированные в (п-1) лияеек по п одноразрядных сумматоров в каждой линейке, причем выход младшего разряда блока формирования частичных произведений, выходы первых одноразрядных сумматоров каждой линейки и выходы одноразрядных сумматоров (п-1)-и линейки являются соответствующими выходами устройства, первый информационный вход S-ro одноразрядного сумматора каждой линейки, начиная со второй, соединен с выходом суммы (t+l)-ro одноразрядного сумматора предыдущей линейки (1,.,.,п-1), информационные входы одноразрядных сумматоров первой линейки, вторые информационные входы -х одноразрядных сумматоров каждой линейки, начиная со второй, информационные входы п-х одноразрядных сумматоров всех линеек и входы переноса одноразрядных сумматоров первой линейки соединены с соответствующими по весу разрядными выходами блока формирования частичных произведений, отличающееся тем, что, с целью повышения быстродействия в устройство дополнительно введены элементы И, ИЛИ, НЕ, элементы ИЛИ индикации, элемент задержки, причем парафазные выходы переноса певых одноразрядных сумматороа каждой линейки и одноразрядных сумматоров (п-1)-й линейки соединены со входа89 70310

Продолжение таблицы

ми соответствующих элементов ИЛИ индикации, выходы которых являются выходами признака окончания работы устройства, парафазные выходы переноса каждого j-ro одноразрядного сумматора i-й линейки (, .. .п, 1,..., п-2) соединены со входами (j-l)-ro элемента ИЛИ, выход которого соединен с первыми входами элементов И соответствующей пары элементов И, выходы которых соединены с парафазным входом переноса (j-1)-го одноразрядного сумматора (1+1)-й линейки, а вторые входы соединены с парафаэным выходом переноса соответствующего одноразрядного сумматора 1-й линейки, инверсные входы переноса одноразрядных сумматоров первой линейки соединены с выходами соответствующих элементов НЕ, входы которых соединены с соответствующими по весу разрядными выходами блока формирования частичных произведений, а также с прямым входом переноса одноразрядных сумматоров первой линейки, управляющие входы одноразрядных сумматоров.всех линеек соединены с выходом элемента И, первый вход которого подключен к выходу элемента задержки, вход которого соединен со вторым входом элемента И, а также с входом запуска уст0ойства,

Источники информации, принятые во внимание при экспертизе

с. 219 (прототип) . 61 .m

2

У -

фУ|Гф Y2

W7.2

Авторы

Даты

1981-12-30—Публикация

1980-02-29—Подача