ном поступлении сомножителей. Это достигается в устройстве, содержащем матрицу 1 элементов 3 И, входы и выходы которых соединены соответственно с прямыми входами разрядов сомножителей и прямыми выходами разрядов частичных произведений, и матрицу из п (п-1) сумматоров 5 16, введением матрицы 2 элементов ИЛИ 4, входы и

1

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах высоко производительности.

Цель изобретения - расширение области применения за счет получения инверсного значения результата при парафазном поступлении сомножителей.

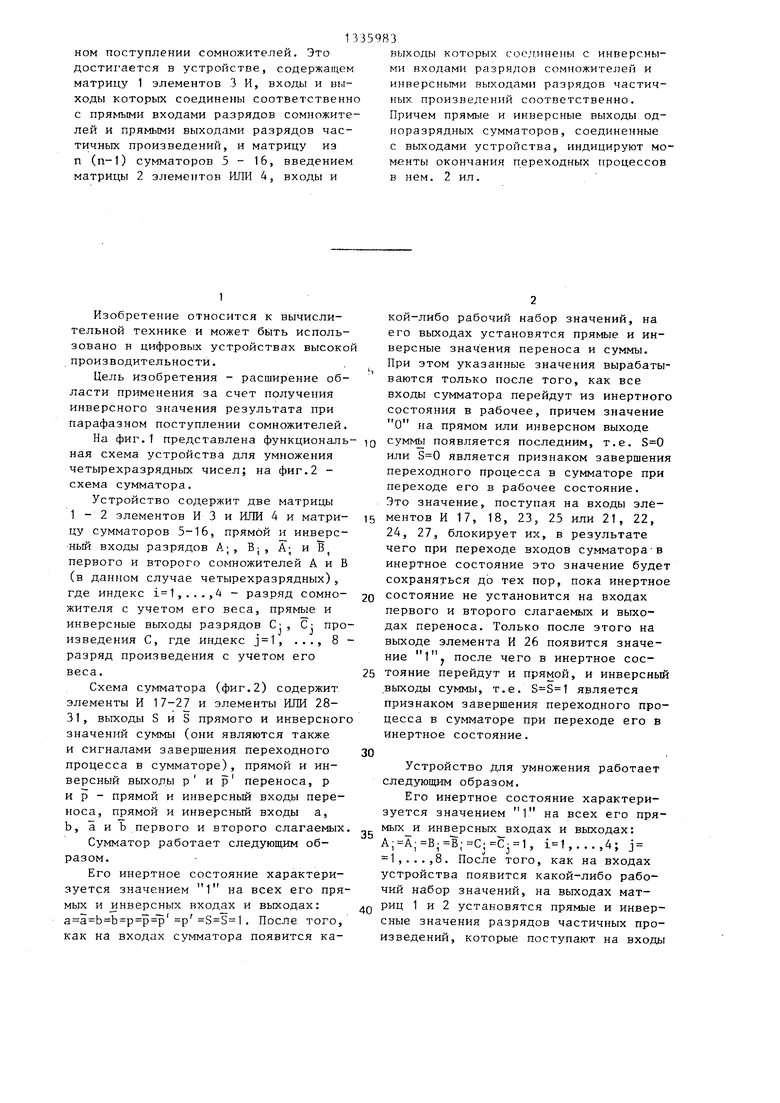

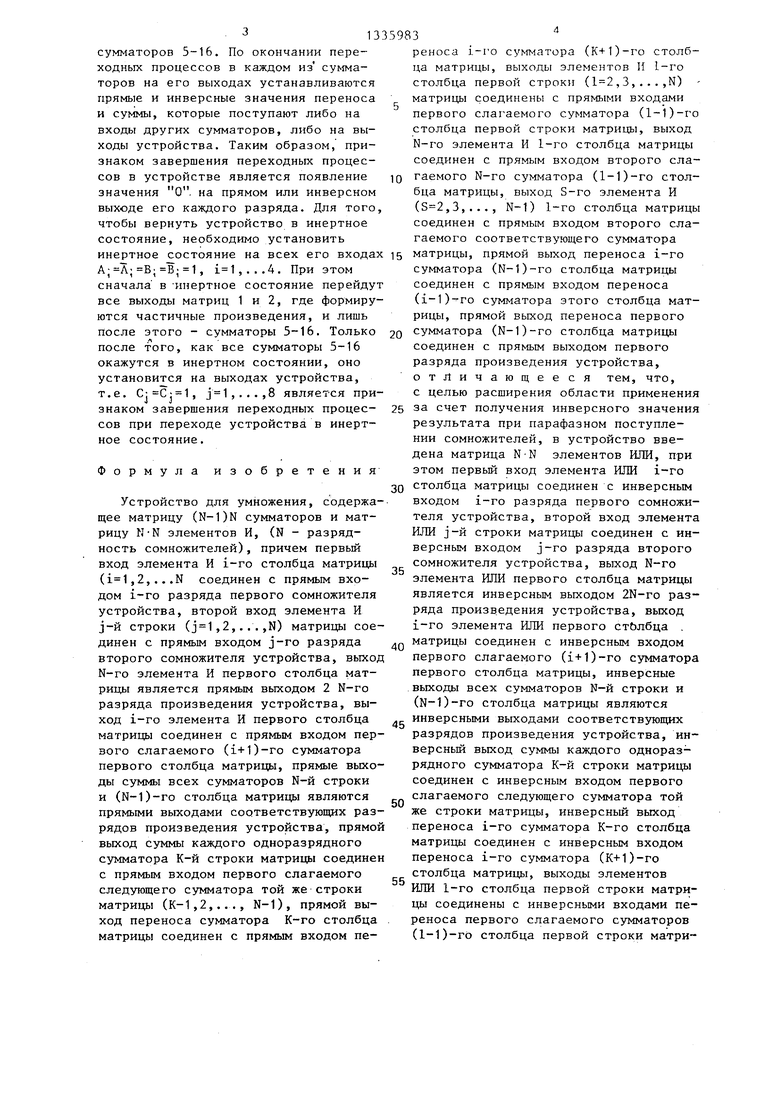

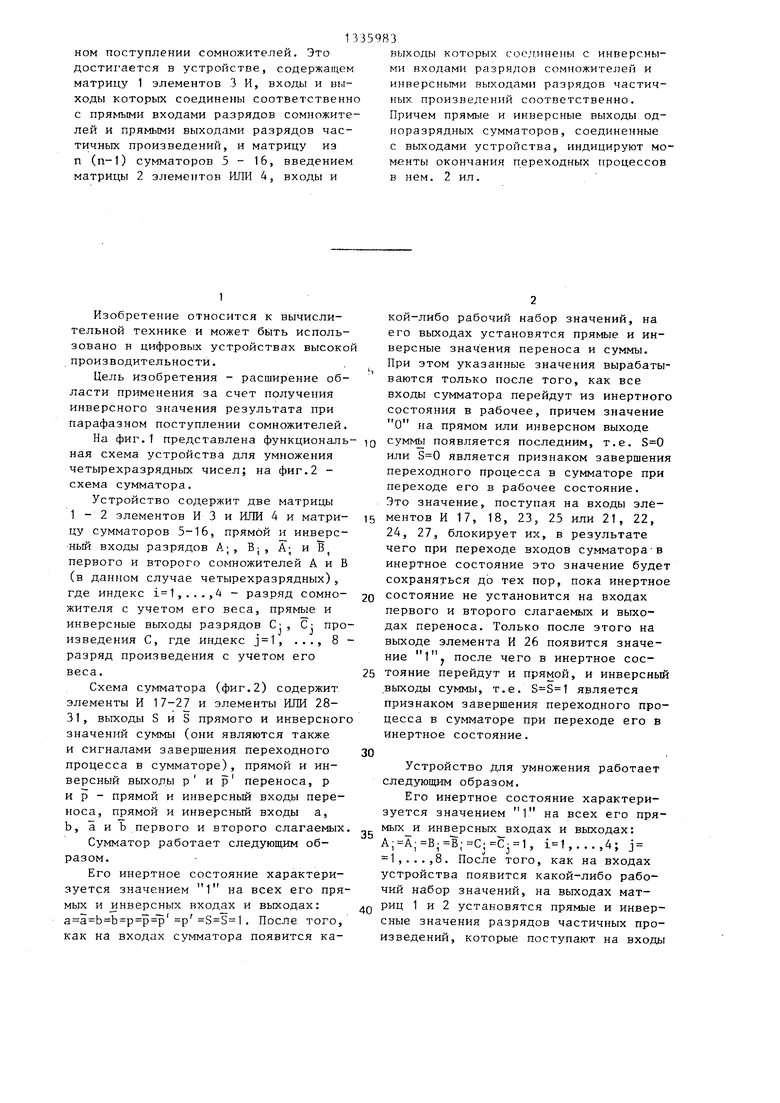

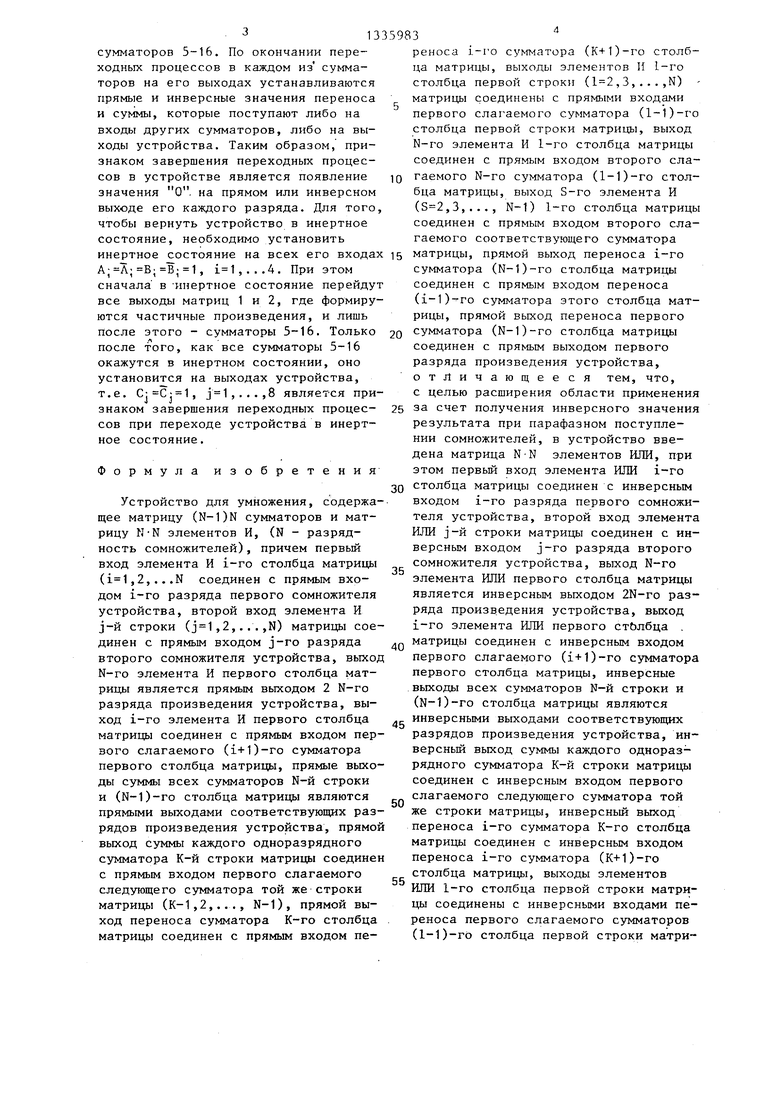

На фиг,1 представлена функциональ мая схема устройства для умножения четырехразрядных чисел; на фиг,2 - схема сумматора.

Устройство содержит две матрицы 1 - 2 элементов И 3 и ИЛИ 4 и матри- цу сумматоров 5-16, прямой и инверс- -ный входы разрядов А;, Bj, А; и В первого и второго сомножителей А и В (в данном случае четырехразрядных), где индекс ,,.,,4 - разряд сомно- жителя с учетом его веса, прямые и инверсные выходы разрядов С , С: произведения С, где индекс , , 8 разряд произведения с учетом его веса,

Схема сумматора (фиг,2) содержит элементы И 17-27 и элементы ИЛИ 28- 31, выходы S и S прямого и инверсног значений суммы (они являются также и сигналами завершения переходного процесса в сумматоре), прямой и инверсный выходы р и р переноса, р и р - прямой и инверсный входы переноса, прямой и инверсный входы а, Ь, а и b первого и второго слагаемых

Сумматор работает следующим образом.

Его инертное состояние характеризуется значением 1 на всех его прямых и инверсных входах и выходах: . После того, как на входах сумматора появится кавыходы которых сое;г,инены с инверсными входами разрядов сомножителей и инверсными выходами разрядов частичных произведений соответственно. Причем прямые и инверсные выходы одноразрядных сумматоров, соединенные с выходами устроР1ства, индицируют моменты окончания переходных процессов в нем. 2 ил.

кой-либо рабочий набор значений, на его выходах установятся прямые и инверсные значения переноса и суммы. При этом указанные значения вырабатываются только после того, как все входы сумматора перейдут из инертного состояния в рабочее, причем значение О на прямом или инверсном выходе сум№1 появляется последним, т,е, или является признаком завершения переходного процесса в сумматоре при переходе его в рабочее состояние. Это значение, поступая на входы элементов И 17, 18, 23., 25 или 21, 22, 24, 27, блокирует их, в результате чего при переходе входов сумматора-в инертное состояние это значение будет сохраняться до тех пор, пока инертное состояние не установится на входах первого и второго слагаемых и выходах переноса. Только после этого на выходе элемента И 26 появится значение 1 после чего в инертное состояние перейдут и прямой, и инверсный выходы суммы, т,8, является признаком завершения переходного процесса в сумматоре при переходе его в инертное состояние.

Устройство для умножения работает следующим образом.

Его инертное состояние характеризуется значением 1 на всех его пря- инверсных входах и выходах: ..I, ,,,,,4; j 1,,,,,8, После того, как на входах устройства появится какой-либо рабочий набор значений, на выходах матриц 1 и 2 установятся прямь:е и инверсные значения разрядов частичных произведений, которые поступают на входы

сумматоров 5-16. По окончании переходных процессов в каждом из сумматоров на его выходах устанавливаются прямые и инверсные значения переноса и суммы, которые поступают либо на входы других сумматоров, либо на выходы устройства. Таким образом, признаком завершения переходных процессов в устройстве является появление значения О, на прямом или инверсном выходе его каждого разряда. Для того, чтобы вернуть устройство в инертное состояние, необходимо установить инертное состояние на всех его входах

, ,... 4. При ЭТОМ

сначала в инертное состояние перейдут все выходы матриц 1 и 2, где формируются частичные произведения, и лишь после этого - сумматоры 5-16. Только после того, как все сумматоры 5-16 окажутся в инертном состоянии, оно установится на выходах устройства, т.е. , ,...,8 является признаком завершения переходных процессов при переходе устройства в инертное состояние.

Формула изобретения

Устройство для умножения, содержащее матрицу (N-1)N сумматоров и матрицу N N элементов И, (N - разрядность сомножителей), причем первый вход элемента И i-ro столбца матрицы (,2,.,.N соединен с прямым входом i-ro разряда первого сомножителя устройства, второй вход элемента И j-й строки (,2,...,N) матрицы соединен с прямым входом j-ro разряда второго сомножителя устройства, выход N-ro элемента И первого столбца матрицы является прямым ВЬЕСОДОМ 2 N-ro разряда произведения устройства, выход i-ro элемента И первого столбца матрицы соединен с прямым входом первого слагаемого (i+1)-ro сумматора первого столбца матрицы, прямые выходы суммы всех сумматоров N-й строки и (N-l)-ro столбца матрицы являются прямыми выходами соответствующих разрядов произведения устройства, прямой выход суммы каждого одноразрядного сумматора К-й строки матрицы соединен с прямым входом первого слагаемого следующего сумматора той же строки матрицы (К-1,2,..., N-1), прямой выход переноса сумматора К-го столбца матрицы соединен с прямым входом пе

5

0

5

реноса 1-го cyNfMaropa (K-t-l)-ro столбца матрицы, выходы элементов И 1-го столбца первой строки (,3,...,N) матрицы соединены с прямыми входами первого слагаемого сумматора (1-1)-го столбца первой строки матрицы, выход N-ro элемента И 1-го столбца матрицы соединен с прямым входом второго слагаемого N-ro сумматора (1-1)-го столбца матрицы, выход S-ro элемента И (,3,..., N-1) 1-го столбца матрицы соединен с прямым входом второго слагаемого соответствующего сумматора матрицы, прямой выход переноса i-ro сумматора (N-l)-ro столбца матрицы соединен с прямым входом переноса (i-1)ro сумматора этого столбца матрицы, прямой выход переноса первого сумматора (N-l)-ro столбца матрицы соединен с прямым выходом первого разряда произведения устройства, отличающееся тем, что, с целью расширения области применения за счет получения инверсного значения результата при парафазном поступлении сомножителей, в устройство введена матрица N N элементов ШШ, при этом первьй вход элемента ИЛИ i-ro столбца матрицы соединен с инверсным входом i-ro разряда первого сомножителя устройства, второй вход элемента ИЛИ j-й строки матрицы соединен с инверсным входом j-ro разряда второго сомножителя устройства, выход N-ro элемента ИЛИ первого столбца матрицы является инверсным выходом 2N-ro разряда произведения устройства, выход i-ro элемента ШШ первого стЬлбда .

„ матрицы соединен с инверсным входом первого слагаемого (i+1)-ro сумматора первого столбца матрицы, инверсные выходы всех сумматоров N-и строки и (N-l)-ro столбца матрицы являются

инверсными выходами соответствующих разрядов произведения устройства, инверсный выход суммы каждого однораз - рядного сумматора К-й строки матрицы соединен с инверсным входом первого слагаемого следующего сумматора той же строки матрицы, инверсный выход переноса i-ro сумматора К-го столбца матрицы соединен с инверсным входом переноса i-ro сумматора (К+1)-го столбца матрицы, выходы элементов ИЛИ 1-го столбца первой строки матрицы соединены с инверсными входами переноса первого слагаемого сумматоров (1-1)-го столбца первой строки матри0

5

0

5

цы, выход N-ro элемента ИЛИ 1-го столбца матрицы соединен с инверсным входом второго слагаемого N-ro сумматора (1-1)-го столбца матрицы, выход S-ro элемента ИЛИ 1-го столбца матрицы соединен с инверсным входом второго слагаемого соответствующего сумматора матрицы, инверсный выход переноса i-ro сумматора (N-l)-ro столбца матрицы соединен с инверсным входом переноса (i-l)-ro сумматора этого столбца матрицы, инверсный выход переноса первого сумматора (N-l)-ro столбца матрицы соединен с инверсным входом первого ра:зряда произведения устройства, причем в состав каждого сумматора матрицы входят одиннадцать элементов И и четыре элемента ИЛИ, прямой вход первого слагаемого сумматора соединен с первыми входами первого, второго, третьего, четвертого и пятого элементов И, инверсный вход первого слагаемого сумматора соединен с первыми входами шестого, седьмого, восьмого и девятого и вторым входом третьего элементов И, прямой вход второго слагаемого сумматора соединен с вторыми входами второго, четвертого, шестого и девятого и третьим входом третьего элементов И, инверсный вход второго слагаемого сумматора соединен с вторыми входами первого, пятого, седьмого и восьмого и четвертым входом третьего элементов И, прямой вход переноса сумматора соединен с первым входом десятого и с третьими входами второго, пятого и девятого элементов И, инверсный вход переноса сумматора соединен с первым входом одиннадцатого и третьи10

15

20

1335983

ми входами первого, шестого и восьмого элементов И, выход первог о элемента И соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены с выходом шестого элемента И, выход седьмого элемента И соединен с третьим входом первого элемента ИЛИ, выход которого соединен с вторым входом десятого и пятым входом третьего элементов И и является инверсным выходом переноса сумматора, выходы второго и десятого элементов И соединены с третьим и четвертым входами второго элемента ИЛИ, выход которого соединен с третьим входом десятого и четвертыми входами первого, второго и шестого элементов И и является прямым выходом суммы сумматора, выход девятого элемента И соединен с первыми входами третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходом пятого элемента И, четвертый 25 вход которого соединен с четвертыми входами восьмого и девятого элементов И, с выходом четвертого элемента ИЛИ, вторым входом одиннадцатого элемента -И и является инверсным выходом суммы сумматора, выход четвертого элемента И соединен с третьим входом третьего элемента ИЛИ, выход которого является прямым выходом переноса сумматора и соединен с третьим входом одиннадцатого и шестым входом третьего элемента И, выход которого соединен с пятым-входом второго и третьим входом четвертого элементов ИЛИ, четвертый и пятый входы которого соединены с выходами восьмого и одиннадцатого элементов И соответственно.

30

35

40

Редактор Н.Егорова

Составитель Н.Мар келова

Техред М.Ходанич Корректор Л.Пилипенко

Заказ 4048/43Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полигргфическое предприятие, г. Ужгород, ул. Проектная, 4

О О О О О О

«i44ii i xiQ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство вычисления сумм произведений | 1990 |

|

SU1718216A1 |

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

| Устройство для умножения | 1980 |

|

SU1001803A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах высокой производительности. Целью изобретения является расширение области применения за счет получения инверсного значения результата при парафаз-. ос, ос, (Л САЭ DO Сд СО 00 00

| Устройство для умножения | 1980 |

|

SU894703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Г /г Л, АЛ Папернов А.А | |||

| Логические основы ЦВТ | |||

| М.: Советское радио, 1972, с.219, рис.9. | |||

Авторы

Даты

1987-09-07—Публикация

1986-04-07—Подача