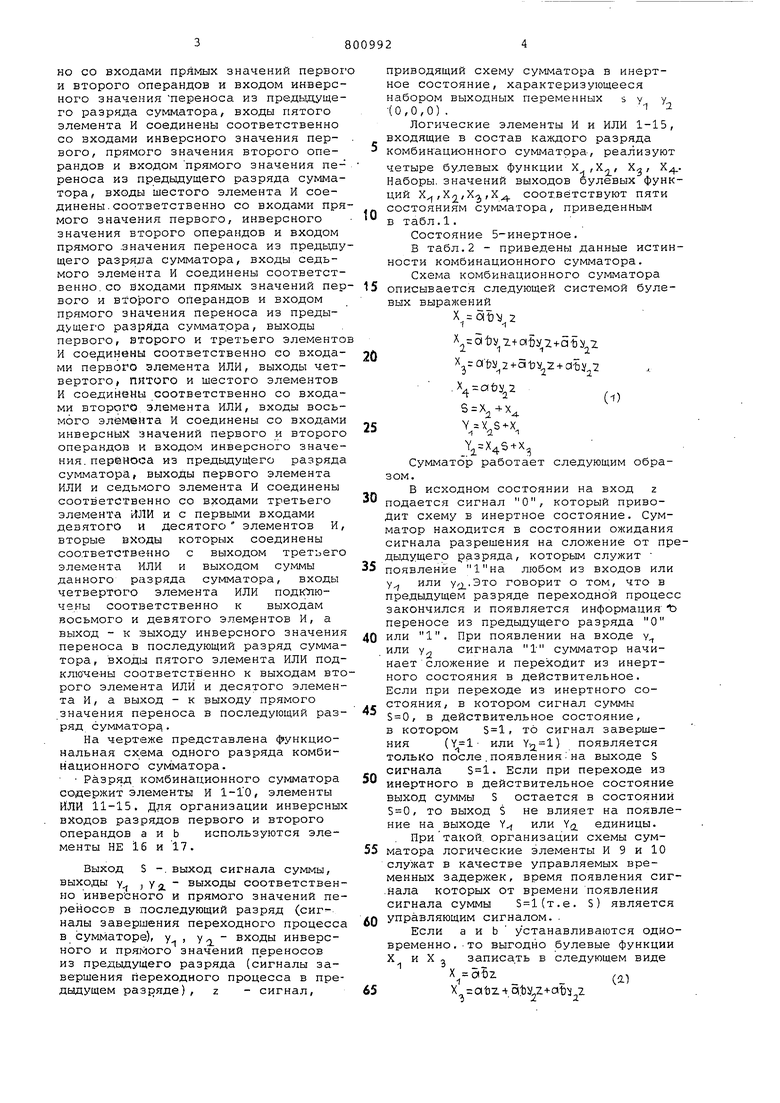

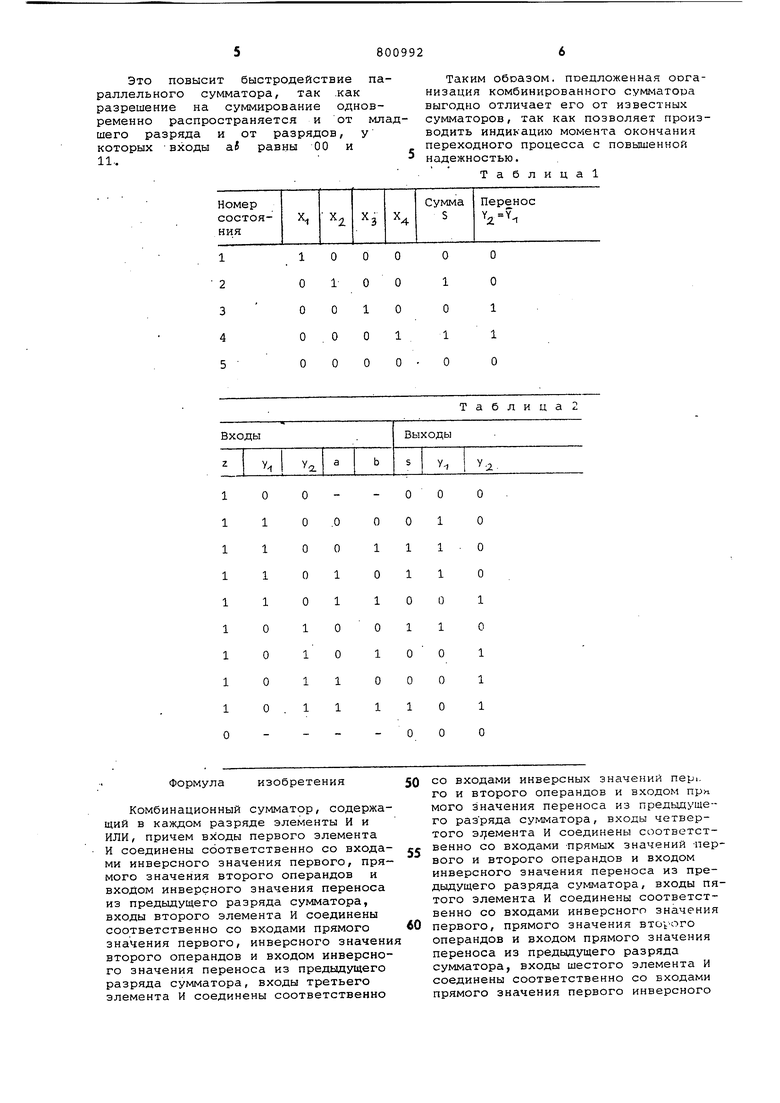

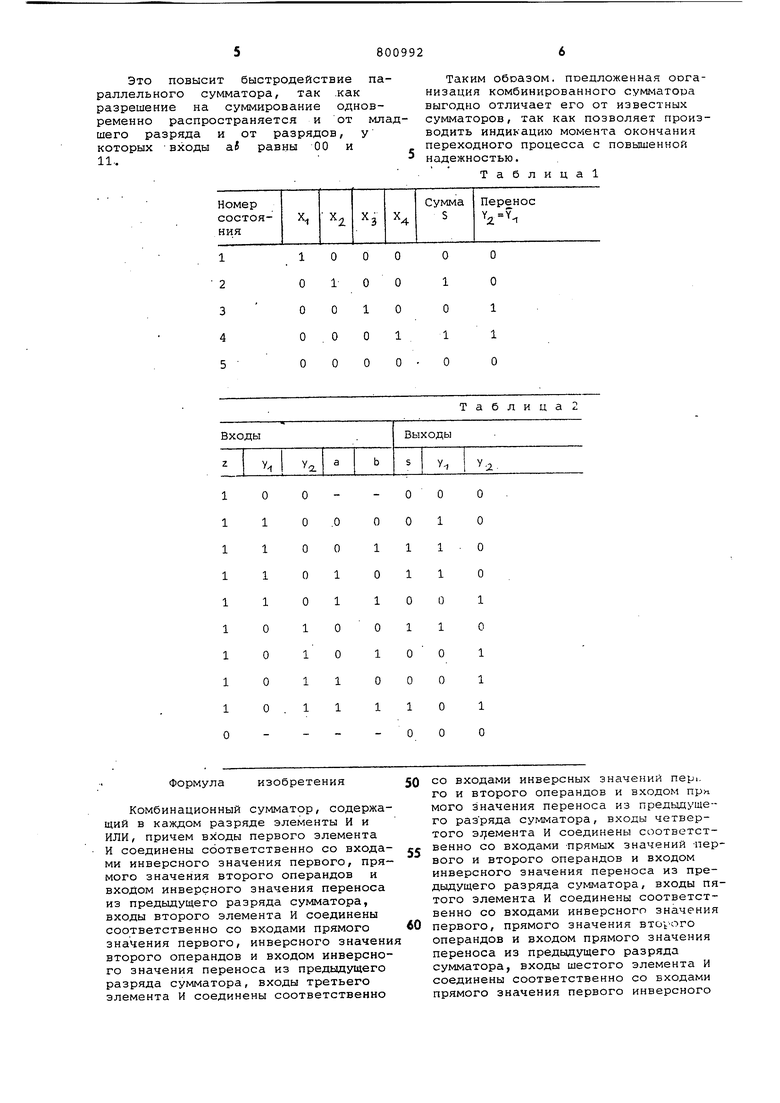

Изобретение относится к цифровой вычислительной технике и может бьзть использовано в цифровых вычислительных устройствах высокой ИЕ1формационной лроиэводительности. Известны различные сумматоры, у. которых увеличиние быстродействия достигается за счет обеспечения работы по реальным задержкам и индикации моментов окончания переходных процессов. Например, асинхронный сум матор, выполненный на триггерах 1 Существенным недостатком данного сумматора является то, что один разряд сумматора эквивалентен по быстро действию 7-8-уровневой комбинационно схеме, так как задержка триггера в 2-3 раза больше задерх ки логических элементов. Наиболее близким по технической сущности к предлагаемому является комбинационный сумматор,содержащий в каждом разряде элементы И и ИЛИ и реализующий с помощью четырех элемен тов И и одного элемента ИЛИ логическую функцию суммы данного разряда сумматора и с помощью других четырех элементов И и одного элемента ИЛИ логическую функцию переноса в последующий разряд сумматора Г2 Недостатком такого сумматора является малая надежность при использовании его в асинхронном режиме, так как сигнал завершения переходного процесса может появляться раньше сигнала на выходе суммы. Цель изобретения - устранение этого недостатка, т.е. повышение его надежности. Для достижения поставленной цели в комбинационном сумматоре, содержащем в каждом разряде элементы И и ИЛИ, причем входы первого элемента И сое-динены соответственно со входами инверсного значения первого, прямого значения второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы второго элемента И соединены соответственно со входами прямого значения первого, инверсного значения второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы третьего элемента И соединены соответственно со входами инверсных значений первого и второго операндов и входом прямого значения переноса из предыдущего разряда сумматора, входы четвертого элемента И соединены соответственно со входами прямых значений первог и второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы пятого элемента И соединены соответственно со входами инверсного значения первого, прямого значения второго операндов и входом прямого значения переноса из предыдущего разряда сумматора, входы шестого элемента И соединены, соответственно со входами пря мого значения первого, инверсного значения второго операндов и входом прямого .значения переноса из предыду щего разряда сумматора, входы седьмого элемента И соединены соответственно, со йходами прямых значений пер вого и второго операндов и входом пряшого значения переноса из предыдущего разряда сумматора, выходы первого, второго и третьего элементо И соеринены соответственно со входами первого элемента ИЛИ, выходы четвертого, пятого и шестого элементов И соединены соответственно со входами второго элемента ИЛИ, входы восьмого элемента И соединены со входами инверсных значений первого и второго операндов и входом инверсного значения, переноса из предыду14его разряда сумматора, выходы первого элемента ИЛИ и седьмого элемента И соединены соответственно со входами третьего элемента ЛЛК и с первьоми входами девятого и десятого элементов И, вторые входы которых соединены соответстве-нно с выходом третьего элемента ИЛИ и выходом суммы данного разряда сумматора, входы четвертого элемента ИЛИ ПОДК ЕЮчены соответственно к выходам восьмого и девятого элементов И, а выход - к выходу инверсного значения переноса в последующий разряд сумматора, входы пятого элемента ИЛИ подключе-ны соответственно к выходам вто рого элемента ИЛИ и десятого элемента И , а ВЫ.ХОД - к выходу прямого значения переноса в последующий разряд сумматораНа чертеже представлена функциональная схема одного разряда комбинационного сумматора. Разряд комбинационного сумматора содержит элементы И l-1O, элементы ИЛИ 11-15. Для организации инверсных входов разрядов первого и второго операндов а и b используются элементы НЕ 16 и 17. Выход S -. выход сигнала суммы, выходы , Y 3. выходы соответственно инверсного и прямого значений переносов в последующий разряд (сигналы завершения переходного процесса в сумматоре), у , у - входы инверсного и прямого значений переносов из предыдущего разряда (сигналы завершения переходного процесса в предыдущем разряде), Z - сигнал, приводящий схему сумматора в инертное состояние, характеризующееся набором выходных переменных s у у (0,0,0).1 Логические элементы И и ИЛИ 1-15, входящие в состав каждого разряда комбинационного сумматора, реализуют четыре булевых функции X ,Х, Х, Х. Наборы, значений выходов булевых функций Х,Х2,Х2,,Х соответствуют пяти состояниям сумматора, приведенным в табл.1. Состояние 5-инертное. В табл.2 - приведены данные истинности комбинационного сумматора. Схема комбинационного сумматора описывается следующей системой булевых выражений X oit) 2 Ч 1 , 51 v 7. + а 5у 2-н а t i/ 2 X :afe / 2-i-a-bv 2 + ati 2 a2 4 Сумматор работает следующим образом. В исходном состоянии на вход z подается сигнал О, который приводит схему в инертное состояние. Сумматор находится в состоянии ожидания сигнала разрешения на сложение от предыдущего разряда, которым служит появление любом из входов или у или ,3TO говорит о том, что в предыдущем разряде переходной процесс закончился и появляется информация ti переносе из предыдущего разряда О или 1. При появлении на входе у или у сигнала 1 сумматор начинает сложение и переходит из инертного состояния в действительное. Если при переходе из инертного состояния, в котором сигнал суммы , в действительное состояние, в котором , то сигнал завершения (Y l- или ) появляется только после.появления на выходе S сигнала . Если при переходе из инертного в действительное состояние выход суммы 5 остается в состоянии , то выход S не влияет на появление на выходе Y или Y,2 единицы. При такой, организации схемы сумматора логические элементы И 9 и 10 служат в качестве управляемых временных задержек, время появления сиг.нала которых от времени появления сигнала суммы (т.е. 5) является управляющим сигналом.. Если а и Ь устанавливаются одновременно,, то выгодно булевые функции X и X , записать в следующем виде X ciBz X atz-vatV,).z Это повысит быстродействие параллельного сумматора, так .как разрешение на суммирование одновременно распространяется и от младшего разряда и от разрядов, у которых -входы ав равны 00 и таким образом, поедложенная ооганизация комбинированного сумматора выгодно отличает его от известных сумматоров, так как позволяет производить индикацию момента окончания переходного процесса с повышенной надежностью. Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный сумматор | 1982 |

|

SU1078426A1 |

| Устройство для сложения и вычитания в избыточной двоичной системе счисления | 1984 |

|

SU1238061A1 |

| Устройство для умножения | 1980 |

|

SU894703A1 |

| Комбинационный сумматор | 1987 |

|

SU1411737A1 |

| Арифметическо-логическое устройство | 1979 |

|

SU822180A1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Комбинационный сумматор | 1983 |

|

SU1267405A1 |

| Комбинационный сумматор | 1988 |

|

SU1527630A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

Входы изобретения Формула Комбинационный сумматор, содержащий в каждом разряде элементы И и ИЛИ, причем входы первого элемента И соединены соответственно со входами инверсного значения первого, прямого значения второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы второго элемента И соединены соответственно со входами прямого значения первого, инверсного значени второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы третьего элемента И соединены соответственно

Таблица

Выходы со входами инверсных значений nepi, го и второго операндов и входом при мого значения переноса из предыдущего разряда сумматора, входы четвертого э; емента и соединены соответственно со входами -прямых значений -первого и второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы пятого элемента И соединены соответственно со входами инверсного значения первого, прямого значения втоу-ого операндов и входом прямого значения переноса из предыдущего разряда сумматора, входы шестого элемента И соединены соответственно со входами прямого значения первого инверсного

Авторы

Даты

1981-01-30—Публикация

1979-04-16—Подача