(St) УСТРОЙСТВО СТАБИЛИЗАЦИИ АЙАЛОГОЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Аналого-цифровое устройство | 1981 |

|

SU1018239A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1320901A1 |

| Устройство для автоматического контроля нагрева горных машин | 1991 |

|

SU1758242A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Способ аналого-цифрового преобразования с контролем выходного кода и аналого-цифровой преобразователь с контролем выходного кода | 1985 |

|

SU1292180A1 |

| Устройство для ввода изображений | 1986 |

|

SU1361593A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

1

Изобретение относится к области ядерной электроники и используется в спектрометрии ядерных излучений.

Известен аналого-цифровой преобразователь, содержащий источник опорных сигналов, детектор, усилитель, АЦП, измерительное устройство (включающее в себя цифровой блок сравнения и регистр эталонного кода) и регулятор. В этом устройстве реперные сигналы преобразуются в АЦП в цифровой код, который затем сравнивается в цифровом блоке сравнения с эталонным кодом. Сигнал ошибки, полученный в результате сравнения, поступает на регулятор, который корректирует коэффициент преобразования АЦП 1 3Недостаток данного устройства низкое качество стабилизации в результате искажения реперных сигналов за счет шумов и наложений сигналов на входе аналого-цифрового преобразователя.

Цель изобретения - улучшение качества стабилизации.

Поставленная цель достигается тем, что в устройство стабилизации аналого-цифрового преобразователя, содержащего аналого-цифровой преобразователь, первый вход которого соединен с входной шиной, второй вход - с выходом регулятора коэффициента преобразования , первый выход - с первым

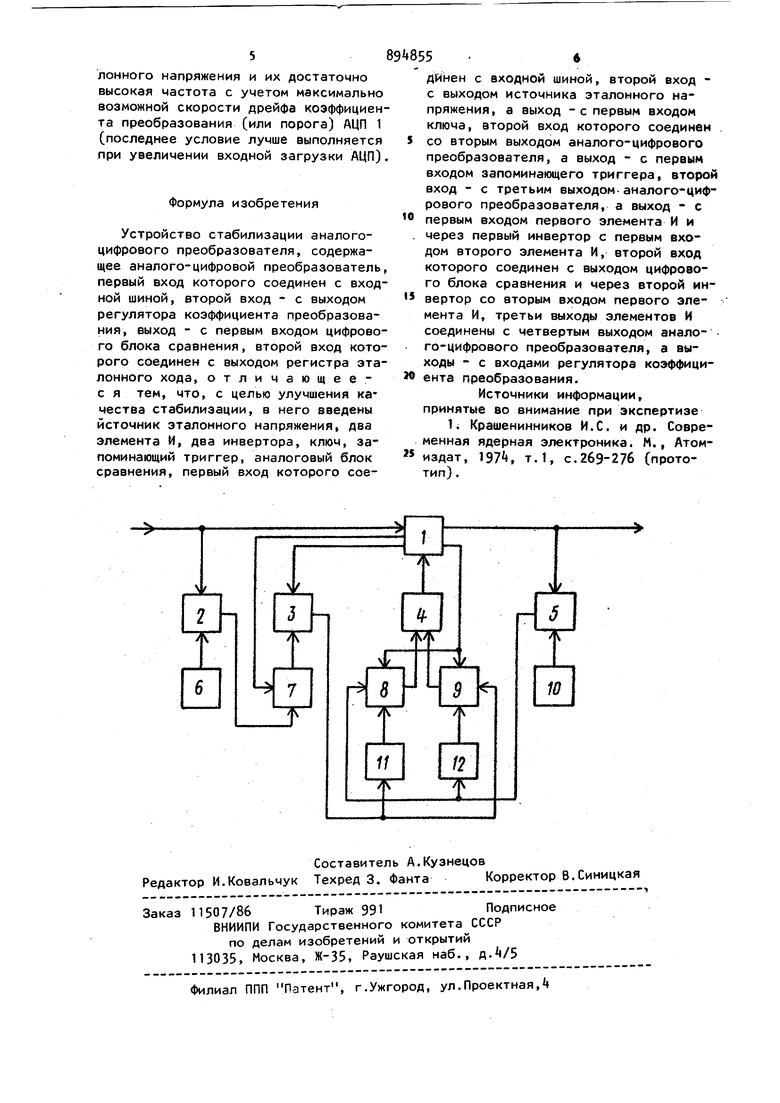

to входом цифрового блока сравнения, второй вход которого соединен с выходом регистра эталонного кода, дополнительно введены источник эталонного напряжения, два элемента И, два ин15вентора, ключ, запоминающий триггер,аналоговый блок сравнения, первый вход которого соединен с входной шиной, второй вход - с выходом источника эталонного напряжения, а выход 20с первым входом ключа, второй вход которого соединен со вторым выходом аналого-цифрового преобразователя, а выход - с первым входом запоминающего триггера, второй вход - с третьим выходом аналого-цифрового преобразователя, а выход - с первым входом первого элемента И и через первый инвертор с первым входом второго элемента И, второй вход которого соединен с выходом цифрового блока сравнения и через второй инвертор со вторым входом первого элемента И, третьи выходы элементов И соединены с четвертым выходом аналого-цифрового преобразователя, а выходы - с входами регулятора коэффициента преобразования, соединен со вторым входом второго элемента И. На чертеже представлена блоксхема устройства. Схема содержит АЦП 1., аналоговый блок 2 сравнения, запоминающий триггер 3, регулятор k, цифровой блок 5 сравнения, источник 6 эталонного напряжения, ключ 7, элементы И 8 и 9, регистр 10 эталонного кода, инверторы 11 и 12. Устройство работает следующим образом. Исследуемый сигнал поступает на вход АЦП и на аналоговый блок 2 срав нения, в котором он сравнивается с постоянным эталонным напряжением от источника 6. Цифровой код, соответст вующий этому сигналу, поступает с первого выхода АЦП на цифровой блок 5 сравнения, в котором он сравнивает ся с эталонным кодом от регистра 10. На выходе аналогового блока 2 сравнения сигнал появляется только в случае превышения исследуемым сигналом постоянного эталонного напряжения, а на выходе цифрового блока 5 сравнения сигнал появляется лишь в случае превышения соответствующим цифровым кодом эталонного кода. С выхода аналогового блока 2 сравнения сигнал подается через нормально открытый ключ 7 на вход установки в со стояние 1 запоминающего триггера 3 который предварительно устанавливает ся в состояние О логическим сигналом, соответствующим началу исследуе мого сигнала с третьего выхода АЦП. Сигнал с выхода запоминающего три1- гера 3 поступает на первый вход элемента И 9 и через инвертор 11 на пер вый вход элемента И 8. С выхода цифрового блока 5 сравнения сигнал пода ется на второй вход элемента И 8 и через инвертор 12 на второй вход эле мента И 9 На третьи входы элементов 54 И 8 и 9 подается логический сигнал с четвертого выхода, конец АЦП, Выходные сигналы элементов И 8 и 9 поступают на входы регулятора 4, коэффициента преобразования, выходной сигнал которого подается на второй вход АЦП. Если исследуемый сигнал на входе АЦП превышает эталонное напряжение от источника 6 и появляется сигнал на выходе аналогового блока 2 сравнения, который устанавливает запоминающий триггер 3 в состояние 1, а цифровой код этого сигнала на первом выходе АЦП оказывается меньше эталонного кода регистра 10, сигнала на выходе цифрового блока 5 сравнения нет, то появляется сигнал на выходе элемента И 9, и регулятор 4 коэффициента преобразования изменяет коэффициенты преобразования (или порог) АЦП в сторону увеличения. Если сигнал на входе АЦП 1 меньше эталонного напряжения, а цифровой код этого сигнала на первом выходе АЦП превышает эталонный код, то, появляется сигнал на выходе цифрового блока сравнения, и возникает сигнал на выходе элемента И 8, и регулятор k коэффициента преобразования изменяет коэффициенты преобразования (или порог) АЦП в сторону уменьшения. Если для одного и того же сигнала на входе АЦП 1 появляются сигналы на выходах обоих блоков 2 и 5 сравнения или же на выходах обоих блоков 2 сравнения и 5 сигналы не возникают, коррекция не происходит.Коррекции не происходит также и при отсутствии сигнала с четвертого выхода АЦП, благодаря чему исключаются ложные сигналы коррекции при отсутствии преобразования по условиям отбора сигналов дискриминаторами нижнего и верхнего уровней АЦП. Качество стабилизации определяется стабильностью источника 6 эталонного напряжения и порога аналогового блока 2 сравнения и не зависит от искажения исследуемых сигналов на входе АЦП. Коэффициенты преобразования (или порог) АЦП 1 определяется величинами эталонного напряжения и эталонного кода и может регулироваться изменением одной или обеих этих величин. .Условиями, необходимыми для работы устройства стабилизации, являются наличие непрерывного распределения исследуемых сигналов в области эталонного напряжения и их достаточно высокая частота с учетом максимально возможной скорости дрейфа коэффициента преобразования (или порога) АЦП 1 (последнее условие лучше выполняется при увеличении входной загрузки АЦП).

Формула изобретения

Устройство стабилизации аналогоцифрового преобразователя, содержащее аналого-цифровой преобразователь, первый вход которого соединен с входной шиной, второй вход - с выходом регулятора коэффициента преобразования, выход - с первым входом цифрового блока сравнения, второй вход которого соединен с выходом регистра эталонного хода, отличаю щеес я тем, что, с целью улучшения качества стабилизации, в него введены источник эталонного напряжения, два элемента И, два инвертора, ключ, запоминающий триггер, аналоговый блок сравнения, первый вход которого соедйнен с входной шиной, второй вход с выходом источника эталонного напряжения, а выход - с первым входом ключа, второй вход которого соединен со вторым выходом аналого-цифрового преобразователя, а выход - с первым входом запоминающего триггера, второй вход - с третьим выходом-аналого-цифрового преобразователя, а выход - с первым входом первого элемента И и через первый инвертор с первым входом второго элемента И, второй вход которого соединен с выходом цифрового блока сравнения и через второй инвертор со вторым входом первого элемента И, третьи выходы элементов М соединены с четвертым выходом аналого-цифрового преобразователя, а выходы - с входами регулятора коэффициента преобразования.

Источники информации, принятые во внимание при экспертизе

Ь Крашенинников И.С. и др. Современная ядерная электроника. М., Атомиздат, 197, Т.1, с.269-276 (прототип) .

Авторы

Даты

1981-12-30—Публикация

1979-07-10—Подача