1

Изобретение относится к вычислительной технике и предназначено для использования в высокопроизводительных цифровых системах обработки информации.

Известно устройство выборки инструкц й для блока обработки инструкций, обслуживающего две различные программы, которое содержит первый вентиль, информационный вход которого соединен с информационным выходом первого буфера команд, а управляющий вход вентиля, подсоединенный к первому входу триггера, соединен с первым, выходом логической схемы, информационный вход второго вентиля соединен с информационным выходом второго буфера команд, а управляющий вход этого вентиля, подсоединенный ко второму входу триггера, подключен ко второму выходу логической схемы,выходы обоих вентилей подсоединены ко входу регистра команд, выход которого связан со входом логической схе К недостаткам данного устройства следует отнести сложность логической схемы. Кроме того, возможен случай, когда не могут быть выполнены ни очередная команда из первой программы.

ни очередная команда из второй программы. При этом конвейерный блок обработки команд простаивает некоторое время, что снижает общую скорость выполнения команд.

Наиболее близким к предлагаемому по технической сущности является устройство поточной обработки информации, имеющее быстродействующую вспомогательную память. Данное устройство содержит программный счетчик, выход которого соединен с первьм входом блока выборки команд, второй вход которого связан с первой вспо15могательной памятью, а выход - со входом группы буферов и со входом блока управления стеком, выход последнего блока подключен к первому входу блока обращения к стеку, второй вход

20 которого подсоединен ко второй вспомогательной памяти, а выход соединен со входом блока индексации, выход блока индексации соединен с первым входсм блока обращения за операнда25ми, второй вход которого связан с третьей вспомогательной памятью, а выход блока обращения за операндами подключен к первому входу буферов,

30 второй вход группы буферов соединен

с ВЫХОДО1 группы буферов, а выход группы буферов соединен со входом арифметического блока, выход которого соединен со второй и третьей вспомогательной памятью и со входом буфера записи, выход буфера записи соединен со входом основной памяти j;2.

В известном устройстве возможны случаи, когда очередная считанная из памяти команда не может быть выполнена. Это происходит, когда для выполнения данной команды требуется операнд, являющийся результатом одной из предыдущих команд, выполнение которых еще не. завершено (например, команда условной передачи управления в зависимости от знака операнда не может быть выполнена, пока не будет вычислен сам операнд).Возникновение таких ситуаций приводит к тому, что устройство простаивает некоторое время, ожидая, пока не будет подготовлен операнд. В результате скорость выполнения команд, опрёделя пая частотой поступления потока команд на выполнение, снижается.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем что в устройство .управления конвейерным вычислительным устройством, содержащее память команд, сумматор, регистр адресов команд, регистр команд, первый второй регистры кода операции, регистр гщресов операндов, блок синхронизации, выход которого соединен со входами синхронизации регистра адресов команд, регистра команд, первого и второго регистров кода операции, регистра адресов операндов и памяти команд, выход которой соединен со входом регистра команд, выход регистра адресов команд соединен с информационным входом памяти команд и со входом сумматора, выход первого регистра кода операции соединен со входом второго регистра кода операции, выходы блока синхронизации, регистра адресов операндов , второго регистра кода операции являются соответственно выходом синхронизации, первым и вторым управляющими выходами устройства, дополнительно введены шесть блоков элементов И, два блока элементов ИЛИ два элемента НЕ, группа регистров задержки, два регистра задержки,дешифратор, вход, первая и вторая группы выходов которого соединены соот.ветственно с первым выходом регистра команд, группами входов первого регистра кода операции и первого регисра задержки, выход которого является третьим выходом устройства,первый выход дешифратора соединен с первьм входом первого .блока элементов И, второй выход дешифратора соединен с первыгли входами второго и третьего

блоков элементов И, третий выход дешифратора соединен с первым входом четвертого блока элементов И, выход сумматора соединен со входом второго регистра задержки, выход которого ,. соединен со вторыми входами первого и второго блоков элементов И, выходы первого, второго, третьего и четвертого блоков элементов И соединены с соответствуквдими входами первого блока элементов ИЛИ, выход которого соединен со входом первого регистра задержки группы, вход каждого последующего регистра задержки группы соединен с выходом предыдущего регистра задержки группы, выход последнего регистра задержки группы соединен со входом регистра адресов команд, второй выход регистра команд соединен с первым входом пятого блока элементов И и через первый элемент НЕ с первым входом шестого блока элементов И, третий выход регистра команд соединен со вторыми входами третьего, четвертого и пятого блоков элементов И, выходы пятого и шестого блоков элементов И соединены с соответствующими входами второго блока элементов ИЛИ, выход которого соединен со входом регистра адресов операндов, первый вход устройства соединен со вторым входом шестого блока элементов И, второй вход устройства соединен с третьим входом третьего блока элементов И и через второй элемент НЕ - с третьим входом второго блока элементов И, входы синхронизации регистров задержки группы первого и второго регистров зеццержки соединены с выходом блока синхронизации.

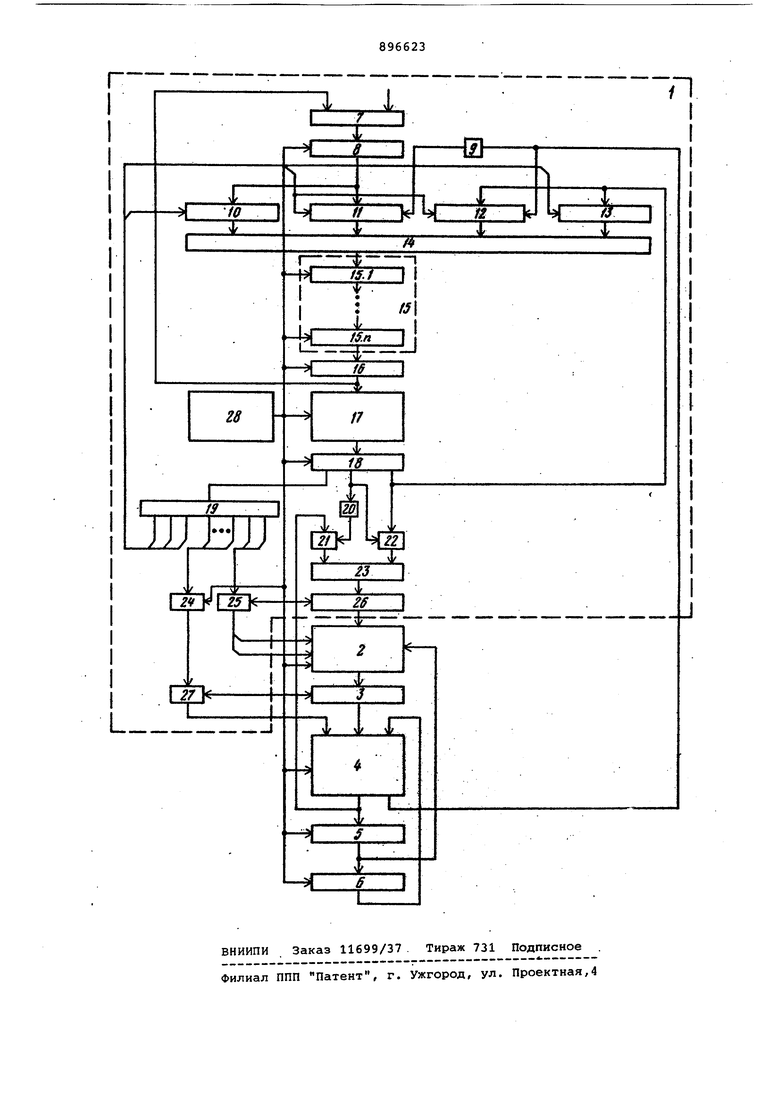

На чертеже представлена блок-схема устройства управления.

Конвейерное вычислительное устройство содержит устройство 1 управления, память 2 операндов, регистр 3 операндов, конвейерное арифметическологическое устройство (АЛУ) 4, первы 5 и второй 6 выходные регистры. Устройство 1 управления содержит сумматор 7, регистр 8 задержки, элемент НЕ 9, блоки 10-13 элементов И, блок 14элементов ИЛИ, группу 15 регистров задержки, регистр 16 адресов команд, память 17 команд, регистр 18 команд, дешифратор 19, элемент НЕ 20 блоки 21 к 22 элементов И, блок 23 элементов ИЛИ, регистр 24 кода операций, регистр 25 задержки, регистр 26 адресов операндов, регистр 27 код операции, блок 28 синхронизации.

Конвейерное АЛУ 4 обрабатывает полученную информацию в течении п тактов {такт - врегад, равное периоду генератора синхроимпульсов) и представляет собой п последовательно соединенных вычислительных звеньев. Каждое звено содержит логическую комбинационную схему и регистр (регистры). Логическая комбинационная схема данного вычислительного звена,прнимая информацию из регистров предыдущего вычислительного звена,выполняет определенную простую арифметическую или логическую функцию (на-, пример, операцию И, операцию сложения двух двоичных чисел и т.п.) и записывает результат (результаты) в регистр (регистры) данного вычислительного звена.-За время прохода информации через все п звеньев выполняются сложные операции. При этом простая операция в ЛЛУ вштолняется в первых звеньях этого АЛУ, и далее результат операции перемещается без преобразований. Конвейерное 7ШУ позволяет одновременно выполнять п арифметических и логических операций, причем в каждом также производится прием операндов и кода операции для выполнения в ЛЛУ, и,-соответственно, в каждом такте выдаются результаты выполненных операций. В частном случае конвейерное АЛУ может пропустить на выход без преобразования либо информацию со своего первого информационного входа, либо со своего второго информационного входа. Запись (прием) информации в регистры вычислительных звеньев конвейерного АЛУ, так же, как и запись информации во все остальные регистры конвейерного вычислительного устройства, производися по приходу синхроимпульса от блока синхронизации. Период синхроимпульсов выбирается так, чтобы за это время можно было или считать команду из памяти 17 команд, или считать либо записать информацию в память 2 операндов, или осуществить преобразование информации в любой комбинационной схеме, принимающей информацию из одного регистра и выдающей результат в другой регистр (например, в логической комбинационной схеме вычислительного звена конвейерного АЛУ). Величина п выбирается в зависимости от соотношения между быстродействием памяти (операндов или команд) и быстродействием логических схем, а также в зависимости от типа команд, выполнйералх в конвейерном АЛУ. В конвейерном вычислительном устройстве производится одновременное решение N задач, причем

N п-1-2.

Устройство работает следующим образом.

По адресу, записанному в регистр адресов 16 команд, производится считывание из памяти 17 команд очередной команды данной пррграмз дл. Это считывание производится в регистр 18 команд в момент прихода синхроимпульса от генератора синхроимпульсов . Одновременно увеличенное на единицу сумматором 7 значение адреса из регистра 16 записывается в регистр 8 задержки. Далее код операции команды, считанной в регистр 18 команд, расшифровывается дешифратором 19. При этом возбуждается одна из трех линий первой группы выходов дешифратора (в зависимости от того, является ли считанная команда коман0дной безусловной передачи управления, командой условной передачи управления или любой другой командой), один из выходов второй группы выходов дешифратора (в зависимости от

5 того, какая функция должна быть реализована конвейерным АЛУ 4 для выполнения считанной команды) и выход дешифратора (в зависимости от того, требует ли считанная команда

0 чтения из памяти 2 операндов, записи в память 2 операндов или не требует ни чтения, ни записи). Если в регистр 18 команд была считана команда безусловной передачи управления, то возбужденная кодом операции

5 этой команды соответствующая линия первой группы выходов дешифратора 19 открывает блок 13 элементов И, что позволяет по приходу синхроимпульса записать через блок 14 эле0ментов ИЛИ в первый регистр 15.1 группы регистров 15 задержки адрес Перехода из сщресного поля команды, находящейся в регистре 18 команд. Если в регистр 18 команд считана

5 команда условной передачи управления в зависимости от знака результата выполнения предыдущей команды этой же программы, то открыт или блок 11 элементов И или блок 12.

0 Если результат выполнения предыдущей команды данной программы отрицательный (в знаковом разряде этого результата единица), то .открыт блок 12 элементов И, что позволяет по приходу синхроимпульса записать

5 через блок 14 элементов ИЛИ в первый регистр 15.1 группы регистров задержки адрес перехода из адресного поля команды, находящейся в регистре 18 команд, т.ё, в данном слуQчае реализуется операция условного перехода по отрицательному значению результата выполнения предьщущей команды данной программы. Если же результат выполнения предыдущей ко5манды данной программы положительный (в знаковом разряде этого результата ноль), то открыт блок 11 элементов И, что позволяет по приходу синхроимпульса даписать через блок 14 элементов ИЛИ в первый ре0гистр 15.1 группы регистров задержки адрес из регистра 8 задержки, т.е. в данном случае не реализуется операция условного перехода,так как результат выполнения предыдущей

5

команды данной программы не является отрицательным. И, наконец, если в регистр 18 команд считана команда, не являющаяся командой передачи управления (условного или безусловного) , то открыт блок 10 элементов И, что позволяет по приходу синхроимпульса записать через блок 14 элементов ИЛИ в первый регистр 15.1 группы регистров задержки адрес из регистра 8 задержки.

Таким образом,осуществляется формирование адреса следующей команды данной програм вы.

Одновременно с записью адреса в регистр 15.1 производится запись информации со второй группы выходов дешифратора 19 в регистр 24 кода операции и информации с выхода дешифратора 19 в регистр 25 задержки. Регистры 24 и 25 предназначены для задержки информации на один такт.

Одновременно с записью адреса в регистр 15.1 производится формирование адреса операнда считанной в регистр 18 команд команды данной програмг и. В устройстве возможны два типа адресации памяти 2 операндов: прямая и косвенная. При прямой адресации в качестве адреса для обращения к памяти 2 операндов используется содержимое адресного поля текущей команды данной програмьФл, Причем по этому адресу можно или считывать информацию из памяти 2, или записывать информацию в эту память. При косвенной адресации в качестве адреса для обращения к памяти 2 операндов используется результат выполнения предыдущей команды данной программы (например, если предыдущая команда данной программы была командой считывания с прямой адресацией содержимого определенной ячейки памяти 2 операндов, то содержимое этой ячейки и будет являться адресом операнда текуще команды данной.программы, если эта текущая команда использует косвенную адресацию). При этом косвенная адресация используется только для считывания информации. Запись с косвенной адресацией производить нельзя. Таким образом, если в разряде признака адресации регистра 18 команд будет записана I (т.е. команда, находящаяся в этом регистре, использует прямую адресацию), то открывается блок 22 элементов И, что позволяет по приходу синхроимпульса записать через блок 23 элементов .ИЛИ в регистр 26 адресов операндов информацию из поля адреса регистра 18 команд (т.е. адрес операнда текущей команды данной программы).Если же в разряде признака адресации регистра 18 ксэманд записан О (т.е. команда, находящаяся в этом регистре использует косвенную адресацию), то открывается блок 21 элементов И,

что позволяет .по приходу синхроимпульса записать через блок 23 элементов ИЛИ в регистр 26 адресов операндов информацию с выхода конвейерного .АЛУ 4, являющуюся результатом выполнения предыдущей команды данной программы. Одновременно производится запись результата выполнения предаадущей команды данной программы с выхода конвейерного АЛУ 4 в выходной регистр 5.

Далее, по приходу следующего синхроимпульса производится либо считывание информации из памяти 2 операндов в регистр 3 операндов,либо запись информации с выхода выходного регистра 5 (результат выполнения предыдущей команды данной программы) в память 2 операндов, либо н производится ни считывания, ни записи. Обращение к памяти 2 производится по адресу из регистра 26 адресов операндов с использованием выходных сигналов регистра 25 задержки, управляющих режимом работы памяти 2 (чтение, запись или отсутствие и чтения и записи). Считывание из памяти 2 производится при выполнении команд чтения (с прямой или косвенной адресацией) и команд реализации двухместных арифметических и логических операций (команда умножения, команда ИЛИ и т.п.). Запись в память 2 производится при выполнении команды записи в память результата выполнения предыдущей команды данной программы. Ни запись, ни считывание не производятся при выполнении команд безусловной и условной передачи управления, а также команд реализации одноместных арифметических и логических операций , операнд которых уже находится в конвейерном АЛУ 4 (например, команда циклического сдвига вправо на один разряд результата выполнения предыдущей команды данной программы) .

Одновременно со считыванием информации из памяти 2 в регистр 3 операндов производится запись кода - операции этой команды из регистра 24 кода операции в регистр 27 кода операции и запись результата выполнения предыдущей команды данной программы из выходного регистра 5 в выходной регистр 6.

Далее, по приходу следукяцего синхроимпульса информация с выходов регистров 3,6 и 27 поступает в конвейерное АЛУ 4. АЛУ начинает выполнять функцию, определяемую кодом опрации текущей команды данной программы, причем сама функция задается значением выходных сигналов, поступающих из регистров 27 кода операции, а в качествеисходных данных для выполнения этой функции используется информация, полученная либо

с выхода регистра 3, либо с выхода регистра б, либо с выходов обоих этих регистров. Такими функциями могут быть двухместные арифметические и логические операции (здесь в качестве первого операнда используется информация, полученная с выхода регистра 3, а в качестве второго операнда - информация,полученная с выхода регистра 6),одноместные арифметические или логические операции над информацией, полученной с выхода регистра 6, отсутствие преобразования информации, полученной с выхода регистра 3 (т.е. передача этой информации через конвейерное АЛУ 4 без ее изменения),или отсутствие преобразования информации полученной с выхода регистра 6 (т.е. передача этой информации на выход конвейерного АЛУ 4 без изменения). Таким образом, конвейерное АЛУ4 позволяет выполнить двухместные арифметические и логические операции,причем первым операндом этих операций является операнд текущей команды данной программы, а вторым операндом результат выполнения предыдущей команды этой же программы, одноместные арифметические и логические операции над результатом выполнения предыдущей команды данной программы, передачу информации с выхода регистра 3 операндов и на вход АЛУ (при выполнении команд чтения из памяти с прямой или косвенной адресацией) с тем, чтобы последующая команда данной програг/1мы могла бы использовать эту информацию, а также передачу результата выполнения предыдущей команды данной програмглы на выход АЛУ (при выполнении команды записи результата предыдущей операции данной программы в память 2 операндов или команд безусловной либо условной передачи управления) с тем, чтобы последующая команда данной программы могла бы использовать эту информацию.

Через п тактов после подачи информации на вход конвейерного АЛУ 4 будет получен результат выполненной операции на выходе этого АЛУ. К этом же моменту времени в регистр 18 команд считана очередная команда данной программы, так как за время считывания текущей команды данной программы из памяти 17 в регистр 18,время формирования адреса операнда этой команды, время чтения этого операнда из памяти 2 в регистр 3 и время выполнения операции для данной команды в конвейерном АЛУ 4 вычислено приращение адреса текущей команды данной программы, сформирован адрес следующей команды этой же программы, задержан сформированный гщрес с помощь п регистров 15 задержки, записан данный адрес в регистр 16 и считана следующая команда из памяти 17 в регист

18 команд. Таким образом, результат выполнения текущей команды данной программы может быть использован следующей командой этой же программы для формирования адреса очередной команды данной программы и для формирования адреса операнда этой следующей команды. После задержки на один такт регистром 5 результата выполнения данной команды следукедая команда может записать этот результат в память

0 2, а после задержки результата еще на один такт (с помощью регистра 6) этот результат может использоваться для выполнения операции в конвейерном АЛУ 4.

5

Таким образом осуществляется выполнение команд данной программы, т.е. производится решение данной задачи .

При одновременном решении в кон0вейерном вычислительном устройстве N задач через каждые N тактов будет считываться из памяти 17 команда данной задачи на выполнение (также по истечении каждых N тактов будет выполняться одна команда данной

5 задачи), т.е. время выполнения любой команды данной задачи равно TN где Т - период синхроимпульсов, поступающих от генератора синхроимпульсов. Однако с учетом того, что ре0шаютсй одновременно N задач,получим, что результирующее время выполнения любой команды равно Т, т.е. из памяти 17 считывается суммарный поток команд (всех N решаемых задач) с

5 частотой, равной частоте работы генерат.ора синхроимпульсов. Эта частота и определяет результирующую скорость выполнения .команд всех задач. В обычных конвейерных вычислительных устройствах (выполняющих

0 решение одной задачи) такая же скорость выполнения команд может быть достигнута только в том случае, если каждая вновь считанная из памяти команда не использует результаты

5 предшествующих команд, выполнение которых еще не завершено в конвейерном вычислительном устройстве.

Формула изобретения

Устройство управления конвейерным вычислительным устройством,содержащее память команд, сумматор, регистр адресов команд, регистр команд, первый и второй регистры кода операции, регистр адресов операндов, блок синхронизации, выход которого соединен со .входами синхронизации регистра адресов команд, регистра команд, первого и второго регистров кода операции, регистра адресов операндов и памяти команд, выход которойсоединен со входом регистра команд, выход регистра адресов команд соединен с информационным входом памяти команд и со входом сумматора, выход первого регистра кода операции соединен со входом второго регистра кода операции, ВЫХОФ1 блока синхронизации, регистра адресов операндов, второго регистра кода операции являются соответственно выходом синхронизации, первым и вторым управляющими входами устройства, отличающееся тем, что, с целью повышения быстродействия, в него дополнительно введены шесть блоков элементов И два блока элементов ИЛИ, два элемента НЕ, группа регистров задержки два регистра задержки, дешифратор, вход, первая и вторая группы выходов которого соединены соответственно с первым выходом регистра команд, с группами входов первого регистра кода операции и первого регистра задержки, выход которого является третьим выходом устройства, первый выход дешифратора соединен с первым входом первого блока элементов И, второй выход дешифратора соединен с первыми входами второго и третьего блоков элементов И,третий выход дешифратора соединен с первым входом четвертого блока элементов И, выход сумматора соединен со входом второго регистра задержки , выход которого соединен со вторыми входами первого и второго блоков элементов И, выходы первого, второго, третьего и четвертого блоков элементов И соединены с соответствующими входами первого блока

элементов ИЛИ,, выход которого соединен со входом первого регистра задержки группы, вход каждого последующего регистра задержки группы соединен с. выходом предыдущего ре- гистра задержки группы, выход последнего регистра задержки группы соединен со входом регистра адреса команд, второй выход регистра команд соединен с первым входом пятого блока элементов И и через первый элемент НЕ с первым входом шестого блока элементов И, третий выход регистра команд соединен со вторыми входами третьего, четвертого и пятого блоков элементов И, выходы

пятого и шестого блоков элементов И соединены с .соответствующими входами второго блока элементов ИЛИ, выход которого соединен со входом регистра адресов операндов, первый вход устройства соединен со вторым входом шестого блока элементов И, второй вход устройства соединен с третьим входом третьего блока элементов И и через второй элемент НЕ - с третьим входом второго блока элементов И, входы синхронизации регистров задержки группы, первого и второго регистров задержки соединены с выходом блока синхронизации.

Источники информации,

принятые во внимание при экспертизе

1.Патент США № 3728692, кл, 235-153,- опублик. 1973.

2.Патент США 3949379.

кл. 235-153, опублик. 1976 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство обработки данных процессора | 1988 |

|

SU1647584A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

Авторы

Даты

1982-01-07—Публикация

1980-04-22—Подача