циненные входы которых являются управляющим входом блока управления, тактовый вход регистра памяти синхрокомбинации является тактовым входом блока управления, а выходы регистра памяти числа бит информации между соседними битами синхрокомбинации.

регистра памяти синхрокомбинации, регистра памяти числа бит в синхрокомбинации и регистра памяти числа бит в цикле являются соответственно первым, вторым, третьим и четвертым выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

| СПОСОБ ВЫДЕЛЕНИЯ ЦИКЛОВОГО СИНХРОНИЗИРУЮЩЕГО СИГНАЛА В СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010438C1 |

| Устройство для передачи ипРиЕМА диСКРЕТНОй иНфОРМАциипО пАРАллЕльНыМ КАНАлАМ СВязипЕРЕМЕННОй длиНы | 1978 |

|

SU794753A1 |

| СИСТЕМА СИНХРОННОГО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 1995 |

|

RU2096916C1 |

| Устройство цикловой синхронизации | 1985 |

|

SU1293849A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| Устройство циклового фазирования аппаратуры передачи двоичных сигналов | 1986 |

|

SU1415449A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ АППАРАТУРЫ ПЕРЕДАЧИ ДИСКРЕТ.НОЙ ИНФОРМАЦИИ, содержащее регистр блок сравнения и решающий блок, выход которого является выходом устройства циклового фазирования аппаратуры передачи дискретной информации, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения работы при различной структуре синхроцикла принимаемого сигнала, в него введены последовательно соединенные распределитель и коммутатор, последовательно соединенн 1е блок управления и сумматор, а также оперативньй запоминающий блок, выход которого подсоеди ней к первому входу блока сравнения, второй вход которого подключен к второму выходу блока управления, а выход блока сравнения подсоединен к информационному входу, решающего блока, установочньй вход которого подключен к третьему выходу блока управления, четвертый выход которого подсоединен к установочному входу распределителя, выход регистра подсоединен к адресному входу оперативного запоминающего блока и к второму входу сумматора, выход которого подсоеди-нен к второму входу коммутатора, выход которогоподсоединен к информационному входу регистра, второй вход распределителя объединен с входом сброса решающего блока и является первым тактовым входом устройства циклового фазирования аппаратуры передачи дискретной информации, вторым тактовым входом которого являются объединенные тактовые входы блока управления, регистра и оперативного запоминающего блока, а управляющий вход блока управления, информационный вход оперативнрго запоминающего . блока, а также объединенные входы записи/считывания коммутатора и оперативного запоминающего блока являют(Л ся соответственно управлякшщм входом, С информационным входом и входом записи/считывания устройства циклового фазирования аппаратуры передачи а с дискретной информации. 2.Устройство ПОП.1, отличающееся тем, что распределитель содержит последовательно соединенные делитель частоты и элемент сравнения, выход которого гюдсоеди4 нен к установочному входу делителя Од частоты, второй вход элемента сравне vl ния, счетный вход делителя частоты о и выход делителя частоты являются соответственно первым и вторым входами и выходом распределителя. 3.Устройство по п. 1, о т л и чающееся тем, что, блок управ дения содержит регистр памяти числа бит в цикле, регистр памяти синхроком бинации, регистр памяти числа бит информации между соседними битами синхрокомбинации и регистр памяти числа бит в синхрокомбинации, объе-

1

Изобретение относится к электросвязи и может использоваться для циклового фазирования систем передачи ди-кретной информации.

Известно устройство циклового фазирования, содержащее последовательно соединенные ключ, регистр сдвига, дешифратор, первьй и второй элементы И, последовательно соединенные блок сравнения, счетчик числа совпадений и триггер, последовательно соединенные декодер и блок памяти, выход которого подсоединен к второму входу второго злемента И, выход первого элемента- И подсоединен к входу ключа и второму установочному входу триггера, второй вход ключа подключен к выходу счетчика числа совпадений, второй выход регистра сдвига подсоединен к третьему входу ключа и входу блока сравнения, четвертьй вход ключ объединен с вторым входом блока сравнения и входом декодера, а выход триггера подсоединен к второму входу первого элемента И Л .

НедостаткЪм известного устройства циклового фазирования является отсутствие возможности циклового фазирования при различной структуре сигосроцикла принимаемого -сигнала.

Наиболее близким техническим решением к предпагаемому является устройство циклового фазирования аппаратуры передачи дискретной информации, содержащее регистр, блок сравнения И, решающий блок, выход кото рого является выходом устройства циклового фазирования аппаратуры передачи дискретной информации, последов тельно соединенные блок стробиоования и блок коррекции, а также счетчик вход и выход которого подключены соответственно к выходу блока сравнения и входу счетчика, выход которого подсоединен к входу решающего блока, первый, второй и третий выходы регистра подсоединены к соответствующим объединенным входам блока коррекции и блока сравнения, первый, второй и третий выходы которого подсоединены к соответствующим входам регистра, а вьсход блока коррекции подсоединен к входу блока сравнения 2.

Недостатком известного устройства циклового фазирования аппаратуры передачи дискретной информации является отсутствие возможности циклового фазирования при различной структуре синхроцикла принимаемого- сигнала.

Цель изобретения - расширение фунциональных возможностей путем обеспечения циклового фазирования при различной структуре синхроцикла принимаемого сигнала.

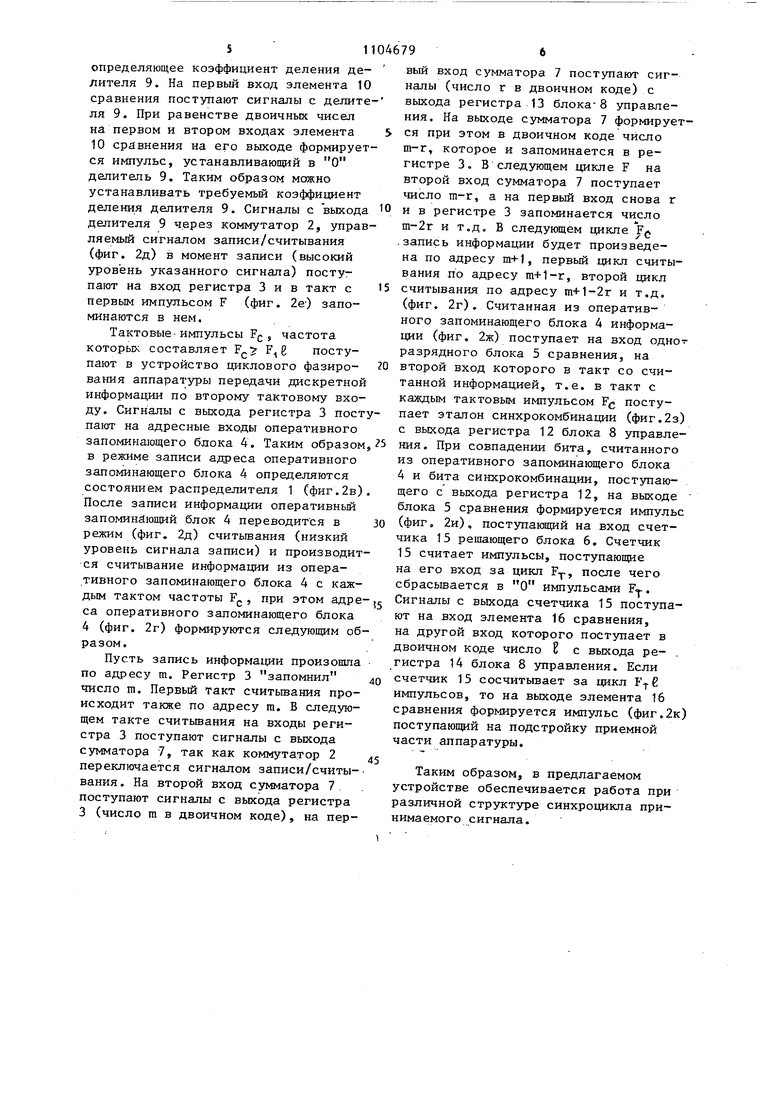

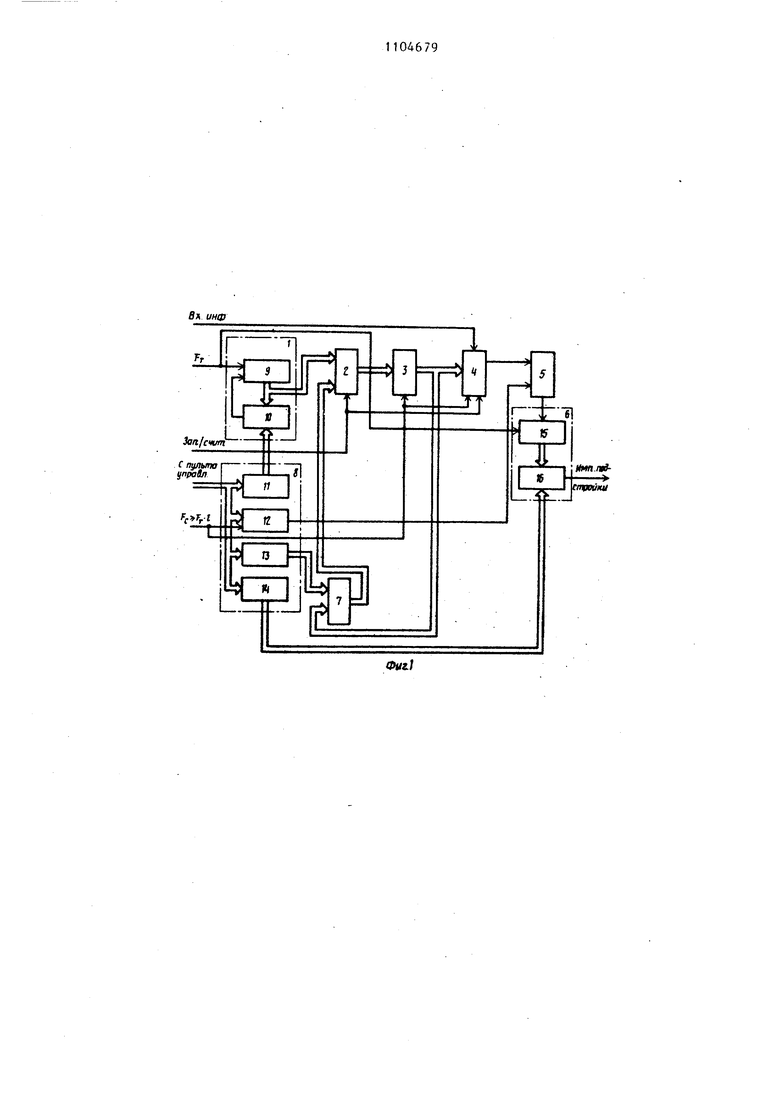

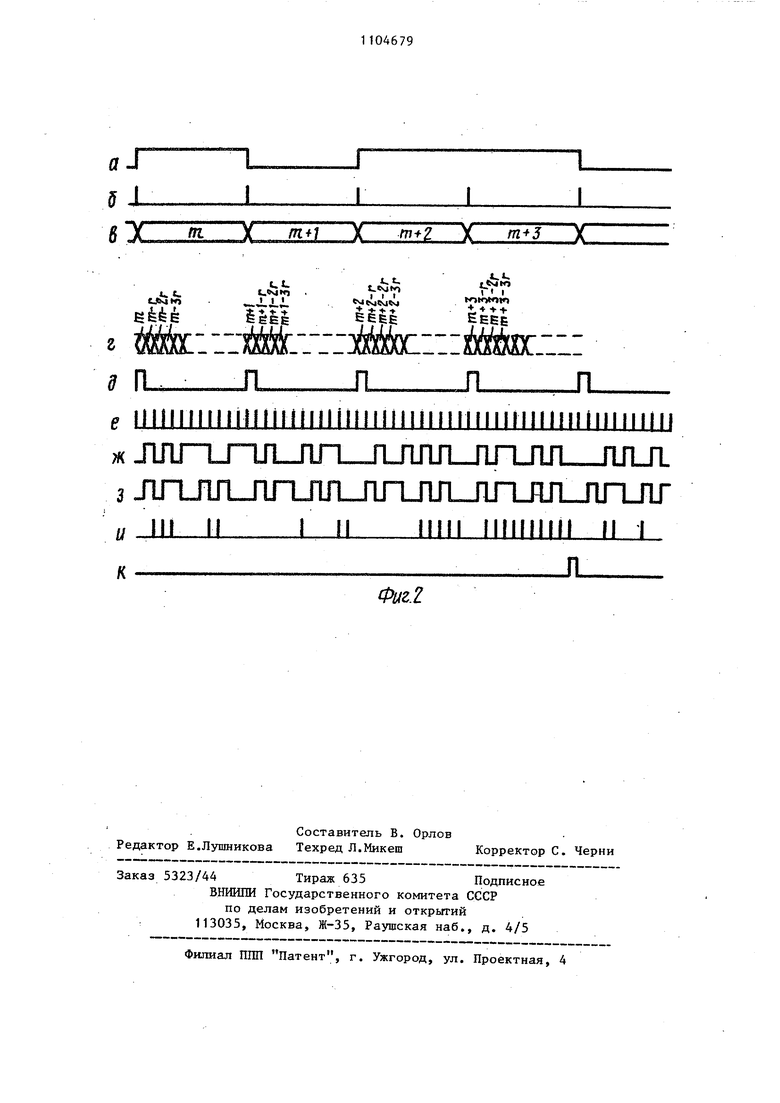

Дпя достижения поставленной цели в устройство циклового фазирования апаратуры передачи дискретной информации, содержащее регистр, блок сравнения и решающий блок, выход которог является выходом устройства циклового фазирования аппаратуры передачи дискретной информации, введены последовательно соединенные распределитель и коммутатор, последовательно соединенные блок управления и сумма. тор , а также оперативный запоминающий блок, выход которого подсоединен к первому входу блока сравнения, второй вход которого подключен к второму вьпоэду блока управления, а выход блока сравнения подсоединен к информационному входу решающего блока, установочный вход которого подключен к третьему входу блока управления. четвертый выход которого подсоединен к установочному входу распределителя выход регистра подсоединен к адресному входу оперативного запоминающего блока и к второму входу сумматора, выход которого подсоединен к второму входу коммутатора, выход ко- торого подсоединен к информационному входу регистра, второй вход распределителя объединен с входом сброса решающего блока и является первым тактовым входом устройства циклового фазирования аппаратуры передачи дискретной информации, вторым тактовым входом которого являются объединенн тактовые входы блока управления, ре гистра и оперативного запоминающего блока, а управляющий вход блока управления, информационный вход опе ративного запоминающего блока, а та же объединенные входы записи/считыв ния коммутатора и оперативного запоминающего блока являются соответственно управляющим входом, информационным входом и входом записи/СЧИ тьтания устройства циклового фазирования аппаратуры передачи дискретной информации. Распределитель содержит последовательно соединенные делитель частоты и элемент сравнения, выход кото рого подсоединен к установочному входу делителя частоты, второй вход элемента сравнения, счетный вход делителя частоты и выход делителя частоты являются соответственно первым и вторым входами и выходом распределителя. Блок управления содержит регистр памяти числа бит в цикле, регистр памяти синхрокомбинации, регистр памяти числа бит информации между соседними битами синхрокомбинации и регистр памяти числа бит в синхроком бинации, объединенные входы которых являются управляющим входом блока управления,тактовый вход регистра памяти синхрокомбинации является так товым входом блока управления, а выходы регистра памяти числа бит инфор мации между соседними битами синхрокомбинации, регистра памяти синхрокомбинации, регистра памяти числа бит в синхрокомбинации и регистра памяти числа бит в цикле являются соответственно перпым, вторым, треть им и четвертым выходами блока управления . На фиг. 1 приведена структурная электрическая схема устройства цикло- вого фазирования аппаратуры передачи дискретной информации; на фиг, 2 - диаграммы сигналов, поясняющие его работу. Устройство циклового фазирования аппаратуры передачи дискретной информации содержит распределитель 1, коммутатор 2, регистр 3, оперативный запоминающий блок 4, блок 5 сравнения решающий блок 6, сумматор 7 и блок 8 травления. Распределитель 1 содержит делитель 9 частоты и элемент 10 сравнения. Блок 8 управления содержит регистр 11 памяти числа бит в цикле, регистр 12 памяти синхро- комбинации, регистр 13 памяти числа бит информации между соседними битами синхрокомбинации, регистр 14 памяти числа бит в синхрокомбинации. Решающий блок 6 содержит счетчик 15 и.элемент 16 сравнения. Устройство циклового фазирования аппаратуры передачи дискретной ий- формации работает следующим образом. В каждом цикле принимаемого сигнала содержится N бит, из которых ь бит принадлежит равномерно расположенными в цикле битам синхрокомбинации. Количество бит информации между любыми соседними битами синхрокомбинации равно г бит. Эти данные, определяющие структуру синхроцикла принимаемого сигнала перед началом работы записываются через управляющий вход в блок 8 управления (фиг.1) В. регистр 11 записывается в двоичном коде число N. В регистр 12 записывается эталон синхрокомбинации для конкретного принимаемого сигнала. В регистре 13 записывается в дпоичном коде число г. В регистр 14 записывается в двоичном коде число В . Принимаемый сигнал (фиг. 2а) поступает на информационный вход оперативного запоминакнцего блока 4, который сигналом записи/считывания (фиг, 2д), поступающим по входу записи/считывания устройства циклового фазирования аппаратуры передачи дискретной информации, перевцдится в режим записи. Тактовые импульсы частотой F-j- (фиг,26) Поступают по второму входу распределителя 1 на счетньй вход делителя 9. На второй вход элемента 10 сравнения поступает с регистра 11 блока 8 управления в двоичном коде число N, 5 1 определяющее коэффициент деления делителя 9. На первый вход элемента 10 сравнения поступают сигналы с ля 9. При равенстве двоичных чисел на первом и втором входах элемента 10 сравнения на его выходе форьшрует ся импульс, устанавливающий в О делитель 9. Таким образом можно устанавливать требуемый коэффициент деления делителя 9. Сигналы с выхода делителя 9 через коммутатор 2, управ ляемый сигналом записи/считывания (фиг. 2д) в момент записи (высокий уровень указанного сигнала) поступают на вход регистра 3 и в такт с первьм импульсом F (фиг. 2е) запоминаются в нем. Тактовые-импульсы 7, частота которых составляет F поступают в устройство циклового фазироBaifflH аппаратзфы передачи дискретной информации по второму тактовому входу. Сигналы с выхода регистра 3 пост пают на адресные входы оперативного запоминающего блока 4. Таким образом в режиме записи адреса оперативного запоминающего блока 4 определяются состоянием распределителя 1 (фиг.2в) После записи информации оперативньй запоминающий блок 4 переводится в режим (фиг. 2д) считьгоания (низкий уровень сигнала записи) и производит ся считывание информации из оперативного запоминающего блока 4 с каждым тактом частоты F , при этом адре са оперативного запоминающего блока 4 (фиг. 2г) формируются следующим об разом. Пусть запись информации произошла по адресу т. Регистр 3 запомнил число т. Первый такт считывания происходит также по адресу га. В следующем такте считывания на входы регистра 3 поступают сигналы с выхода сумматора 7, так как коммутатор 2 переключается сигналом записи/считывания . На второй вход сумматора 7 поступают сигналы с выхода регистра 3 (число m в двоичном коде), на пер79вый вход сумматора 7 поступают сигналы (число г в двоичном коде) с выхода регистра 13 блока-8 управления. На выходе сумматора 7 формируется при этом в двоичном коде число m-r, которое и запоминается в регистре 3, В следующем цикле F на второй вход сумматора 7 поступает шcлo m-r, а на первый вход снова г и в регистре 3 запоминается число m-2r и т.д. В следующем цикле F запись информации будет произведена по адресу т+1, первый цикл считывания по адресу ra+1-r, второй цикл считывания по адресу m+1-2r и т.д. (фиг. 2г). Считанная из оперативного запоминающего блока 4 информации (фиг. 2ж) поступает на вход одноразрядного блока 5 сравнения, на второй вход которого в такт со считанной информацией, т.е. в такт с каждым тактовым импульсом F поступает эталон синхрокомбинадаи (фиг.2з) с выхода регистра 12 блока 8 управления. При совпадении бита, считанного из оперативного запоминающего блока 4 и бита синхрокомбинации, поступающего с выхода регистра 12, на выходе блока 5 сравнения формируется импульс (фиг, 2и), поступакяций на вход счетчика 15 решающего блока 6, Счетчик 15 считает импульсы, поступающие на его вход за цикл F, после чего сбрасьюается в О импульсами F. Сигналы с выхода счетчика 15 поступают на вход элемента 16 сравнения, на другой вход которого поступает в двоичном коде число Е с выхода ре- . гистра 14 блока 8 управления. Если счетчик 15 сосчитывает за хщкл F-j. 6 импульсов, то на выходе элемента 16 сравнения формируется импульс (фиг.2к) поступающий на подстройку приемной части аппаратуры. Таким образом, в предлагаемом устройстве обеспечивается работа при различной структуре синхроцикла принимаемого сигнала.

я

д а

е llllNMininiillinninillllllllllMlllllliniiHItlNll ж JinjnjnJLJir

3 J ЛJШJ JaJlЛJl

JJJ иI II11111 МИНИН II 1

к

п

п

л

Фиг

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство цикловой синхронизации | 1975 |

|

SU566379A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство циклового фазирования аппаратуры передачи двоичных сигналов | 1977 |

|

SU651494A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-07-23—Публикация

1983-02-09—Подача