(54) УМНОЖИТЕЛЬ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частотно-импульсных сигналов | 1981 |

|

SU968812A1 |

| Умножитель частоты | 1974 |

|

SU627554A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Умножитель частоты | 1980 |

|

SU868756A1 |

| Следящий умножитель частоты | 1979 |

|

SU832556A1 |

| Дискретный умножитель частоты повторения импульсов | 1977 |

|

SU692065A1 |

I

Изобретение относится к автомати-) ке и вычислительной технике и может быть использовано при умножении частотно-импульсных сигналов на коэффициент, больший единицы, с целью увеличения статической и динамической точности частотомеров.

Известен умножитель частотно-импульсных сигналов, содержащий управляемый генератор частоты, блок перераспределения, блок вьщеления разности периодов двух частот, элементы совпадения, счетчик импульсов, преобразователь код-напряжение, триггеры и делитель частоты LI .

Недостаток этого устройства - ограниченный диапазон умножаемых частот

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее делитель частоты, счетчик импульсов, соединенный через преобразователь код-напряжение с генератором частоть, блок

временной раздвижки импульсов, блок задержки, блок ньделения разности периодов, триггер и элементы совпадения, причем выход делителя частоты соединен со входами блока за- держки и одним входом триггера, второй вход которого подключен к выходу блока задержки, выход блока временной раздвижки соединен со входом блока задержки и одним входом блока выделения разности периодов, выход триггера подключен к первому входу одного элемента совпадения 2 .

Однако данное устройство характеризуется ограниченным диапазоном умножаемых частот.

Цель изобретения - расширение диапазона умножаемых частот при одновременном упрощении устройства.

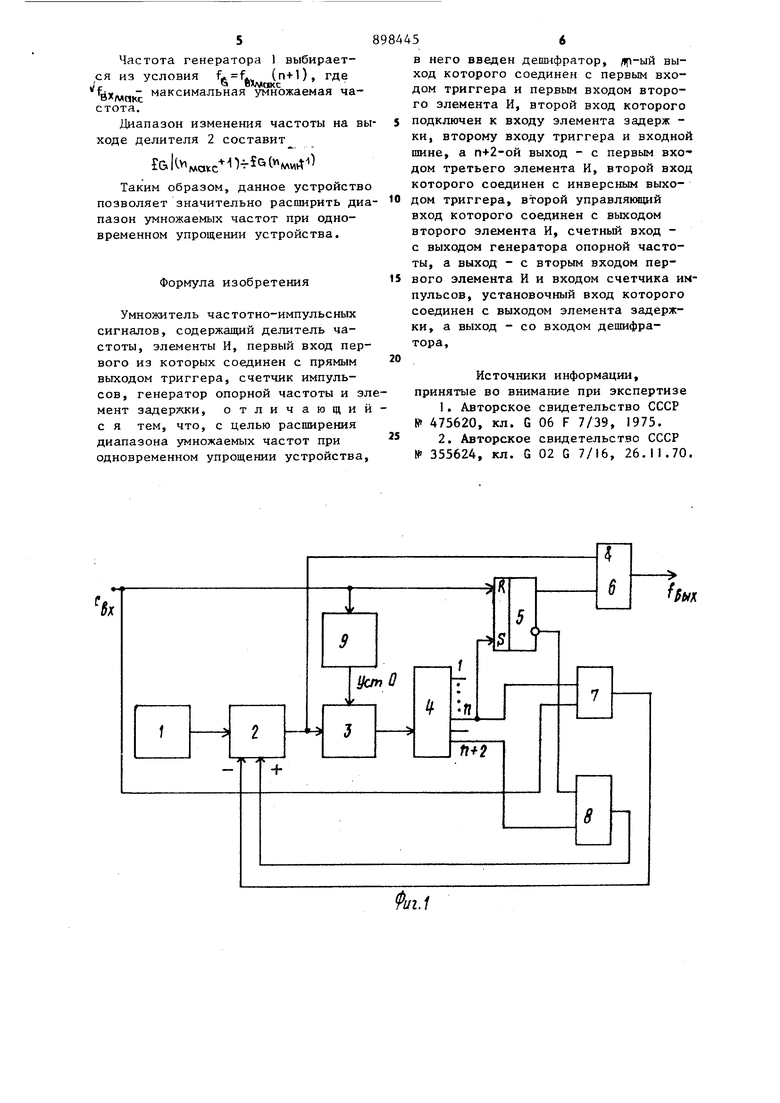

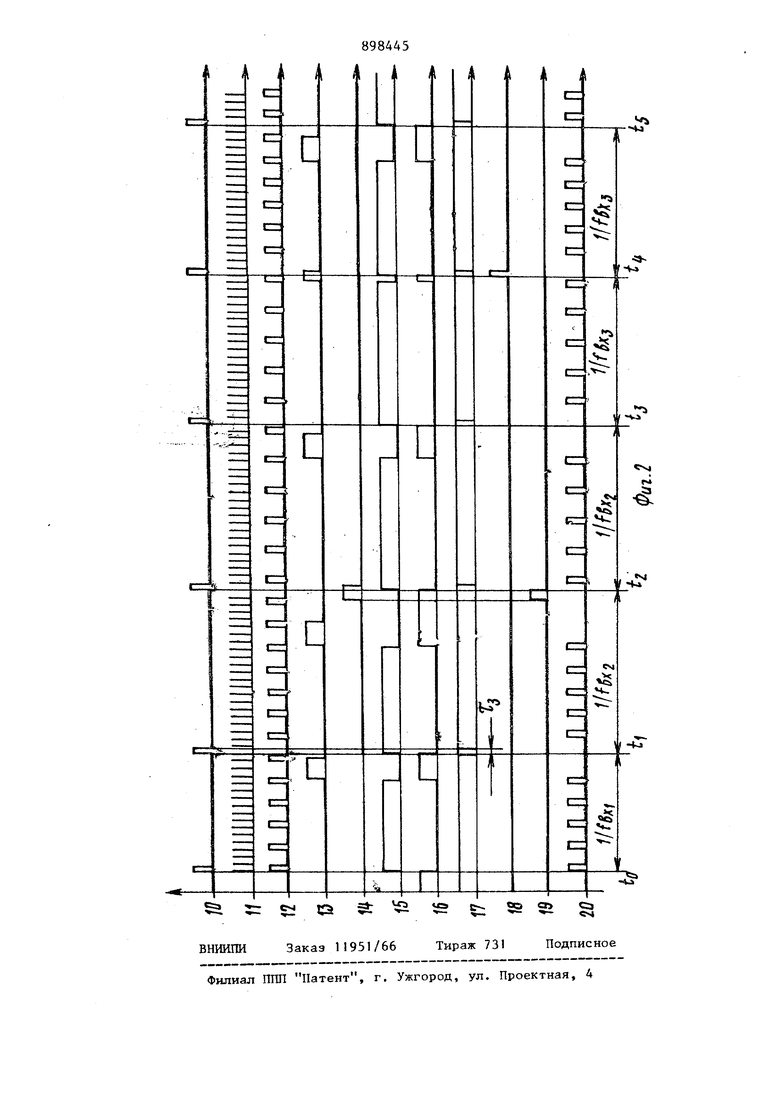

Поставленная цель достигается тем, что в умножитель частотно-импульсных сигналов, содержавши делитель частоты, элементы И, первый вход первого из которых соединен с прямым выходом триггера, счетчик импульсов, генератор опорной частот и элемент задержки, введен дешифратор, п-ый выход которого соединен с первым входом триггера и первьм входом второго элемента И, второй вход которого подключен к входу эле мента задержки, второму входу триггера и входной шине, а (п+2)-ой выход - с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом триггера, а выход - с первым управляющим входом делителя частоты, второй управляющий вход которого соединен с выходом второго элемента И, счетный вход - с выходом генератора опорной частоты, а выход - с вторым входом первого элемента И и входом счетчика импульсов, установочный вход которого соединен с выходом элемента задержки, а выход - со входом дешифратора. На фиг. 1 представлена структурная схема устройства на фиг. 2 временные диаграммы, поясняющие его работу. Устройство содержит генератор 1 опорной частоты, делитель 2 частоты с управляемым коэффициентом деле

НИН5 счетчик 3 импульсов, дешифратор 4, триггер 5, элементы 6-8 И, элемент 9 задержки.

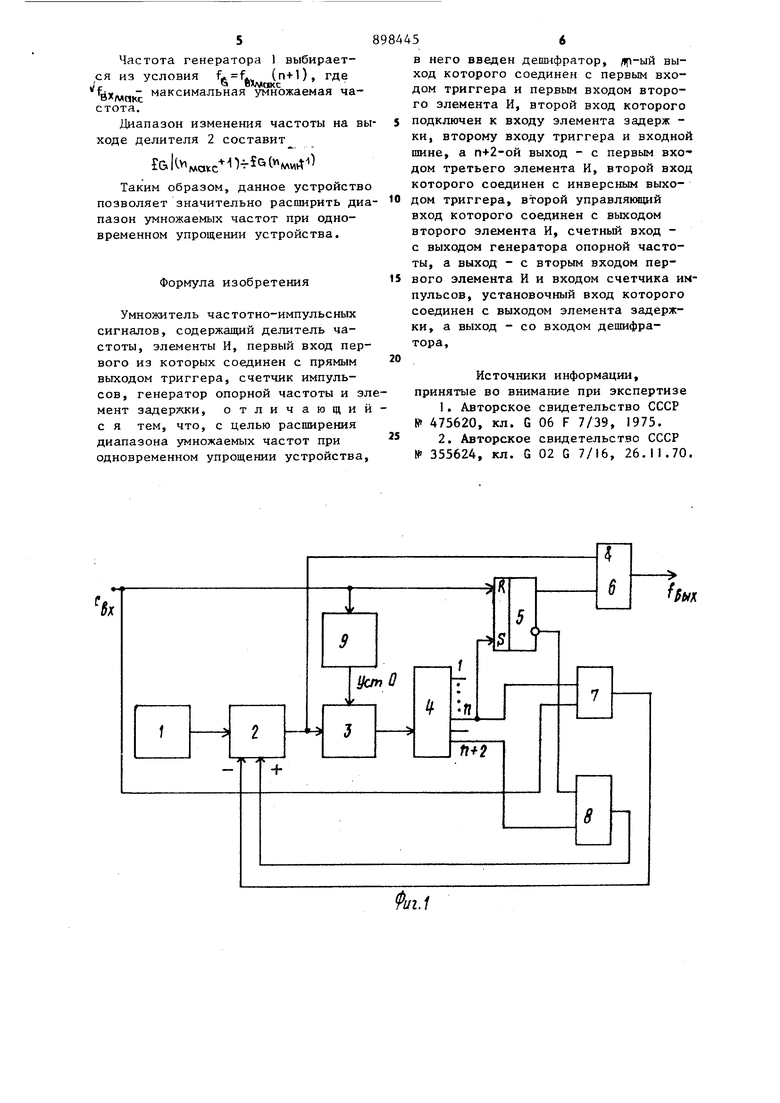

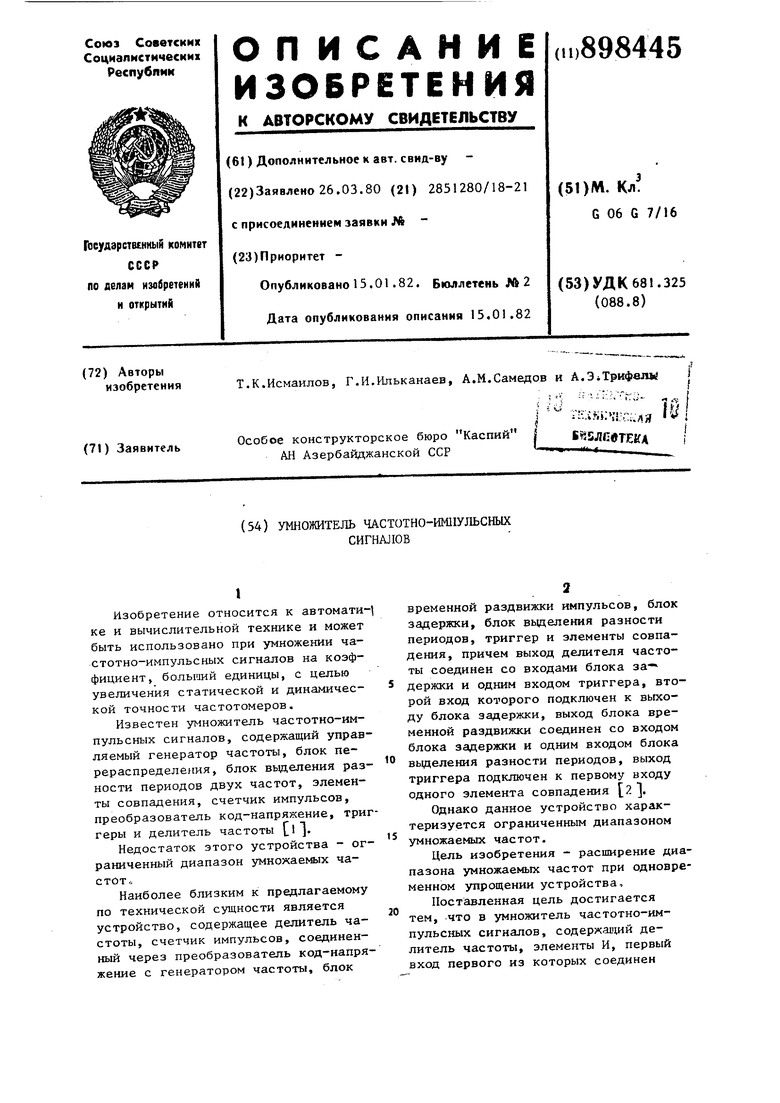

Умножитель частотно-импульсных сигналов работает следующим образом. В исходном состоянии коэффициент деления делителя 2 установлен что на его выход за один период вход ной частоты . фиг. 2 Ю) проходят (n+l) импульс генератора 1 (см. фиг. 2, 12), На выход умножителя за это же время пройдут П импульсов, так как на прямом выходе триггера 5 формируется импульс длительностью l/f-n, где f.,, - частота импуль: „„ ..„„„„„;:„„„ 9 ,„ i; / сов на выходе делителя 2. Триггер 5 устанавливается в состояние 1 с поступлением входного импульса и возвращается в исходное состояние с поступлением п-го импульса с выхода делителя 2, т.е. с п-го выхода дешифратора 4, управляемого счетчиком 3. Таким образом t, лП (см. фиг. 2.20, 2.15, 2.13, время ). На инверсном выходе триггера 5 формируётся импульс, длительность которого равна длительности между поступлением п-го импульса с выхода депоступающий на первый управляющий вход делителя 2 и изменяющий коэффициент деления его таким образом, что на выход делителя частоты 2 за шифратора 4 и ближайшим входным импульсом (см. фиг. 2.16). На выходах элементов 7 и 8 установлены уровни логической единицы. С поступлением каяодого входного импульса через время tr (см. фиг, 2.17), определяемым элементом задержки, счетчик 3 и дешифратор 4 возвращаются в исходное состояние. Частота на выходе делителя 2 частоты может принимать значения (1/К-К/К) fg, где fg - частота импульсов генератора 1, К - максимальный коэффициент деления частоты делителя 2. В исходном состоянии f 4--ft (n+1); L принимает значения от 1 до к. С уменьшением частоты входных импульсов до fgx , т.е. с увеличением их периода (см. фиг 2, время ), на выход делителя 2 при том же коэффициенте деления его L/K за один период входной частоты пройдут (п+2) и более импульсов (см. фиг. 2.12). С появлением импульса на (п+2)-ом выходе дешифратора 4 (см. фиг. 2.14) и совпадении его с импульсом на выходе триггера 5 HSI выходе элемента 8 появится импульс (см. фиг. 2.19), один период входной частоты вновь будет проходить (n+l) импульс, т.е. - -fj -Cn+l) fgj,, где Д дискрет ° изменения частоты на выходе делителя 2 (см. фиг. 2, время t,-t.,). С увеличением частоты входных импульсов до f. т.е. с уменьшением их периода, при совпадении импульса с п-го выхода дешифратора 4 и ближайшего входного импульса частоты на выходе элемента 7 (см. фиг. 2.18) появится импульс (см. фиг. 2, время ), изменяющий коэффициент деления делителя 2 частоты и устанавливаюищй его теперь уже равным Цр fQ ( у, (см. фиг. 2, время Очевидно, в статическом состоянии максимальный период между двумя ближайшими импульсами на выходе устройства может составить два периода текущей частоты на выходе деДИТР.ЛЯ 2 частоты. 1 выбираетЧастота генератора f-.f., (п+1), где ся из условия J,6 вХлдп максимальная умножаемая ча стота. Диапазон изменения частоты на ходе делителя 2 составит (w,,i) Таким образом, данное устройст позволяет значительно расширить д пазон умножаемых частот при одновременном упрощении устройства. Формула изобретения Умножитель частотно-импульсных сигналов, содержащий делитель частоты, элементы И, первый вход пе вого из которых соединен с прямым выходом триггера, счетчик импульсов, генератор опорной частоты и мент задержки, отличаювди с я тем, что, с целью расширения диапазона умножаемых частот при одновременном упрощении устройств в него введен дешифратор, flp-ый выход которого соединен с первым входом триггера и первым входом второго элемента И, второй вход которого подключен к входу элемента задерж ки, второму входу триггера и входной шине, а n+2-ой выход - с первым вхо дом третьего элемента И, второй вход которого соединен с инверсным выходом триггера, второй управляющий вход которого соединен с выходом второго элемента И, счетный вход с выходом генератора опорной частоты, а выход - с вторым входом первого элемента И и входом счетчика импульсов, установочный вход которого соединен с выходом элемента задержки, а выход - со входом дешифратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 475620, кл. G 06 F 7/39, 1975. 2. Авторское свидетельство СССР № 355624, кл. G 02 G 7/16, 26.11.70.

Авторы

Даты

1982-01-15—Публикация

1980-03-26—Подача