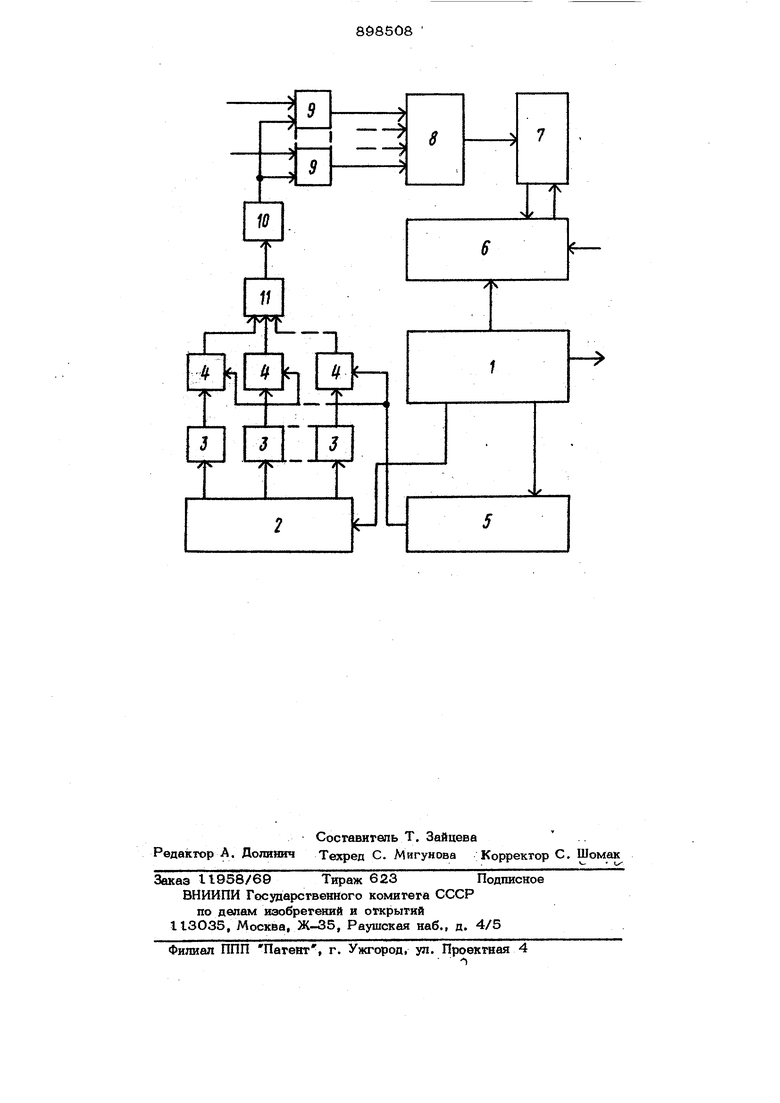

Изобретение относи1чзя к запоминающим устройствам. Известно устройство для контроля блоков памяти, содержащее схемы сравнения числовой регистр, усилители чтения, вспомогательное запоминающее устройство и блок управления. В этом устройств© пре дусмотрена подача импульсов стробхфования в разное время относительно начала сигнала чтения Cl3. Недостатком этого устройства являет ся невысокая точность контроля. Наиболее близким техническимрешением к изобретению является устройство для контроля блоков памяти, содержащее блок управления, вспомогательное запоминающее устройство, схемы сравнения, числовой регистр, усилители чтения, соединенные с формирователями строба С 2. Недостатком этого устройства является невысокая точность контроля, так как в нем не предусматривается определение оптимального времени подачи импульсов стробирования на усилители чтения. Цепь изобретения - повьпиеняе точности контроля блоков памяти. Птютавленная цель достигается тем, что в устройство для контроля блоков памяти, содержащее числа, уснлй- тепи чтения, формирователь стробирук ших сигналов, схему сравнения, блок управления в накопитель, причем выход формирователя стробируюших сигналов подключен к одним вз входов усилителей чтенш, другие входы которых являются инфорлашюнными входами устройства, а выходы соединены со входами регистра числа, выход которого подключея к первому входу схемы сравнения, второй вход к выход которой соединены соответхзтвёкно с выходом и с первым входсял накопи- теля, второй вход которого подключен к первому выходу блока управления, третий вход накопителя и второй выход блока управления являются соответственно управляющими входом и выходом устройства, введены счетчик формирователи управляющих сигналов, элемент задержки, элеменг ИЛИ и элемент И, причем входы и элемента задержки подключен соответственно к третьему и четвертому выходам блока управления, выходы элемента задержки соединены соответствен- Но со входами формирователей управляющих сигналов, выходы которых подключены к первым входам соответствующих элеменгов И, вторые входы которых соединены с выходом счетчика, входы элемента ИЛИ подключены к выходам элементов И, а выход соединен со входом формирователя стробирующих сигналов. На чертеже изображена функциональная схема предложенного устройства, Устройство содержит блок управления t, элемент задержки 2, формирователи управляющих сигналов 3, элементы РГ 4, счетчик 5, накопитель 6, схему сравнения 7, регистр числа 8, усилители чтеНИН 9, формирователь сгробируюших сигналов Ю и элемент ИЛИ II. Выход формирователя Ю подключен к одним из входов усилителей 9, другие входы которых являются информационными входами устройства, а выходы соединены со входами регистра 8. Выход регистра 8 подключен к первому входу схемы сравнения 7, второй вход и выход которой соединены соответственно с выходом и с первым входом накопителя 6, второй вхо которого подключен к первому выходу блока управления I. Третий вход накопителя 6 и второй выход блока управления I являются соответственно управляющим входом и выходом устройства. Входы счетчика 5 и элемента задержки 2 подключены соответственно к третьему и к четвертому выходам блока управления I Выходы элемента задержки 2 соединены соответственнб со входами формиро |вателей 3, выходы которых подключены к первым входам соответствующих элементов И 4, вторые входы которых соединены с выходом счетчика 5, Входы элемента ИЛИ 11 подключены к выходам элементов И 4, а выход соединен со входом формирователя Ю, Информационные входы и управляющие вход и выход устройства подключаются к соответствующим выходам и входу контролируемого блока памяти (на чертеже не показан). Накопитель 6 является накопителем полупостоянного типа. Устройство работает следукдцим образом. Предварительно в накопитель 6 записываются те же коды чисел и по тем же адресам, что и в контролируемый блок памяти. По си1Ч1алу из блока управления I происходит считыгзание информации по очередному адресу из проверяемого блока памяти. В это же время из блока управления I поступает импульс тока на вход элемента задержки 2 и на запуск счетчика 5, В соответствии с кодом числа, хранящегося в данный момент в счетчике 5, открывается один кз элементов И 4, например первый справа элемант И 4, При этом с соответствующего выхода элемента задержки 2 сигнал, сформированный соответствующим формирователем 3, проходит через элемент И 4 и элемент ИЛИ 11 на вход формирователя 10, который вырабатывает импульс стробиро- вания, поступающий на первые входы усилителей 9 в момент времени, определяемый задержкой прохомсдения сигнала на элементе задержки 2, Считанное число из проверяемого блока памяти после усиления и стробирования поступает на регистр 8, а затем на первый вход, схемы сравнения 7, на второй вход которой приходит код того же числа из накопителя 6. При совпадении или несовпадении кодов чисел в накопитель 6 записывается соответствующий сигнал. Затем из блока управления 1 подаются очередные сигналы опроса проверяемого блока памяти запуска счетчика 5 и сигнал на вход элемента задержки 2, В соответствии с кодом числа, хранящегося в данный момент в счетчике 5, открываетсядругой элемент И 4 для прохождения сигнала на запуск формирователя 10, в результате чего стробирующий сигнал смещается по времени относительно предыдущего стробирующего сигнала. Этот процесс опроса проверяемого блока памяти по одному и тому же адресу, но с воспроизведением сигналов чтения по смещенному стробирующему сигналу может проводиться несколько раз, что определяется техническими требованиями к информационной надежности проверяемого блока памяти и количеством выходов элемента задержки 2, количеством формирователей управляющих сигналов 3 и элементов И 4, Режимы проверки могут быть установлены с помощью блока управления I. Такими режимами могут быть, во-первых, режимы последовательной проверки безошибочного считывания всех чисел из проверяемого блока памяти при подаче сигнала стробирования в одно и то же время, а затем введение аналогичной проверки при последователь-ном смещении по времени стробирующего сигнала, а, во-вторых, смещение по вралени сгробирующего сигнала при мно- гокрагном чтении числа по одному и тому же адресу, что позволяет в обоих слу чаях выбрать оптимальное время строби- ровання и в результате повысить точност контроля блока памяти. Технико-экономическое преимущество предложенного устройства заключается в обеспечении более высокой, по сравнению с известным точности контроля, достигаемой за счет выбора оптимального ни стробирования сигнала чтения. Формула изобретения Устройство для контроля блоков памяти, содержшцее регистр числа, усилители чтения, формирователь стробирующих сигналов, схему сравнения, блок управления и накопитель, причем выход фор мирователя стробирующих сигналов подключен к одним из входов усилителей чтения, другие входы которых являются информапиот1ыми входами устройства, а выходы соединены со входами регистра числа, выход которого подключен к первому входу схемы сравнения, второй вход и выход которой соединены соответственно с выходом и с первым входом на- копителя, второй вход которого подключен к первому выходу блока управления, третий вход накопителя и второй выход блока управления являются соответчзгвенно управляющими входом и выходом устройства, отличающееся гем, что, с целью повыщения точности контроля, оно содержит счетчик, формировате-. ли управляющих сигналов, элемент за- держки, элемент ИЛИ и элементы И, причем входы счетчика и элемента задержки подключены соответственно к третьему и к четвертому выходам блока управления, выходы элемента задержки соединены соответственно со входами формирователей управляющих сигналом, выходы которых подключены к первым вхо.. дам соответствующих элементов И, вторые входы которых соединены с выходом счетчика, входы элемента ИЛИ подключены к выходам элементов И, а выход соединен со входом формирователя сгро- бируюших сигналов. Источники янформашш, хфннятые во внимание при экспертизе 1.Авторское свидетельство СССР № 706882, кл. G II С 29/ОО, 1978. 2.Авторское свидетельство СССР NJ 702412, кл. G, 11 С 29/ОО, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1982 |

|

SU1049980A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Запоминающее устройство | 1986 |

|

SU1361636A1 |

| Запоминающее устройство | 1982 |

|

SU1062787A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство микропрограммного управления с контролем | 1990 |

|

SU1805466A1 |

| Устройство для приоритетного распределения заданий | 1987 |

|

SU1509888A1 |

| Устройство для ввода информации | 1985 |

|

SU1251091A1 |

Авторы

Даты

1982-01-15—Публикация

1980-05-23—Подача