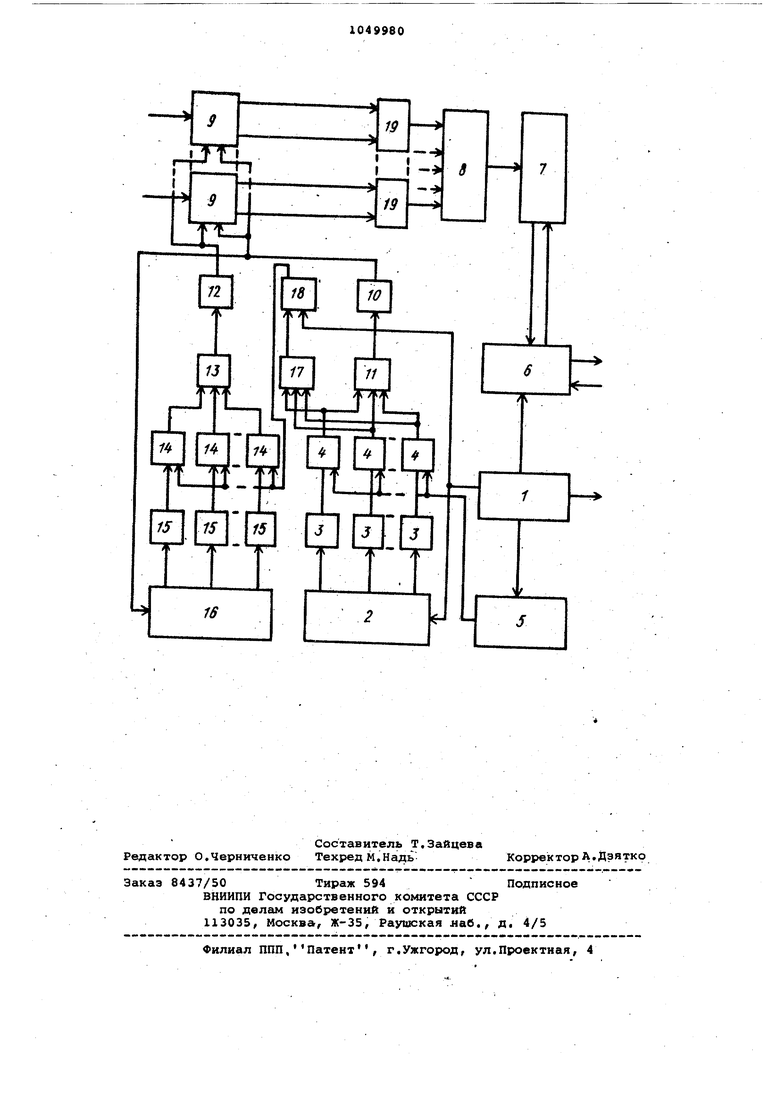

Изобретение относится к вычислительной технике. Известно устройство для контроля блоков памяти, содержащее блок управ ления, счетчик, триггер, регистр сдэига, блок сравнения, регистр, эле мент И, блок индикации, элемент задержки и две группы, элементов И 1 , Недостатком этого устройства явля ется невысокая точность контроля. Наиболее близким к, изобретению по технической сущности является устройство для контроля блоков памяти, содержащее регистр числа, усилители чтения, формирователь стробирующих сигналов, блок сравнения, блок управления, счетчик, формирователи управляющих сигналов, элемент задерж ки, элемент ИЛИ, группу элементов И и накопитель, причем выход формирователя стробирукхчих сигналов подключен; к одним из входов усилителей чтения, другие входы которых являются информационными входами устройства, а выходы соединены с входами регистра числа, выход которого подключен к первому входу блока сравнения второй вход которого и выход соединены соответственно с выходами и с первым входом накопителя, второй вхо которого подключен к первому выходу блока управления, третий вход накопителя и второй выход блока управле ния являются соответственно управля ющими входами и выходом устройства, входы счетчика и элемента задержки подключены соответственно к .третье,му и четвертому выходам блока управ ления, выходы элемента задержки сое неаы соответственно с входами фор мирователей управляющих сигналов, выходы которых подключены к первым входам группы элементов И, вторые входы которых соединены с входом счетчика, выходы элемента ИЛИ подкл чены к выходам группы элементов И, а выход соединен со входом-формиров теля стробирующих сигналов 2. Недостатком известного устройства является отсутствие возможности автоматического определения оптималь ного времени следования второго сигнала с-тробирования относительно первого при двухкратном стробировании, что снижает точность контроля. Цель изобретения - повышение точности контроля, Поставленная цель достигается тем что в устройство для контроля блоков памяти, содержащее регистр числа, усилители считывания, блок сравнения .первый формирователь стробирующих сигналов, блок управления, счетчикимпульсов, первую группу формирователей управляющих сигналов, первую группу элементов задержки, первый элемент ИЛИ, .первую гру;ппу элементов И и накопитель, один из входов которого подключены соответственно к выходам блока сравнения и к первому выходу блока управления, второй и третий выход которого соединены соответственно с входом счетчика импульоов и с входами элементов задержки первой группы, выходы которых подключены к входам формирователей управляющих сигналов первой группы, выходы которых соединены с первыми входами элементов И первой группы, вторые входы которых подключены к выходам сч1втчика импульсов, а выходы. к входам первого элемента ИЛИ, выход которого соединен с входом первого формирователя стробирующих сигналов, выход которого подключен к первым входам усилителей считывания, причем выходы регистра числа соединены с одними из входов блока сравнения, другие входы которого подключен к одним из выходов накопителя, другие входы и выходы которого являются контрольными входами и выходами устройства, управляющим выходом и инфор-. мационными входами устройства являются четвертый выход блока управления .и вторые входы усилителей считывания, введены второй формирователь стробирующих сигналов, вторая группа формирователей управляющих сигналов,, триггер, вторая и третья группы .эле-, ментов И, второй и третий элементы ИЛИ и вторая группа элементов задержки, входы каторых подключены к выходу первого формирователя стробирующих сигналов, а выходы - к входам формирователей управлякицих сигналов второй группы, выходы которых соединены с первыми входами элементов И второй группы, .выходы которых подключены к входам второго элемента ИЛИ, выход которого соединен с входом второго формиррвателя стробирующих сигналов, выход которого подключен к третьим входам усилителей считывания, выходы которых соединены со входами элементов И третьей группы, выходы которых подключены i входам регистра числа, причем вторые входы элементов И второй группы соединены . |С выходом триггера, входы которого подключены соответственно к входам элементов задержки первой группы и к выходу третьего элемента ИЛИ,, входы которого соединены с выходами элементов И первой группы, На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит блок 1 управления, первую группу элементов 2 задержки первую группу формирователей 3 управляющих сигналов, первую группу элементов И 4, счетчик 5 импульсрв, накопитель 6, блок 7 сравнения, регистр 8 числа, усилители

9считьтания, первый формирователь

10стробирующих сигналов, первый элемент ИЛИ 11, второй формирователь

12 стробируюиих сигналов, второй элемент ИЛИ 13, вторую группу элемен- ,

тов И 14, вторую группу формироватёлей 15 управляющих сигналов, вторую

группу элементов 16 задержки, третий

элемент ИЛИ 17, триггер 18 и третью группу элементов И 19.

Накопитель б является накопителем 10

полупостояннаго типа, -

Устройство работает следующим об разом.

Предварительно в накопитель 6 заг писыва:отся те же коды чисел и по тем 15 же адресам, что и в контролируемый блок памяти.

По сигналу Tf3 блока 1 происходит считывание информации по очередному адресу из контролируемого блока памя20 ти. В это же время из блока 1 поСту- пает импульс тока на вход элементов 2 задержки и на запуск счетчика 5, В соответствии с кодом числа, храняадегося в данный момент в счётчике 5/ 25 открывается один, из элементов И 4 и через элемент ИЛИ 11 поступает управляющий сигнал на вход формирователя 10, который вырабатывает сигнал стробирования, поступающий на входы л усилителей 9 (в момент времени, определяемый задержкой прохождения сигнала на элементе задержки 2) и на вход, .элементов задержки 16. Выходные сигналы с элементов задержки 16 пооче- .. редно подаются навходы формироватё- лей 15, с выходов которых они поступают на первые входы элементов И 14, на вторые входы которых подается разрешающий сигнал с выхода триггера 18, так как триггер 18 к этому времени 40 находится в состоянии «i« за счет подачина один из его входов импульса с выхода элемента ИЛИ 17, на вход , которого поступают сигналы с элемен,тов И 4 (предварительно триггер 18 j по сигналу из блока 1 находится в исходном нулевом состоянии). С выходов элементов И 14 управляющие сигналы поступают на входы элемента ИЛИ 13, выходной сигнал, с которого

подается на ,вход формирователя 12, .с выхода которого подается сигнал на третьи входы усилителей 9 для стробирования сигналов считывания по второму каналу. Число сформированных сигналов считывания по второму каналу равно числу выходов элемента задержки 16,в то время как по первому каналу формируется только один сигна считывания, который, как и сигналы считьтания второго канала, подается на входы элементов И 19. При совпадении указанных сигналов с выходов элементов И 19 информационные сигналы поступают на входы регистра 8, а ,затем на одни из входов блока 7, на другие входы которого подается код числа из накопителя 6. Этот код оди,наков с ожидаемым кодом числа, считываемого из контролируемого блока памяти. Результаты сравнения сигналов, т.е. результаты совпадения сигналов по обоим каналам поступают в |наколитель 6. Затем по этому же адресу в контролируемый блок памяти подается новый сигнал на считывание. При этом стробирование сигнала считы вания по первому каналу производится по сигналу, поступившему с одного иэ выходов элементов задержки 2, а по второму каналу снова производится многократное стробированиб, т.е. по сигналам с выходов всех элементов задержки 16 (как это описано ранее). Таким образом, общее число сформированных сигналов с;«итывания, подаваемых на блок 7, равно п-п п, где п - соответственно число выходов элементов задержки 2 м элементов 16 задержки. .

-Таким образом, предлагаемое устройство позволяет определить оптимальные времена стр&бирования сигнала считывания при двухкратном стробировании, вследствие чего повышается . точность контроля блоков памяти I

Технико-экономическое преимущество предлагаемого устройства по срав|нению с известным заключается в боле 1ВЫСОКОЙ точности контроля блоков па1МЯТИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU898508A1 |

| Устройство для ввода информации | 1987 |

|

SU1509914A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Оперативное запоминающее устройство типа @ с обнаружением и исправлением ошибок | 1981 |

|

SU999114A1 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Запоминающее устройство | 1982 |

|

SU1062787A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ, содержащее регистр числа/ усилители считывания, блок сравнения, первый формирователь стробирующих сигналов, блок управления, счетчик импульсов, первую группу формировате лей управляющих сигналов, первую группу элементов задержки, первый элемент ИЛИ, первую группу элементов И и накопитель, одни из входов которого подключены соответственно к выходам блока сравнения и к первому выходу блока управления, второй и третий выходы которого соединены соответственно с входом счетчика импульсов и с входами элементов эадержк -и первой группы, выходы которых подключены к входам формирователей управляющих сигналов первой группы, выходы которых соединены с первыми входами элементов И первой грушш, вторые входы которых подключены к выходам счетчика импульсов, а выходы - к входам первого элемента ИЛИ, выход которого соединен с входой первого формирователя стробир оцйх сигналов, выход. которого подключен к первым входам усилителей считывания, причем выходы регистра числа соединены с одними иэ входов блока сравнения, другие входы которого подключены к одним иэ выходов накопителя, другие входы и выходы которого являются контрольными входами и выходами устройства, управляющим выходом и информационньми входами устройства являются четвертый выход блока управления и вторые входы усилителей считывания, о т л и ч а ю щ ее с я тем, что, с целью повышения точности контроля, в него введены второй формирователь стробирующих сигналов, вторая группа формирователей управляющих сигналов, триггер, . { вторая и третья группы элементов И, S второй и. третий элементы ИЛИ и BtoW рая группа элементов зпдержки, входы которых подключены к выходу перС вого Формиров ателя стробирующ1йс сигналов, а выходы - к входам формирователей управляющих сигналбв второй группы, выходы которых соединены с первыми входами элементов И второй группы, выходы ксторых подключены к входам второго элемента ИЛИ, выход которого соединен с входом второго Формирователя стробирующих сигналов, выход которого подключен к третьим со входам усилителей считывания, выходы СХ) которых соединены с входами элементов И третьей группы, выходы которых подключены к входам регистра числа, причем вторые входы элементов И второй группы соединены с выходом триггера, входы которого подключены соответственно к входам элементов задеряоси первой группы и к выходу :третьего элемеита ИЛИ, входы которо:го соединен; с выходами элементов И первой группы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ правки пары торцевых алмаз-НыХ КРугОВ СВОбОдНыМ АбРАзиВОМ | 1978 |

|

SU795916A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU898508A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| . | |||

Авторы

Даты

1983-10-23—Публикация

1982-03-26—Подача