Изобретение относится к вычислительной технике, в частности к запо- минаюп1им устройствам, и может быть использовано при построении вычислительных систем.

Цель изобретения - повьппение надежности устройства.

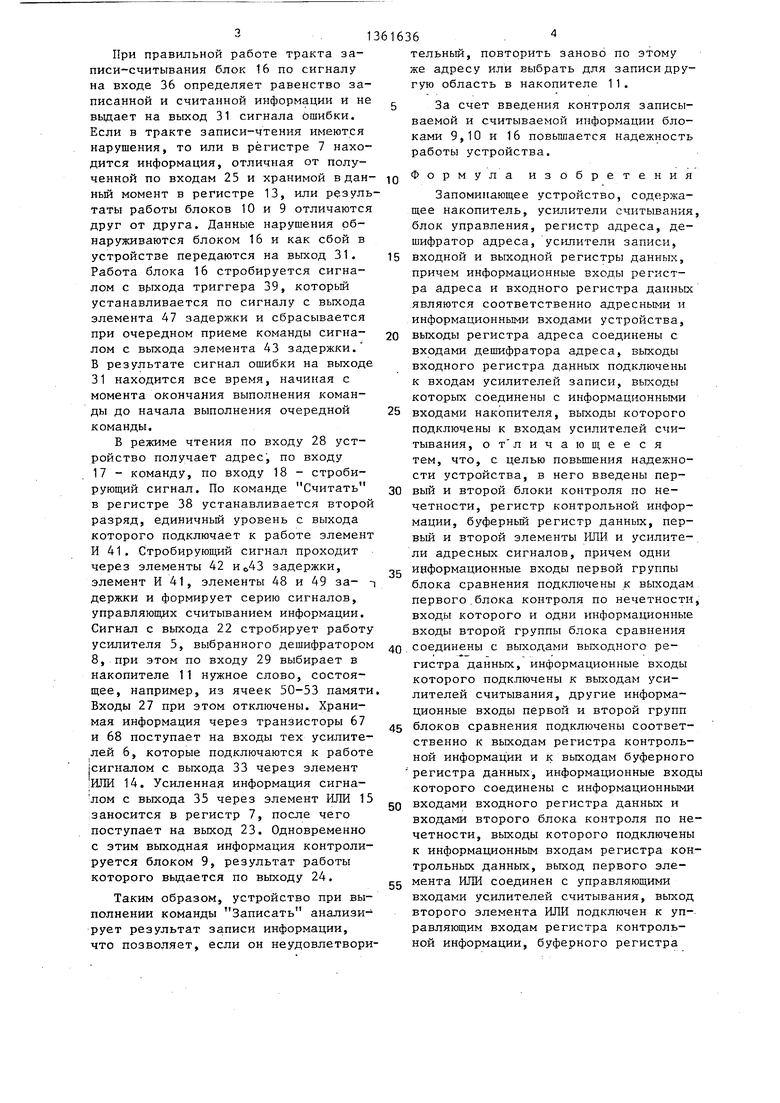

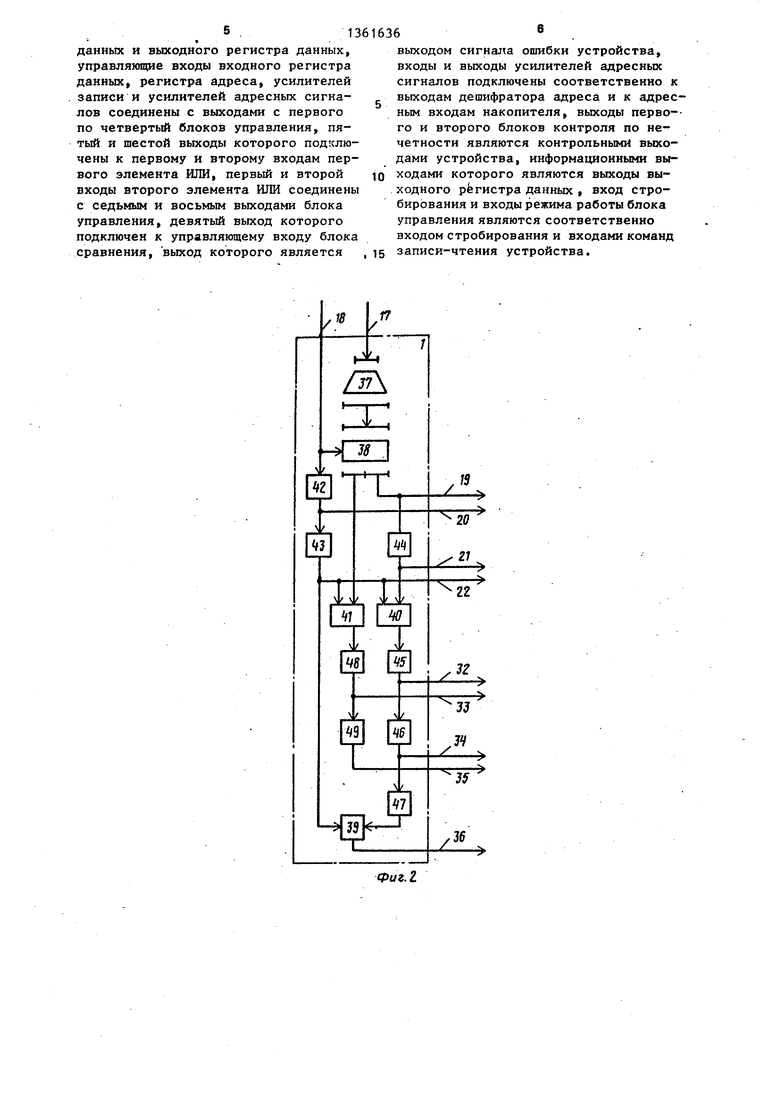

На фиг.1 изображена функциональная схема запоминающего устройства на фиг,2 и 3 - функциональные схемы соответственно блока управления и накопителя на фиг.4 - принципиальная схема ячейки памяти накопителя.

Устройство содержит блок 1 управления, входной регистр 2 данных, регистр 3 адреса, усилители 4 записи, усилители 5 адресных сигналов, усилители 6 считывания, выходной регистр 7 данных, дешифратор 8 адреса, первый 9 и второй 10 блоки контроля по нечетности, накопитель 11, регистр 12 контрольной информации, буферныйч регистр 13 данных, первый 14 и вто13616362

гистре 38. По команде Запись в регистре 38 устанавливается первый разряд, единичный уровень с выхода коg торого после задержки элементов 44 подключает к работе элемент И 40, Передний фронт этого сигнала является управляющим сигналом на вьгходах 19 и 21.

10 Стробирующий сигнал, проходящий по цепи, состоящей из элементов 42 и 43 задержки, элемента И 40, элементов 45-47 задержки и триггера 39, организует выработку серии управляющих

15 сигналов, которые обеспечивают выполнение команды записи в устройстве. Сигналом на выходе 19 запоминается в регистре 2 записываемая информация. Сигналом на выходе 20 запоминается

20 в регистре 3 адрес. Сигналы с выходов элементов 44 и 43 задержки по выходам 21 и 22 стробируют работу выбранных усилителей 4 и 5, В результате работы выбранного из усилителей 5 по одрой 15 элементы ИЛИ и блок 16 сравне- 25 ному из входов 29 выбирается одно

НИН, а также вход 17 команд записи- чтения, вход 18 стробирования устройства, выходы 19-22 с первого по чет- вертьш блока 1 управления, информационные выходы 23, один из контрольных выходов 24, информационные входы 25, другие контрольные выходы 26 устройства, информационные входы 27 накопителя 11, адресные входы 28 устройства, адресные входы 29 и выходы 30 накопителя 11, выход 31 сигнала ошибки устройства, выходы 32-36 с пятого по девятый блока 1 управления. Блок 1 управления содержит (фиг.2) дешифратор 37, регистр 38, триггер 39, элементы И 40 и 41 с первого по восьмой элементы 42-49 задержки. Накопитель 41 содержит (фиг.З) ячейки 50-65 памяти, каждая из которых содержит (фиг.4) МОП-транзисторы 66-68..

Устройство работает следующим образом,

В режиме записи по входу 25 устройство получает информацию для записи, по входу 28 - адрес, по входу

17 - команду и по входу 18 - строби- рующий сигнал. Полученная информация анализируется блоком 10 на наличие в ней нарушений по нечетности. Результат анализа блок 10 вьщает на выход 26, Одновременно в блоке 1 дешифратор 37 дешифрирует полученную команду, которая по сигналу, полученному по входу 18, запоминается в ре0

из слов накопителя 11, например слово, состоящее из ячеек 58-61 памяти

(фиг.З)., По данному сигналу, поступающему

0 на входы 30 (фиг.4), в каждой

ячейке памяти данного слова открываются транзисторы 66 и 68, Транзистор 66 обеспечивает по входам 27 поступление с выходов усилителей 4 ин5 формации для записи. Транзистор 68 обеспечивает через транзистор 67 по выходу 30 поступление хранимой на паразитных конденсаторах информации, . В результате этого на выходах 30 некоторое время присутствует старая информация, а после записи - новая ий- формация. Сигнал с выхода элемента 45 задержки по выходу 32 через элемент ИЛИ 14 подключает к работе уси5 лители 6 в момент поступления на их входы новой считанной информации. Сигнал с выхода элемента 46 задержки через элемент ИЛИ 15 (фиг.1) обеспечивает занесение усиленной информа- .

0 ции в регистр 7. Одновременно с этим в регистры 12 и 13 этот же сигнал заносит соответственно результат работы блока 10 и информацию, полученную для записи по входам 25. Это необхо5 димо для сохранения записываемой информации (после сброса ее с входов 25), последующего сравнения ее с результатом работы блока 9 и считанной в регистр 7 информации.

При правильной работе тракта записи-считывания блок 16 по сигналу на входе 36 определяет равенство записанной и считанной информации и не вьщает на выход 31 сигнала ошибки. Если в тракте записи-чтения имеются нарушения, то или в регистре 7 находится информация, отличная от полученной по входам 25 и хранимой в дан- ньй момент в регистре 13, или результаты работы блоков 10 и 9 отличаются друг от друга. Данные нарушения обнаруживаются блоком 16 и как сбой в устройстве передаются на выход 31. Работа блока 16 стробируется сигналом с в{ 1хода триггера 39, которьй устанавливается по сигналу с выхода элемента 47 задержки и сбрасывается при очередном приеме команды сигналом с выхода элемента 43 задержки. В результате сигнал ошибки на выходе 31 находится все время, начиная с момента окончания выполнения команды до начала выполнения очередной команды.

В режиме чтения по входу 28 устройство получает адрес, по входу 17 - команду, по входу 18 - строби- рующий сигнал. По команде Считать в регистре 38 устанавливается второй разряд, единичный уровень с выхода которого подключает к работе элемент И 41. Стробирующий сигнал проходит через элементы 42 Ио43 задержки, элемент И 41, элементы 48 и 49 за- т держки и формирует серию сигналов, управляющих считыванием информации. Сигнал с выхода 22 стробирует работу усилителя 5, выбранного дешифратором 8, при этом по входу 29 выбирает в накопителе 11 нужное слово, состоящее, например, из ячеек 50-53 памяти Входы 27 при этом отключены. Хранимая информация через транзисторы 67 и 68 поступает на входы тех усилителей 6, которые подключаются к работе сигналом с выхода 33 через элемент ИЛИ 14. Усиленная информация сигна- лом с выхода 35 через элемент 1-ШИ 15 заносится в регистр 7, после чего поступает на выход 23. Одновременно с этим выходная информация контролируется блоком 9, результат работы которого вьщается по выходу 24.

Таким образом, устройство при выполнении команды Записать анализирует результат записи информации, что позволяет, если он неудовлетвори0

0

5

тельный, повторить заново по этому же адресу или выбрать для записи другую область в накопителе 11.

За счет введения контроля записываемой и считываемой информации блоками 9,10 и 16 повьшается надежность работы устройства.

Формула изобретения

Запоминающее устройство, содержащее накопитель, усилители считывания, блок управления, регистр адреса, дешифратор адреса, усилители записи,

5 входной и выходной регистры данных, причем информационные входы регистра адреса и входного регистра данных являются соответственно адресными и информационными входами устройства, выходы регистра адреса соединены с входами дешифратора адреса, выходы входного регистра данных подключены к входам усилителей записи, выходы которых соединены с информационными входами накопителя, выходы которого подключены к входам усилителей считывания, oт личaюD eecя тем, что, с целью повьш ения надежности устройства, в него введены пер0 вый и второй блоки контроля по нечетности, регистр контрольной информации, буферный регистр данных, первый и второй элементы ЖИ и усилители адресных сигналов, причем одни информационные входы первой группы блока сравнения подключены к выходам первого.блока контроля по нечетности, входы которого и одни информационные входы второй группы блока сравнения

0 соединены с выходами выходного регистра данных, информационные входы которого подключены к выходам усилителей считывания, другие информационные входы первой и второй групп

5 блоков сравнения подключены соответственно к выходам регистра контрольной информации и к выходам буферного регистра данных, информационные входы которого соединены с информационными

0 входами входного регистра данных и входами второго блока контроля по нечетности, выходы которого подключены к информационным входам регистра контрольных данных, выход первого элеg мента ИЛИ соединен с управляющими входами усилителей считывания, выход второго элемента ИЛИ подключен к управляющим входам регистра контрольной информации, буферного регистра

5

данных и выходного регистра данных, управляющие входы входного регистра данных, регистра адреса, усилителей записи и усилителей адресных сигналов соединены с выходами с первого по четвертый блоков управления, пятый и шестой выходы которого подключены к первому И второму входам первого элемента ИЛИ, первый и второй входы второго элемента ИЛИ соединены с седьмым и восьмым выходами блока управления, девятый выход которого подключен к управляющему входу блока сравнения, выход которого является

выходом сигнала ошибки устройства, входы и выходы усилителей адресных сигналов подключены соответственно к выходам дешифратора адреса и к адресным входам накопителя, выходы перво-- го и второго блоков контроля по нечетности являются контрольными выходами устройства, информационными выходами которого являются выходы выходного регистра данных , вход стро- бирования и входы режима работы блока управления являются соответственно входом стробирования и входами команд записи-чтения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU847377A1 |

| Запоминающее устройство | 1982 |

|

SU1016832A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1986 |

|

SU1439679A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Запоминающее устройство | 1985 |

|

SU1298800A1 |

| Запоминающее устройство | 1982 |

|

SU1062787A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Запоминающее устройство с обнаружением одиночных ошибок | 1979 |

|

SU855738A1 |

/

Фиг.

У

Редактор В.Петраш

Составитель Т.Зайцева

Техред М.ДНДЫК Корректор А.Тя.ско

Заказ 6297/52 Тираж 588Подписное

ВНИИПИ Государственного коьштета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

J

X

6В

| Оперативное запоминающее устройство | 1982 |

|

SU1061175A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ,(54) ЗАПОМИНАЩЕЕ УСТРОЙСТВО ,(57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено при построении вычислительных систем | |||

| Целью изобретения является повышение надежности устройства | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Надежность устройства повьшает- ся за счет обеспечения контроля при записи и чтении информации | |||

| Насос | 1917 |

|

SU13A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

Авторы

Даты

1987-12-23—Публикация

1986-05-06—Подача