(54) УСТРОЙСТВО ДЛЯ ВВОДА И В1..:ВОДА И1(Т ОРМАЦМ11

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для программной диагностики каналов ввода-вывода и интерфейса | 1980 |

|

SU932498A1 |

| Мультиплексный канал | 1980 |

|

SU879580A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для управления каналами | 1976 |

|

SU641436A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для ввода-вывода информации в вычислительных системах.

Известно устройство для ввода и вывода информации, содержащее блок связи с центральным npoueccopori, регистр адреса каналов, регистр запросов, дешифратор запросов, блок контроля и каналы ввода-вывода, которые связаны между собой и входами-выходами процессора, системой информационных адресных и управляю1ЧИХ ШИ}1 1 .

Недостатком устроГютва является сравнительно невысокая надежность из-за отсутствия проверки узла контроля в процессе работы.

Наиболее близким по технической сущности к предлагаемому является устройство для ввода и вывода информации, содержащее блок контроля, первый вход которого подключен к первому выходу блока сопряжения и к

первым входам первого и второго селекторных каналов, второй вход блока контроля - ко второму выходу блока сопряжения, к первому входу мультиплексного канала и к вторым входам первого и второго селекторных каналов, третий и четвертый входы блока контроля - к третьему и четвертому выходам блока сопряжения, пятый вход подключен к первым

10 выходам мультиплексного и селекторных каналов, к первому входу блока сопряжения, шестой вход блока контроля подключен ко вторым выходам селекторных каналов и ко второ15му входу блока сопряжения, седьмой вход блока контроля подключен ко второму выходу мультиплексного канала и к третьим выходам селекторных каналов, третий и четвертый входы

20 блока сопряжения соответственно подключены к первому и второму входам устройства, пятый и шестой выходы подключены соответственно 3 к первому и второму выходам устройства, третий вход которого подсоединен к первым входам первого и второго регистров, к восьмому входу блока контроля, к нулевому входу первого триггера, ко второму входу мультиплексного и к третьим входам селекторных каналов, третий выход - к первому выходу дешифратора, четвертый выход - к выходу первого триггера,второй выход дешифратора соединен со вторым входом первого регистра, первый выход кото рого подключен к первому входу деши ратора и к пятому входу блока сопряжения, седьмой выход которого соедии ен с третьим входом мультиплексного канала и с четвертыми вхо дами селекторных каналов, четвертые выходы которых соединены с третьим выходом мультиплексного канала и со вторыми входами второго регистра, пятые выходы селекторных каналов соответственно с пятым и шестым выходами устройства, шестые выходьг с шестым и седьмьи выходами устройс ва соответственноV пятые входы еелекторных каналов - с четвертым и п тым входами устройства соответствен шестые входы-с шестым и седьмым вхо дами устройства соответствен1|О, четвертый и пятый входы мультиплекс ного канала подключены к восьмому и девятому входам устройства соотве ственно, а четвертый и пятый выходы - к седьмому и восьмому выходам устройства соответственно, выход второго регистра соединен со вторым входом дешифратора 23Недостатком устройства является снижение его надежности, которое вы зывается возникновением ошибок в блоке контроля информации. Целью изобретения является повышение надежности устройства. Указанная цель достигается тем, что в устройство для ввода и вывода информации, содержащее блок контрол первый вход которого подключен к первому вы-ходу блока сопряжения и к первым входам первого и второго селекторных каналов, второй вход бл ка контроля - ко второму выходу бло ка сопряжения, к первому входу муль типлексного канала и к вторым входам первого и второго селекторных каналов, третий и четвертый входы блока контроля - к третьему и четвер1тому выходам блока сопряжения соответственно, пятый вход - к первым выходам мультиплексного и селекторных каналов и к первому входу блока сопряжения, шестой вход блока контроля подключен ко вторым выходам селекторных каналов и ко второму входу блока сопряжения, седьмой вход подключен ко второму выходу мультиплексного канала и к третьим выходам селе1{торных каналов, третий и четвертый входы блока сопряжения соответственно подключены к первому и второму входам устройства, пятый и шестой выходы - соответственно к первому и второму выходам устройства,третий вход которого подсоединен к первым входам первого и второго регистров, к восьмому входу блока контроля, к нулевому входу первого триггера; ко второму входу мультиплексного и к третьим входам селекторных каналов, третий выход - к первому выходу дешифратора, четвертый выход к выходу первого триггера, второй выход дешифратора соединен со вторым входом первого регистра, первый выход которого подключен к первому входу дешифратора и к пятому входу блока сопряжения, седьмой выход которого соединен с третьим входом мультиплексного канала и с четвертыми, входами селекторных каналов, четвертые выходы которых соединены с третьим выходом мультиплексного канала и со вторыми-входами второго регистра, пятые выходы соответственно - с седьмым и восьмыг.1 выходами устройства, пятые входы селекторных каналов соответственно - с четвертым и пятым входами устройства,шестые входы соответственно с шестым и седьмым входами устройства,, четвертый и пятые входы мультиплексного канала подключены соответственно к восьмому и девятому входам устройства, а четвертый и пять;й выходы - к девятым и десятым выходам устройства соответственно, выход второго регистра соединен со вторым входом дешифратора, введены первый и второй И, первый и второй элементы И-НЕ, элементы ЗИ-211ЛЯ, второй и третий триггеры, выход второго триггера соединен с девятым входом блока контроля, группа выходов которого подключена к группам входов первого и втЪрого элементов Н-НЕ, второй выход первого регистра

соединен со входами первого элемента И, выход которого подключен к входам второго и третьего триггера и к первым входам элемента ЗИ-2ИЛИ, вторые входы которого сое- динены с третьим входом устройства и с единичными и нулевыми входами второго и третьего триггеров,третьи входы ЗИ-2КЛИ соединены с выходами соответствующих элементов И-НЕ, выход соединен с единичным входом первого триггера, выход первого элемента И-НЕ подключен к первому входу второго элемента И,второй входкоторого соедийен с третьи ВХОДОМ устройства, третий вход второго элемента И соединен с выходом второго триггера, а выход второго элемента И соединен с десятым входо блока контроля.

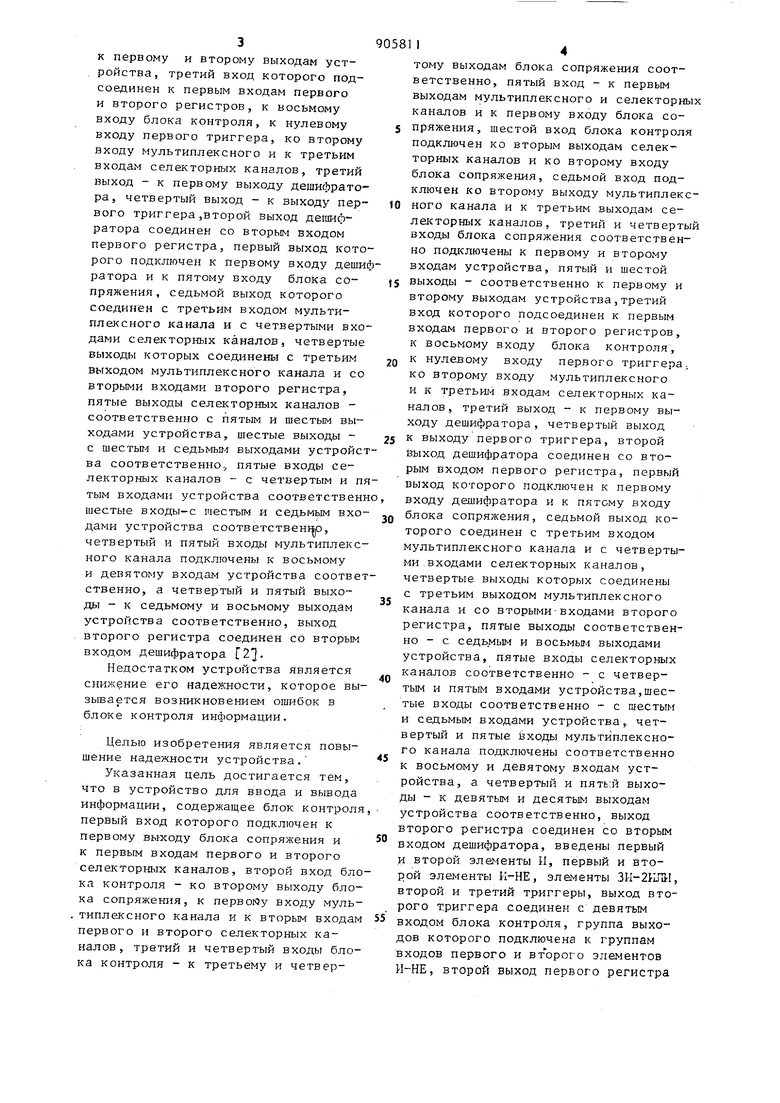

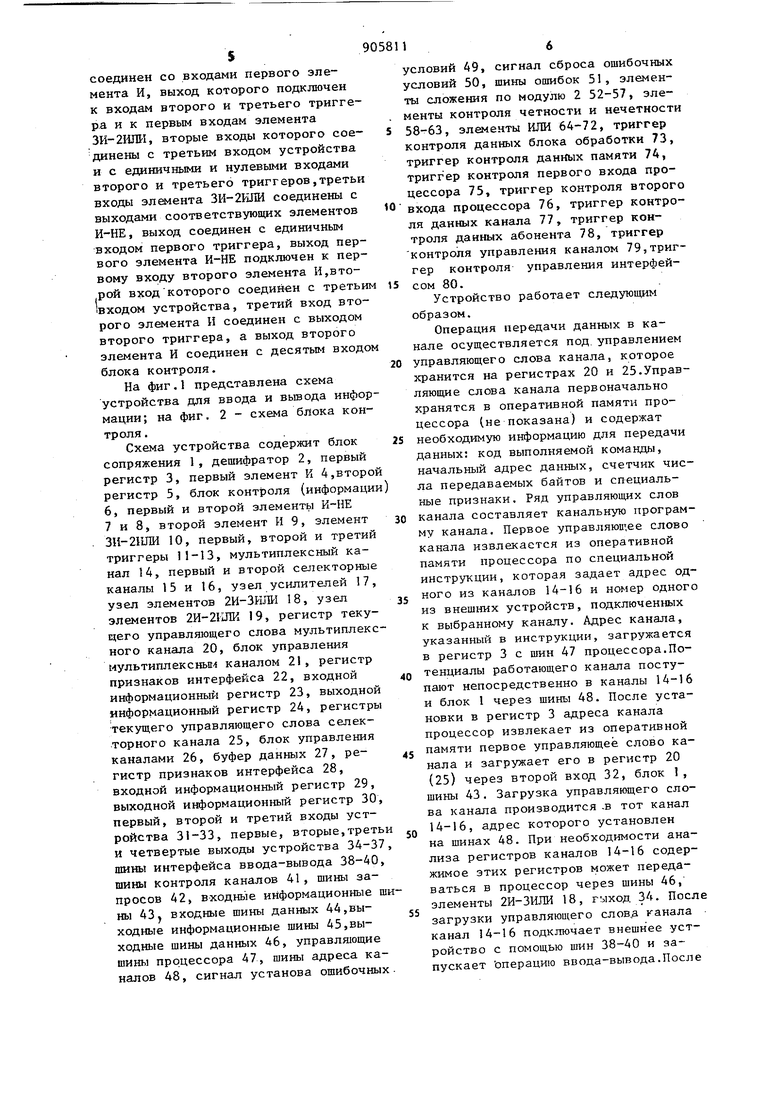

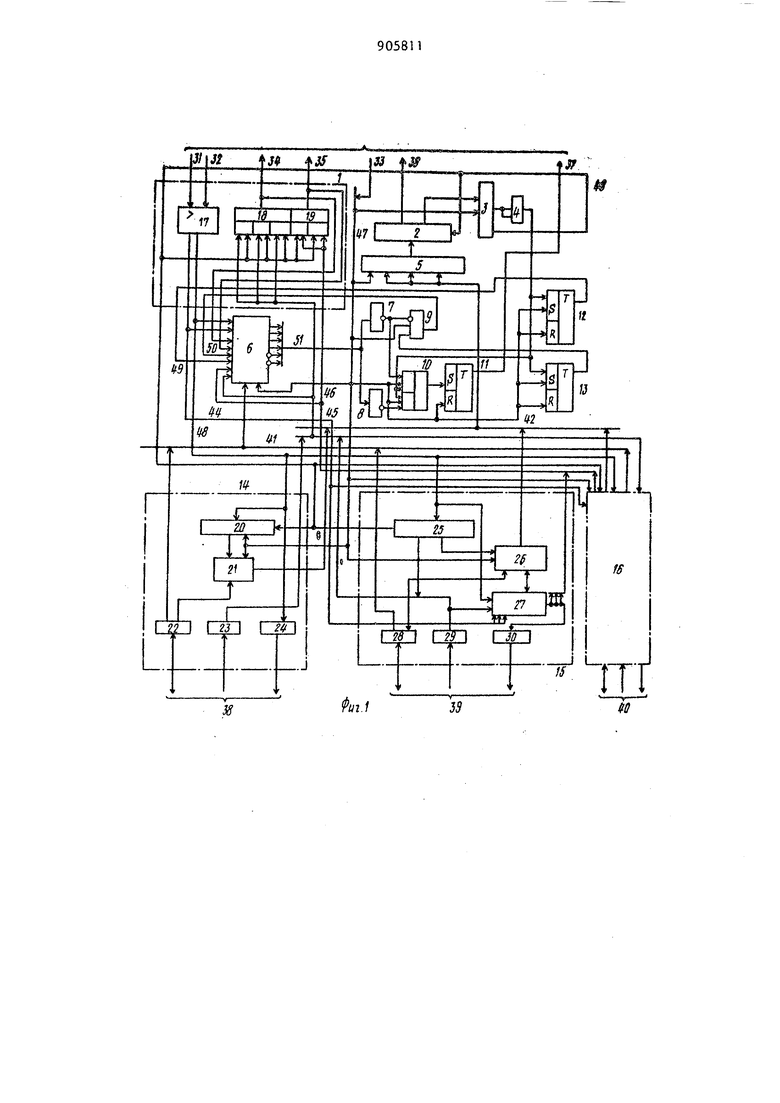

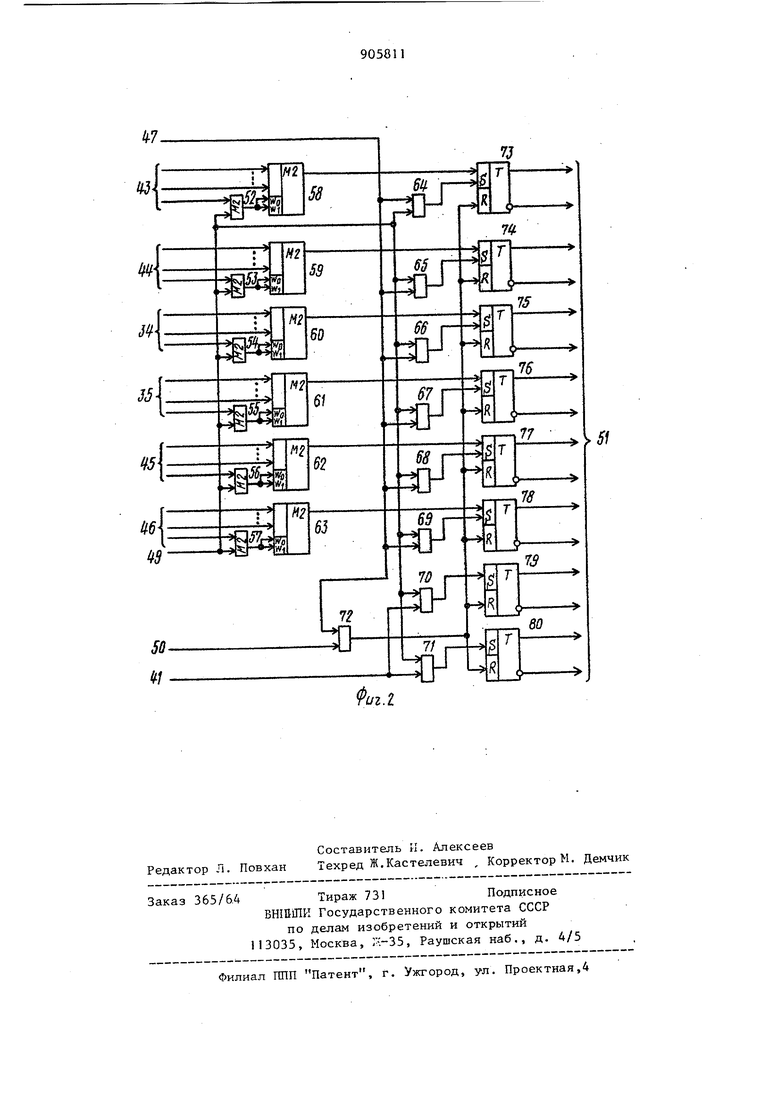

На фиг.1 представлена схема устройства для ввода и вьшода информации; на фиг. 2 - схема блока контроля .

Схема устройства содержит блок сопряжения 1, дешифратор 2, первый регистр 3, первый элемент К 4,второ регистр 5, блок контроля (информаци 6, первый и второй элементы И-НЕ 7 и 8, второй элемент И 9, элемент ЗН-211Ш 10, первый, второй и третий триггеры 11-13, мультиплексный канал 14, первый и второй селекторные каналы 15 и 16, узел усилителей 17, узел элементов 2И-ЗИЛИ 18, узел элементов 2И-21ШК 19, регистр текущего управляющего слова мультиплексного канала 20, блок управления мультиплексным каналом 21, регистр признаков интерфейса 22, входной информационный регистр 23, выходной информационный регистр 24, регистры текущего управляющего слова селекторного канала 25, блок управления каналами 26, буфер данных 27, регистр признаков интерфейса 28, входной информационный регистр 29, выходной информационный регистр 30, первый, второй и третий входы устройства 31-33, первые, вторые,треть и четвертые выходы устройства 34-37 шины интерфейса ввода-вывода 38-40, шины контроля каналов 41, щины запросов 42, входные информационные шны 43, входные шины данных 44,выходные информационные шины 45,выходные шины данных 46, управляющие шины процессора 47, шины адреса каналов 48, сигнал установа ошибочных

условий 49, сигнал сброса ошибочных условий 50, шины ошибок 51, элементы сложения по модулю 2 52-57, элементы контроля четности и нечетност 58-63, элементы ИЛИ 64-72, триггер контроля данных блока обработки 73, триггер контроля данных памяти 74, триггер контроля первого входа процессора 75, триггер контроля второг входа процессора 76, триггер контроля данных канала 77, триггер контроля данных абонента 78, триггер контроля управления каналом 79,триггер контроля управления интерфейсом 80.

Устройство работает следующим образом.

Операция передачи данных в канале осуществляется под. управлением управляющего слова канала, которое хранится на регистрах 20 и 25.Управляющие слова канала первоначально хранятся в оперативной памяти процессора (.не показана) и содержат необходимую информацию для передачи данных: код выполняемой команды, начальный адрес данных, счетчик числа передаваемых байтов и специальные признаки. Ряд управляющих слов канала составляет канальную программу канала. Первое управляющее слово канала извлекается из оперативной памяти процессора по специальной инструкции, которая задает адрес одного из каналов 14-16 и номер одног из внешних устройств, подключенных к выбранному каналу. Адрес канала, указанный в инструкции, загружается в регистр 3 с шин 47 процессора.Потенциалы работающего канала поступают непосредственно в каналы 14-16 и блок 1 через шины 48. После установки в регистр 3 адреса канала процессор извлекает из оперативной памяти первое управляющее слово канала и загружает его в регистр 20 (25) через второй вход 32, блок 1, шины 43. Загрузка управляющего слова канала производится -в тот канал 14-16, адрес которого установлен на шинах 48. При необходимости анализа регистров каналов 14-16 содержимое этих регистров может передаваться в процессор через шины 46, элементы 2И-ЗИЛИ 18, гыход 34. Посл загрузки управляющего словд канала канал 14-16 подключает внешнее устройство с помощью шин 38-40 и запускает операцию ввода-вывода.После запуска операции ввода-вывода устройство освобождает процессор для выполнения последующих инструкций и продолжает эту операцию,используя информацию, расположенную на регистрах канала, при помощи следующих микропрограмм: обслуживание передач данных, обслуживание выборки управляющего слова, обслуживание прерывания по вводу-выводу. При необходимости вызвать соответствующую микропрограмму канал устанавливает соответствующий запрос, который через группу шин 42 поступает в регистр 5, выходы которого поступают в дешифратор 2. Дешифратор 2 формирует сигнал запроса, поступающий в процессор через выход 36 и в регист адреса канала,запрос которого будет обслуживаться. Получив сигнал запроса,процессор приостанавливает работу по обслуживанию инструкций процессора, вызывается соответствующая микропрограм ма обслуживания запроса канала. В случае обслуживания передачи данных селекторного канала при выполнении операции считывание данные поступаю из буфера 27 в процессор через шины 46, элементы 2И-2ИЛИ 19 и выход 35. В случае выполнения операции йаписи данные, поступающие из процессора ч рез выход 31 и шины 44, заносятся в буфер 27, далее через регистр 30 они поступают во внешнее устройство Б процессе выполнения операции ввода-вывода в канале производится контроль блоком 6 всех этапов выполнения операции ввода-вывода.При этом контролируется поток управляющих и информационных трактов,работа интерфейса ввода-вывода. При обнаружении сбоя (отказа) в работе кана выполнение операции ввода-вывода прекращается и производится прерывание по вводу-выводу. Контроль работы блока 6 осуществляется в тот момент времени,когда устройство не обслуживает запросов от каналов, т.е. находится в состоя НИИ ожидания. Это означает, что триггеры регистра 3 сброщены и элемент И 4 формирует сигнал ожидания, который совместно с управляющим сиг налом с шин 33 устанавливает в единичное состояние триггеры 11 и 12. Сигнал с единичного выхода триггера I1 поступает в блок 6 на вторые вхо ды элементов 52-57 (фиг.2), для ийвертирования контрольных разрядов информации, поступающей по шинам 34, 35, 43-46 на первые входы указанных злементов. Таким образом, выходы элементов 58-63 формируют ошибку по четности. Условия, при которых проверяется четность информации, также создаются сигналом с единичного выхода триггера 11, и через элементы 64-69 устанавливают триггеры контроля 73-78. Триггеры 79,80, контролирующие работу аппаратуры канала и интерфейса, также устанавливаются через элементы 70, 71 сигналом с единичного выхода триггера 1I.После установки в единичное состояние триггеров 73-8D их единичные выходы поступают для анализа на элемент 7. Если какой-либо из триггеров не установился, то по выходу элемента 7 и при наличии состояния ожидания (выход элемента 4 в единичном состоянии) через элемент 10 устанавливается триггер 13. Сигнал с единичного выхода триггера 13 поступает на четвертый выход 37 и указывает на неверную работу схам контроля. Если все триггеры 73-80 установились,то триггер 11 сбрасывается по управляющему сигналу с шин 33, и выход элемента 9 вырабатывает сигнал, который поступает в блок 6 на второй вход элемента 72, выход которого сбрасывает триггеры 73-80. После сброса в нулевое состояние триггеров 73-80 нулевые выходы поступают для анализа на элемент 8. Если какой-либо из триггеров не сбросился, то по выходу элемента 8 и при наличии состояния ожидания через элемент 10 устанавливается триггер 13, указывая на неверную работу схем контроля.Если все триггеры 73-80 сбросились, то триггер 12 сбрасывается по управляющему сигналу с шин 33. Далее, вновь производится анализ состояния устройства по выходу элемента 4. Если устройство остается в состоянии ожидания, то описанный цикл проверки работы блока 6 повторяется.Если в момент цикла проверки состояние ожидания сбрасывается, то цикл проверки заканчивается, но триггер 13 не устанавливается. Введение отличительных признаков устройства,, позволяющее осуществить контроль блока 6, увеличивает достоверность контроля передачи ин9формации, за счет чего достигается повышение надежности устройства. Формула изобретения Устройство для ввода и вывода информации, содержащее блок контрол первы вход которого подключен к первому выходу блока сопряжения и к первым входам первого и второго селекторных каналов, второй вход блока контроля - к второму выходу блока сопряжения, к первому входу мультиплексного канала и к вторым входам первого и второго селекторны каналов, третий и четвертый входы блока контроля - к третьему и четвертому выходам блока сопряжения,п тый вход подключен к первым выходам мультиплексного и селекторных каналов, к первому входу блока сопряжения, шестой вход блока контрол подключен к вторым выходам селектор ных каналов и к второму входу блока сопряжения, седьмой вход подключен к второму выходу мультиплексного ка нала и к третьим выходам селекторны каналов, третий и четвертый входы блока сопряжения соответственно подключены к первому и второму входам устройства, пятый и шестой выходы подключены соответственно к первому и второму выходам устройств третий вход которого подсоединен к первым входам первого и второго регистров,к восьмому входу блока контроля, к нулевому входу первого триггера, к второму входу мультиплексного и к третьим входам селекторных каналов, третий выход - к первому выходу дешифратора, четвертый выход - к выходу первого триггера, второй выход дешифратора t соединен с вторым входом первого регистра, первый выход которого под ключен к первому входу дешифратора и к пятому входу блока сопряжения, седьмой выход которого соединен с ,третьим входом мультиплексного канала и с четвертыми входами селекторных каналов, четвертые выходы которых соединены с третьим выходом мультиплексного канала и с вторыми входами второго регистра, пятые выХОДЫ селекторных каналов - соответственно с пятым и шестым выходами устройства, шестые выходы - с шестьтм и седьмым выходами устройства соответственно, пятые входы селекторных каналов соответственно - с четвертьм и пятым входами устройства, шестые входы соответственно - с шестым и седьмым входами устройства, четвертый и пятый входы мультиплексного канала подключены соответственно к восьмому и девятому входам устройства, а четвертый и пятый выходы - к седьмому и восьмому выходам устройства соответственно, выход второго регистра соединен с вторым в.ходом дешифратора, отличающееся тем, что, с целью повьш1ения надежности устройства, в него введены первый и второй элементы К, первый и второй элементы И-ИЕ, элемент ЗИ-21Ш11, второй и третий триггеры, выход второго триггера соединен с девятым входом блока контроля, группа выходов которого подключена к группам входов первого и второго элементов II-IIE, второй выход первого регистра соединен с входами первого элемента И, выход которого подключен к входам второго и третьего триггера и к первым входам элемента ЗИ-2ШМ, вторые входы которого соединены с третьим входом устройства и с единичными и нулевыми входами второго . и третьего триггеров, третьи входы элемента ЗИ-2ИЛИ соединены с выходами соответствующих элементов И-НЕ, выход соединен с единичным входом первого триггера, выход первого элемента И-НЕ подключен к первому входу второго элемента И, второй вход которого соединен с третьим входом устройства, третий вход второго элемента И соединен с выходом второго триггера, а выход второго элемента И соединен с десятым входом блока контроля. Источники информации, принятые во внимание нри экспертизе 1.Патент CI1IA К 3453600, кл. G 06 F 3/ОА, 1975. 2.Качков Б.П. и др. Электронная вычислительная машина ЕС-1022. М., Статистика, 1979, с. 35-75 (прототип).

иг.1

3S

fO

}S

Авторы

Даты

1982-02-15—Публикация

1980-03-04—Подача