(54) yCTPOJJCTBO ДЛЯ КОНТЮЛЯ ИНТЕГРАЛЬНЫХ БЛОКОВ ОПЕРАТИВНОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU894796A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1024920A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

1

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля блоков оперативной памяти, содержащее генератор импульсов, программный блок, элемент ЗАПРЕТ, коммутатор, блок индикации и блок обнаружения короткого замыкания обмоток матриц 11 .

Однако это устройство невозможно применять для контроля интегральных блоков памяти.

Наиболее близким к предлагаемому техническим решением является устройство, содержащее микропрограммный блок команд, первый выход которого подключен ко входу блока адресации, а второй выход - ко входу генератора контрольных данных, выход которого подключен к первому входу блока сравнения и первому входу /проверяемого интегрального ОЗУ, выход которого через регистр приема информации соединен со вторым входом блока сравнения, выход которого подключен ко входу микропрограммного блока команд 2.

Недостатками этого устройства являются низкое быстродействие, поскольку проверка каждой ячейки контролируемого блока памяти осуществляется за пять циклов обращения к памяти, и недостаточная надежность, поскольку оно не обеспечивает проверку наличия взаимных связей между ячейками, расположенными в одной и той же половине паМяти.

Цель изобретения - повьщ1ение быстродействия и надежности устройства.

10

Поставленная цель достигается тем, что в устройство для контроля интегральных блоков оперативной памяти, содержащее адресный блок, формирователь контрольных сигналов, схему сравнения, регистр числа и блок

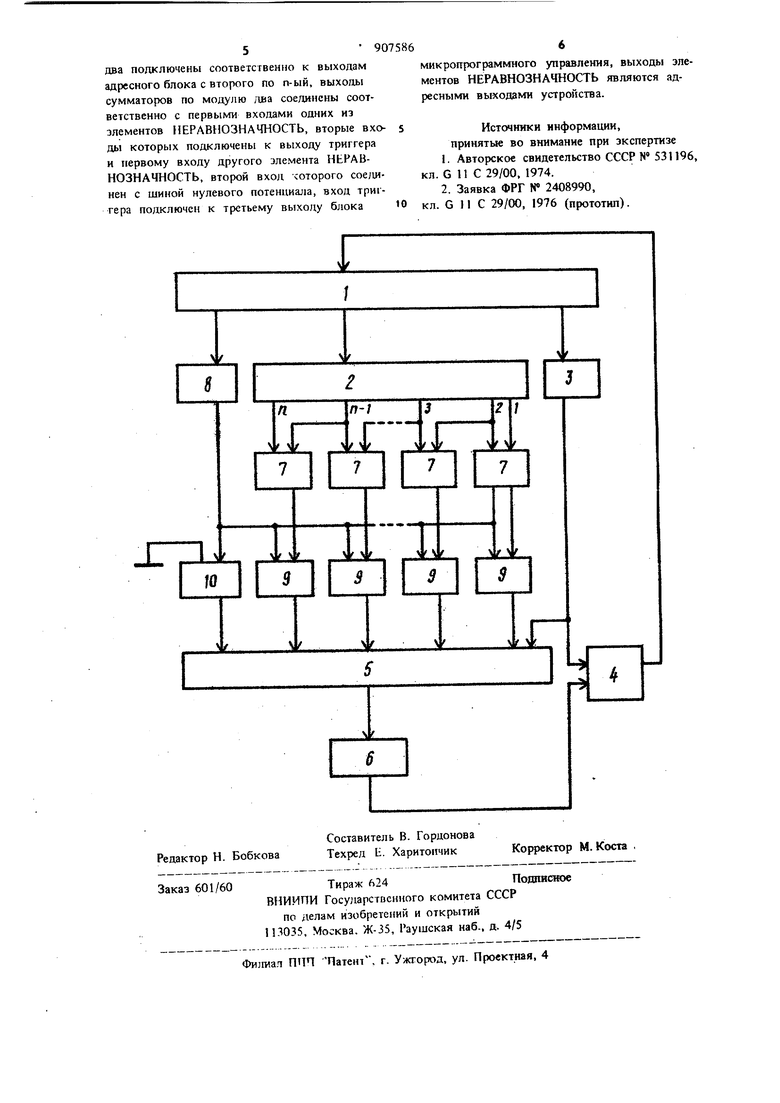

15 микропрограммного управления, вход которого соединен с выходом схемы сравнения, первый выход - с входом адресного блока, а второй выход - с входом формирователя контрольных сигналов, выход которого ключен к первому входу схемы сравнения и является контрольным выходом устройства, второй вход схемы сравнения соединен с выходом регистра числа, входы которого явля390ются входами устройства, введены сумматоры по модулю два, триггер и элементы НЕРАВНОЗНАЧНОСТЬ, причем первые входы сумматоров по модулю два соединены соответственно с выходами адресного блока с пер вого по (п-1)-ый, где п - количество раэртдов адресного блока, вторые входы сумматоров по модулю два подключены соответственно к выходам адресного блока со второго по П-ЫЙ , выходы сумматоров по модулю два соединены соответственно с первыми входами одних из элементов НЕРАВНО ЗНАЧНОСТЬ, вторые входы которых подклю чены к выходу триггера и первому входу другого элемента НЕРАВНОЗНАЧНОСТЬ, второй вход которого соединен с шиной нулевого потенциала, вход триггера подключен к третьему выходу блока микропрограммного управления, выходы элементов НЕРАВНОЗНАЧ НОСТЬ являются адресными выходами устрой ства. На чертеже изображена структурная схема предлагаемого устройства. Устройство содержит блок 1 микропрограммного управления, адресный блок 2, фор мирователь 3 контрольных сигналов, схему 4 сравнения, контролируемый интегральный блок 5 оперативной памяти, регистр 6 адсла, сумматоры 7 по модулю два, триггер 8, пред назначенный для формирования кода маски, и элементы НЕРАВНОЗНАЧНОСТЬ 9{)И 10. Устройство работает следующим образом. По программе блока 1 адресный блок 2 формирует двоичный код адреса, преобразование которого осуществляют сумматоры 7 по модулю два путем поразрядного сложения дв ичного кода адреса со сдвинутым вправо на один разряд значением данного кода. Таким образом получается преобразованный код (п-П разрядов адреса, причем код старшего п-го разряда адреса принимает значение нуль, для элемента НЕРАВНОЗНАЧНОСТЬ 10 соеданен с шиной нулевого потенциала. Преобразованный код адреса через элементы НЕРАВНОЗНАЧНОСТЬ 9 и 10 поступает на адресные входы проверяемого интеграль ного блока 5 оперативной памяти. Формирование контрольных данных осуществляется формирователем 3 по команде блока 1. Затем записывают нуль в первую ячейку проверяемого блока 5, по команде блока I включают триггер 8, формирующий код маски, и инвертируют код адреса при пг.мощи элементов НЕРАВНОЗНАЧНОСТЬ 9 и 10. Если число разрядов кода адреса четное, то инверсный код адреса имеет дополнекие До четности, равное нулю. В последнюю ячейку памяти блока 5 записывают нуль. Затем двоичный код адреса увеличивают на единицу, устанавливают триггер 8 в нулевое состояние и преобразуют код адреса при помощи сумматоров 7 и элементов НЕРАВНОЗНАЧНОСТЬ 9 и 10. По новому адресу записьшают единицу и пров();1ят проверку блока 5, как описано выше. Процесс преобразования адресов выполняется до тех пор. пока не заполняются информацией все ячейки проверяемого блока 5 оперативной памяти. Преобразование кода адреса при считывании осуществляется аналогичным образом. Считанная информация запоминается в регистf e 6. Схема 4 сравнения сравнивает информацию с выхода регистра бис выхода формирователя 3 контрольных сигналов. Результаты контроля поступают в блок 1. Таким образом, в устройстве обеспечивается непоследовательный обход ячеек памяти блока 5, при котором в каждом следующем цикле обращения код адреса изменяется в максимальном количестве разрядов, что исключает операции контроля четности кода адреса и упрощает команды управления формирователем 3 контрольных сигналов, за счет чего сокращается вржмя и повышается качество контроля. Устройство обеспечивает проверку взаимного влияния ячеек памяти и дешифраторов адреса блока 5. Технико-экономические преимущества предлагаемого устройства заключаются в более высоких, по сравнению с известным, быстродействии и надежности. Формула изобретения Устройство для контроля интегральных блоков оперативной памяти, содержащее адресный блок, формирователь контрольных сигналов, схему сравнения, регистр числа и блок микропрограммного управления, вход которого соединен с выходом схемы сравнения, первый выход - с входом адресного блока, а второй выход - с входом формирователя контрольных сигналов, выход которого подключен к первому входу схемы сравнения и является контрольным выходом устройства, второй вход схемы сравнения соединен с выходом регистра числа, входы которого являются входами устройства, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит сумматоры по модулю два,- триггер и элементы НЕРАВНОЗНАЧНОСТЬ, причем первые входы сумматоров по модулю два соединены соответственно с выходами адресного Рлока с первого по (п-1)-ый (где п - количество разрядов адресного блока), вторые входы сумматоров по модулю

два подключены соответственно к выходам адресного блока с второго по п-ый, выходы сумматоров по модулю два соединены соответственно с первыми входами одних из элементов НЕРАВНОЗНАЧНОСТЬ, вторые входы которых подключены к выходу триггера и первому входу другого элемента HtPABНОЗНАЧНОСТЬ, второй вход которого сое/шнен с шиной нулевого потенциала, вход триггера подключен к третьему выходу блока

микропрограммного управления, выходы элементов НЕРАВНОЗНАЧНОСТЬ являются адресными выходами устройства.

Источники информации, принятые во внимание при экспертизе

кл. G 11 С 29/00, 1976 (прототип).

Авторы

Даты

1982-02-23—Публикация

1980-06-16—Подача