та И, выход которого соединен с управляющим входом блока памяти и через первый элемент задержки - с первым информационным входом накапли- вающего сумматора, выход регистра кода операции соединен с вторым инфдрмационным входом регистра адреса и с первым входом четвертого блока элементов И, выход которого соединен с вторым входом первого сумматора по модулю два, второй выход регистра микрокоманд соединен с первым входом второго сумматора по модулю два и с первым входом третьего блока элементов И, выход которого соединен с третьим входом первого сумматора по модулю два, четвертый выход регистра .микрокоманд соединён с вторым входом четвертого блока элементов И, с вторым входом третьего блока элементов И и через второй элемент НЕ - с первым входом третьего И, выход которого через второй элемент

задержки соединен с управляющим входом формирователя адреса и с установочным входом peгиctpa логических условий, выход регистра логических условий соединен с вторым входом второго сумматора по модулю два, выход которого соединен с вторым входом второго блока элементов И, выход второго блока элементов И соединен с вторым информационным входом накапливающего сумматора, пятый выход регистра микрокоманд соединен с вторым входом первого элемента И, третьим входом четвертого блока элементов И, третьим входом третьего блока элементов И, входом первого элемента НЕ и вторым входом третьего элемен та И, шестой выход регистра микрокоманд соединен с вторым входом третьего элемента ИЛИ, третий вход устройства соединен с вторым входом второго элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Микропрограммный процессор с контролем | 1980 |

|

SU862144A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955058A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления с контролем функционирования, применяемых в ЭВМ и вычислитель ных системах.

Известно микропрограммное устройство управления, включающее в себя блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, счетЧик, сумматор, микрокоманд, триггер фиксации сбоя элементы И, ИЛИ, НЕ 1.

Недостатком указанного устройства является низкая оперативность контроля и большой объем контрольного оборудования.

Известно также микропрограммное устройство управления с контролем, срдержащее блок памяти, регистры адреса и микрокоманд, триггер сбоя, сумматор и логические элементы 2,

Недостатками этого устройства Я8ляЬтся НИЗК.ЗЯ оперативность контроля обусловленная формированием результата проверки в конце выполнения микропрограммы, и большой объем контрольного оборудования.

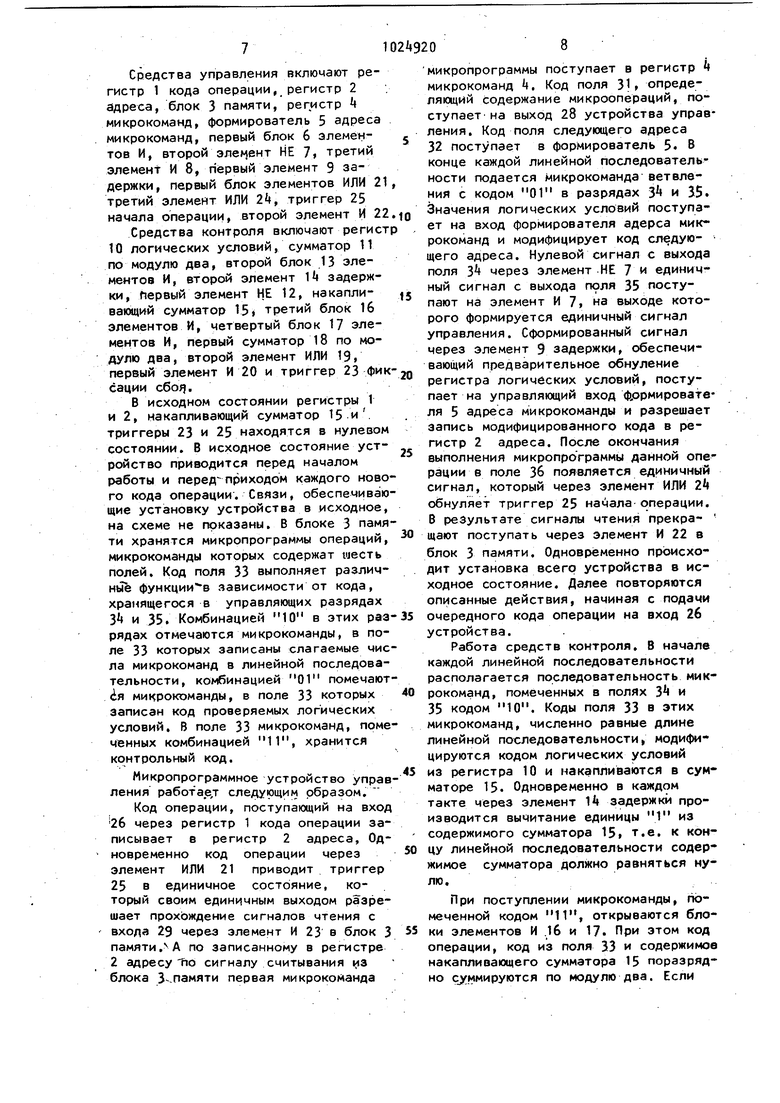

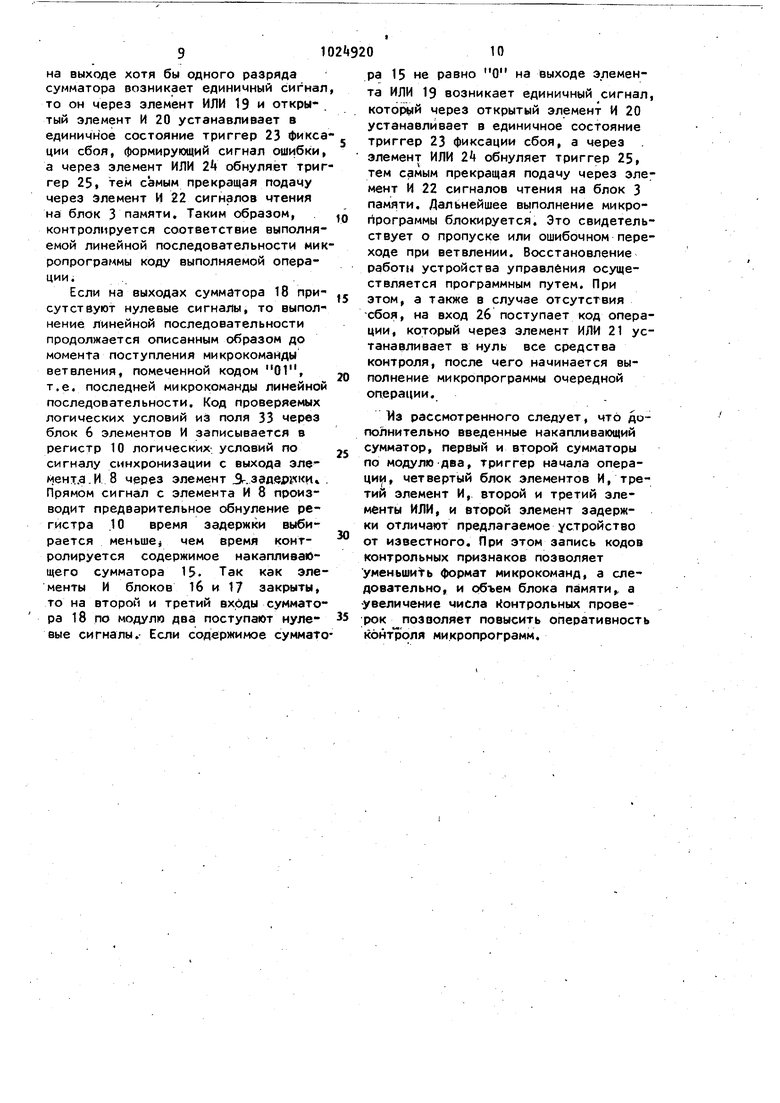

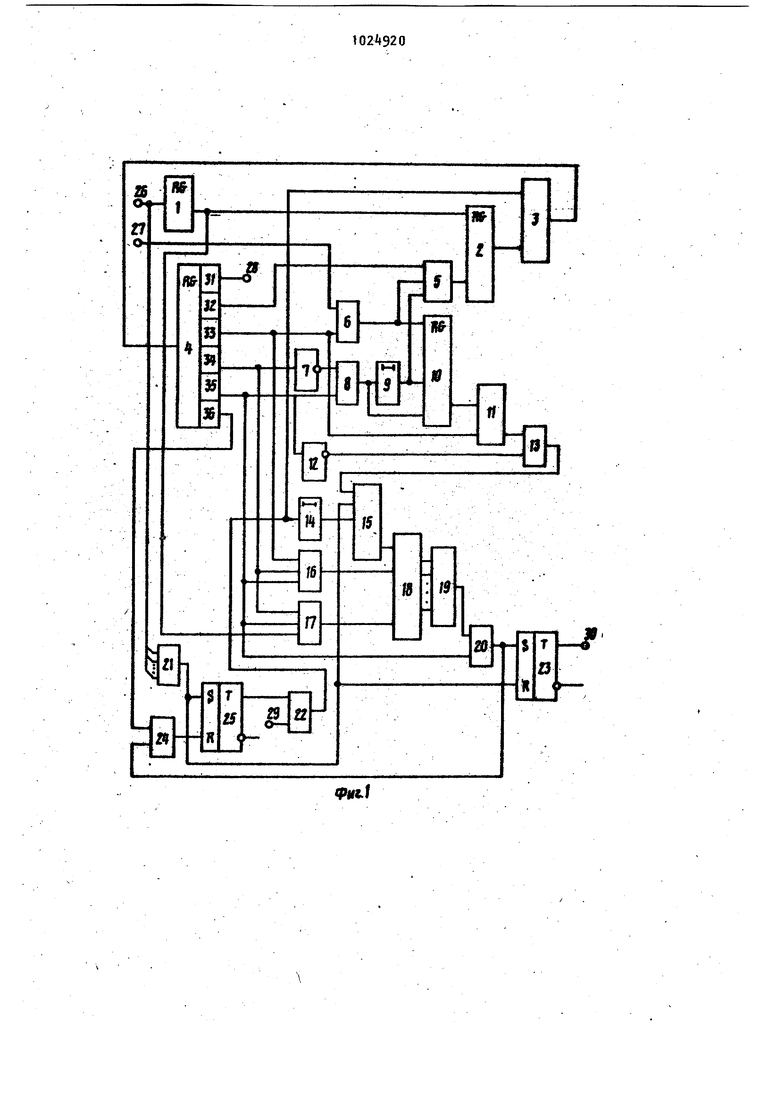

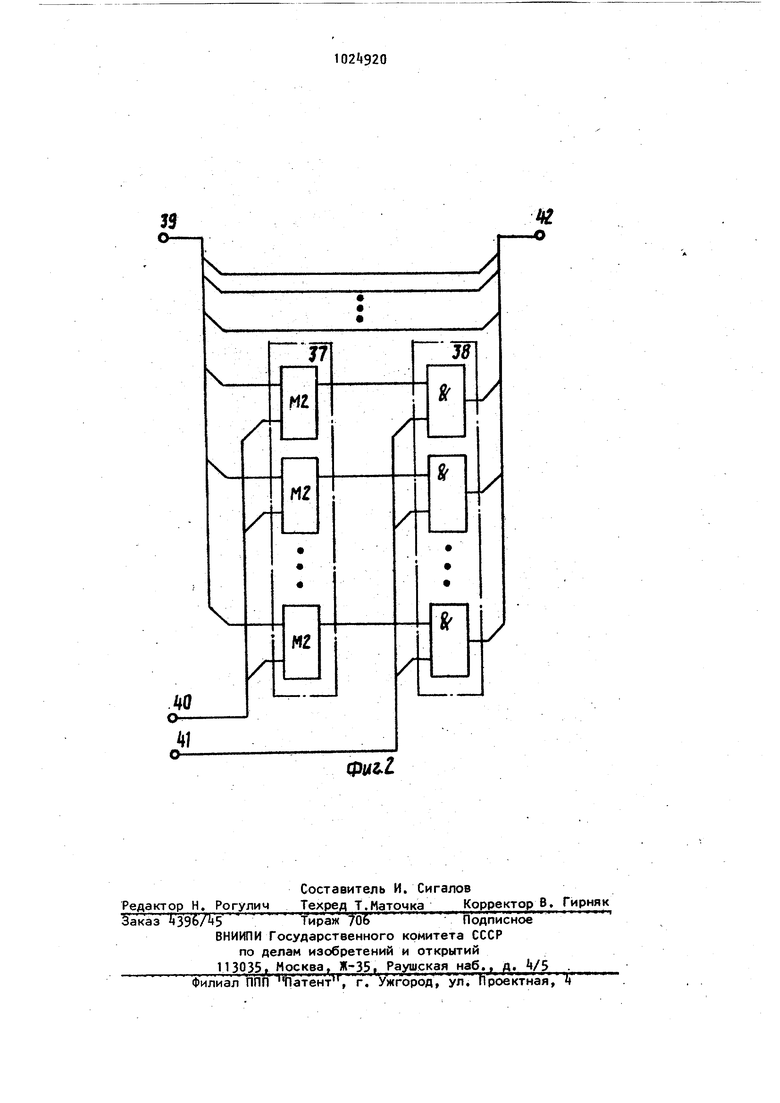

Наиболее близким по технической сущности является самоконтролируемое микропрограммное устройство управления процессора, содержащее регистр кода операции, регистр микрокоманд, регистр адреса, формирователь адреса микрокоманды, блок памяти, триггер формирования .сигнала ошибки, первый, второй и третий блоки элементов И, первый, второй элементы И элемент ИЛИ, элемент задержки, первый, второй элементы НЕ, причем выход блока памяти соединен с входом регистра микрокоманд, первый, второй и третий выходы которого соединены соответственно с выходом микроопераций устройства, первым входом первого блока элементов И и первым информационным входом формирователя адреса микрокоманд, выход которого соединен с первым информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти, первый и второй входы устройства управления соединены соответственно с входом регистра кода операции и вторьуи входом первого блока элементов И, выход которого соединен с вторым инфорнацион3ным входом формирователя адреса микрокоманды и с информационным входом регистра логических условий, управляющий вход которого соединен с выхо дом элемента задержки, выход первого элемента НЕ соединен с первым входом второго блока элементов И, вы ход первого элемента И соединен с входом триггера ошибки, единичный вы ход которого является выходом сигнала ошибки . Недостатками известного устройства являются н.зкaя экономичность, обусловленная избыточностью блока памяти, и низкая оперативность контроля соответствия выполняемой микропрограммы коду операции. В этом устройстве увеличение длины поля логических условий приводит к увеличению избыточности блока памя тИ, а осуществлениеконтроля в конце линейной последовательности определяет сравнительно низкую оперативность обнаружения несоответствия выполняемой микропрограммы коду операции. Целью изобретения является повыше ние оперативности обнаружения сбоев и сокращения объема блока памяти. Поставленная цель достигается тем что в микропрограммное устройство управления, содержащее регистр кода операции, регистр микрокоманд, регистр адреса, формирователь адреса микрокоманды, блок памяти, триггер формирователя сигнала ошибки, первый второй и третий блоки элементов И, первый, второй элементы И, элемент ИЛИ, элемент задержки, первый, второй элементы Н, причем выход блока памяти соединен с входом регистра микрокоманд, первый, второй и третий выходы которого соединены соответственно с выходом микроопераций устрой ства, первым входом первого блока элементов И и с первым информационным входом формирователя адреса микрокоманды, выход которого соединен с первым информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти, первый и второй входы устройства сое динены соответственно с входом регистра кода операции и вторым входом первого блока элементов И, выход которого соединен с вторым информацион ным входом формирователя ад0ес.а микрокоманды и с информационными входа204ми регистра логических условий, управляющий вход которого соединен с выходом элемента задержки, выход первого элемента НЕ соединен с первым входом второго блока элементов И, выход первого элемента И соединен с единичным входом триггера ошибки, единичный выkoд которого является выходом сигнала ошибки, дополнитель но введены накапливающий сумматор, первый и второй сумматоры по модули два, второй элемент задержки, триггер начала операции,четвертый блок элементов И, третий элемент И, второй и третий элементы ИЛИ, причем первый вход устройства соединен с входами второго элемента ИЛИ, выход которого соединен с единичным входом триггера начала операции, нулевым входом триггера фиксации сбоя и установочным входом накапливающего сумматора, выход которого соединен с первым входом первого сумматора по модулю два, выходы первого сумматора по модулю два соединены с входами второго элемента ИЛИ, выход которого .соединен с первым входом первого элемента И, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, выход которого соединен с нулевым входом триггера начала операции, единичный выход триггера начала операции соединен с первым входом второго элемента И, выход которого соединен с управляющим входом блока памяти и через первый элемент задержKit - с первым информационным входом накапливающего сумматора,.выход регистра кода операции соединен с вторым информационным входом регистра адреса и с первым входом четвертого лока элементов И, выход которого соединен с вторым входом первого суматора по модулю два, второй выход егистра микрокоманд соединен с первым входом второго сумматора по модую два и с первым входом третьего лока элементов И выход которого оединен с третьим входом первого умматора по модулю два, четвертый ыход регистра микрокоманд, соединен вторым входом четвертого блока элеентов И, с вторым входом третьего лока элементов, И и через второй лемент НЕ - с первым входом третьео элемента И, выход которого через торой элемент задержки соединен с правляющим входом формирователя адеса и с установочным входом регистpa логических условий, выход регистра логических условий соединен с вто рым входом второго сумматора по моду лю два, выход которого соединен с --т вторым входом второго блока элемеитов И, выход второго блока элементое И соединен с вторым информационным входом накапливающего сумматора, пятый выход регистра микрокоманд соеди нен с вторым входом первого элемента И, третьим входом четвертого блока элементов И, треты4м входом третьего блока элементов И, входом первого элемента НЕ и вторым входом третьего элемента И, шестой выход регистра микрокоманд соединен с вторым входом третьего элемента ИЛИ, третий вход устройства соединен с вторым входом второго элемента И. Сущность изобретения состоит а уменьшении длины поля логических условий микрокоманды аа счет записи контрольного признака (числа микрокоманд) в полях логических условий нескольких микрокоманд, помеченных меткой. При этом.записываемое число микрокоманд модифицируется кодом логических условий, соответствующим варианту ветвления после предыдущей линейной последовательности. . По мере выполнения линейной После довательности числа, записанные в по лях логических условий, накапливают ся в сумматоре. Причем в первом такте линейной последовательности в сум матор записывается мисло, соответствую1иее проведенному ветвлению. В каждом такте выполнения линейной последовательности в сумматор за писывается часть контрольного кодаJ а затем из сумматора производится вычитание единицы. В результате в конце линейной последовательности при при правильно проведенном ветвле нии и выполнении всех микрокоманд в сумматоре формируется нулевой код (в противном случае формируется число, не равное нулю). Кроме оставшиеся свободными поля логических условий, помеченных другой меткой, записывается конт рольный код, служащий для контроля соответствия линейной последовательности коду выполняемой операции Это позволяет повысить оперативность контроля. Реализация проверки правильности ветвления, соответствия числа микрокоманд заданному и выполнение контрольных проверок на соответствие линейной последовательности коду выполняемой операции достигается использованием указанных новых элемент тов и связей. На. фиг, 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема формирователя адреса микроко- , мёнды. Функциональная схема предлагаемого устройства содержит регистр 1 кода операций, регистр 2 адреса, блок 3 памяти и регистр микрокоманд. Формирователь 5 адреса микрокоманды, первый блок 6 элементов И, второй элемент НЕ 7, третий элемент И 8, первый элемент 9 задержки, регистр 10 логических условий, второй сумматор 11 по модулю два, первый элемент НЕ 12, второй блок 13 элементов И, второй элемент 1 задержки, накапливающий сумматор 15, третий t6 и четвертый 17 блоки элементов И, первый сумматор 18 по модулю два, второй элемент ИЛИ 19 первый элемент И 20, первый элемент ИЛИ 21, второй элемент И 22, триггер 23 фиксации сбоя, третий элемент ИЛИ 2, триггер 25-начала операции, вход 26 кода операции, вход 27 логических условий, выход 28, вход 29. сигналов чтения и выход 30 сигнала ошибки устройства, поля регистра микрокоманд Ц, поле 31 микроопераций, поле 32 адреса следукнцей микрокоманды, поле 33 задания логических условий контрольного кода и числа микрокоманд в последовательности, первый 3 и второй 35 управляющие разряды, поле 36 конца операции. Формирователь адреса микрокоманды 5 (фиг. 2) содержит группу сумматоров 37 по модулю два, осуществляющих модификацию адреса следующей микрокоманды, группу элементов И. 38, обеслечивающих запись сформированного адреса в регистр адреса 2 при ветвлении. Кроме того с;хема содержит вход 39 следующего адреса, вход 40 логических условий, вход Д1 управления, выход k2 информации в регистр 2 адреса. Предлагаемое микропрограммное устройство управления содержит средства управления и средства контроля. Средства управления включают регистр 1 кода операции, регистр 2 адреса, блок 3 памяти, регистр А микрокоманд, формирователь 5 адреса микрокоманд, первый блок 6 элементов И, второй элемент НЕ 7, третий элeмeнt И 8, первый элемент 9 задержки, первый блок элементов ИЛИ 21 третий элемент ИЛИ 2, триггер 25 начала операции, второй элемент И 22 Средства контроля включают регист 10 логических условий, сумматор 11 по модулю два, второй блок 13 элементов И, второй элемент 1 задержки, Лервый элемент НЕ 12, накапливающий сумматор 15 третий блок 16 элементов И, четвертый блок 17 элементов И, первый сумматор 18 по модулю два, второй элемент ИЛИ 19, первый элемент И 20 и триггер 23 Фик сации c6of). В исходном состоянии регистры 1 и 2, накапливающий сумматор 15 и . триггеры 23 и 25 находятся в нулевом состоянии. В исходное состояние устройство приводится перед началом работы и перед приходом каждого ново го кода операции. Связи, обеспечиваю щие установку устройства в исходное, на схеме не показаны. В блоке 3 памя ти хранятся микропрограммы операций, микрокоманды которых содержат шесть полей. Код поля 33 выполняет различные функции в зависимости от кода, хранящегося в управляющих разрядах З и 35. Комбинацией 10 в этих раз рядах отмечаются микрокоманды, в поле 33 которых записаны слагаемые чис ла микрокоманд в линейной последовательности, комбинацией 01 помечают я микрокоманды, в поле 33 которых записан код проверяемых логических условий. В поле 33 микрокоманд, поме ченных комбинацией 11, хранится контрольный код. Микропрограммное устройство управ ления работаед следующим образом. Код операции, поступающий на вход 26 через регистр 1 кода операции записывает в регистр 2 адреса, Одновременно код операции через элемент ИЛИ 21 приводит триггер 25 в единичное состояние, который своим единичным выходом разрешает прохождение сигналов чтения с входа 29 через элемент И 23 в блок 3 памяти . А по записанному в регистре 2 адресу 110 сигналу считывания блока 3 -Памяти первая микрокоманда 208 микропрограммы поступает в регистр k микрокоманд k. Код поля 3 определяющий содержание микроопераций, поступает на выход 28 устройства управления. Код поля следующего адреса 32 поступает в формирователь 5. В конце каждой линейной последовательности подается микрокоманда ветвления с кодом 01 в разрядах 3 и 35. Значения логических условий поступает на вход формирователя адерса микрокоманд и модифицирует код следующего адреса. Нулевой сигнал с выхода поля 3 через элемент НЕ 7 и единичный сигнал с выхода поля 35 поступают на элемент И 7, на выходе которого формируется единичный сигнал управления. Сформированный сигнал через элемент 9 задержки, обеспечивающий предварительное обнуление регистра логических условий, поступает на управляющий вход фррмирователя 5 адреса микрокоманды и разрешает запись модифицированного кода в регистр 2 адреса. После окончания выполнения микропрограммы данной операции в поле 36 появляется единичный сигнал, который через элемент ИЛИ 2k обнуляет триггер 25 начала операции. В результате сигналы чтения прекращают поступать через элемент И 22 в блок 3 памяти. Одновременно происходит установка всего устройства в исходное состояние. Далее повторяются описанные действия, начиная с подачи очередного кода операции на вход 26 устройства. Работа средств контроля. В начале каждой линейной последовательности располагается последовательность микрокоманд, помеченных в полях З и 35 кодом 10. Коды поля 33 в этих микрокоманд, численно равные длине линейной последовательности, модифи цируются кодом логических условий из регистра 10 и накапливаются в сумматоре 15. Одновременно в каждом такте через элемент k задержки производится вычитание единицы 1 из содержимого сумматора 15 т.е. к концу линейной последовательности содержимое сумматора должно равняться нулю, ; При поступлении микрокоманды, помеченной кодом 11, открываются блоки элементов И .16 и 17. При этом код операции, код из поля 33 и содержимое накапливающего сумматора 15 поразрядно qyммиpyютcя по модулю два. Если 1 на выходе хотя бы одного разряда сумматора возникает единичный сигнал то он через элемент ИЛИ 19 и открытый элемент И 20 устанавливает в единичное состояние триггер 23 фикса ции сбоя, формирующий сигнал ошибки, а через элемент ИЛИ 2k обнуляет триг гер 2S, тем самым прекращая подачу через элемент И 22 сигналов чтения на блок 3 памяти. Таким образом, контролируется соответствие выполняемой линейной последовательности мик ропрограммы коду выполняемой операции. Если на выходах сумматора 18 присутствуют нулевые сигналы, то выполнение линейной последовательности продолжается описанным образом до момента поступления микрокоманды ветвления, помеченной кодом 01, т.е. последней микрокоманды линейной последовательности. Код проверяемых логических условий из поля 33 через блок 6 элементов И записывается в регистр 10 логических условий по сигналу синхронизации с выхода элемент.а.И 8 через элемент 3-.зэдйр1 1 и Прямом сигнал с элемента И 8 производит предварительное обнуление регистра ,10 время задержки выбирается MeHbmej чем время контролируется содержимое накапливайщего сумматора 15. Так как эле менты И блоков 1б и 17 закрыты, то на второй и третий входы сумматора 18 по модулю два поступают нулевые сигналы.- Если содержимое суммато 010 ра 15 не равно О на выходе элемента ИЛИ 19 возникает единичный сигнал, которой через открытый элемент И 20 устанавливает в единичное состояние триггер 23 фиксации сбоя, а через . элемент ИЛИ 2 обнуляет триггер 25, тем самым прекращая подачу через элемент И 22 сигналов чтения на блок 3 памяти. Дальнейшее вь1полнение микропрограммы блокируется. Это свидетельствует о пропуске или ошибочном переходе при ветвлении. Восстановление работы устройства управления осуществляется программным путем. При этом, а также в случае отсутствия сбоя, на вход 26 поступает код операции, который через элемент ИЛИ 21 устанавливает в нуль все средства контроля, после чего начинается выполнение микропрограммы очередной операции. Из рассмотренного следует, что дополнительно введенные накапливающий сумматор, первый и второй сумматоры по модулю два, триггер начала операции, четвертый блок элементов И, третий элемент И, второй и третий элементы ИЛИ, и второй элемент задержки отличают предлагаемое устройство от известного. При этом запись кодов контрольных признаков позволяет уменьшить формат микрокоманд, а следовательно, и объем блока памяти,, а -увеличение числа Контрольных прове;рок позволяет повысить оперативность контролй микропрограмм.

J3

, V

1

.

мг

ч

«2

м

151

W

(Риг.

Авторы

Даты

1983-06-23—Публикация

1982-02-09—Подача