(54) ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1061275A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1988 |

|

SU1518905A2 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| Устройство для контроля памяти | 1983 |

|

SU1167660A1 |

| Устройство для исправления двойных и обнаружения многократных ошибок циклическими кодами | 1983 |

|

SU1185611A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

1Изобретение относится к технике передачи дискретных сообщений и может быть использовано при построении системы передачи информации с решающей обратной связью. Известно декодирующее . устройство, содержащее первый элемент ИЛИ, к одному из входов которого подключен выход сумматора по модулю два, ко входам которого подключены соответственно выход накопителя и выход второго элемента ИЛИ, к одному из входов которого подключен один из выходов блока обнаружения ощибок через счетчик тактовых импульсов, причем другой вход первого .элемента ИЛИ является входом устройства 1. Однако достоверность декодирования в этом устройстве невысока. Цель изобретения - повышение достоверности декодирования. Эта цель достигается тем, что в декодирующее устройство, содержащее первый элемент ИЛИ, к одному из входов которого подключен выход сумматора по модулю два, ко входам которого подключены соответственно выход накопителя и выход второго элемента ИЛИ, к одному из входов которого подключен один из выходов блока обнаружения ощибок через счетчик тактовых импульсов, причем другой вход первого элемента ИЛИ является входом устройства, введены последовательно соединенные счетчик циклов, первый элемент И-ИЛИ, к другому входу которого подключен первый выход регистра сдвига через элемент И-НЕ, и триггер, прямой и инверсный выходы которого подключены- соответственно к первому входу и ко второму входу второго элемента И-ИЛИ, при этом первый дополнительный выход блока обнаружения ощибок подключен к первому входу счетчика циклов, второй вход которого объединен со входом регистра сдвига и с соответствующим входом первого элемента И-ИЛИ и подключен ко второму дополнительному выходу блока обнаружения ошибок, второй выход регистра сдвига подключен к соответствующему входу второго элемента ИЛИ, третий вход второго элемента И-ИЛИ подключен к выходу накопителя, четвертый вход - к выходу первого элемента ИЛИ и ко входу блока обнаружения ощибок, второй вход объединен с соответствующим входом первого элемента И-ИЛИ, а выход второго элемента И-ИЛИ подключен . ко входу накопителя.

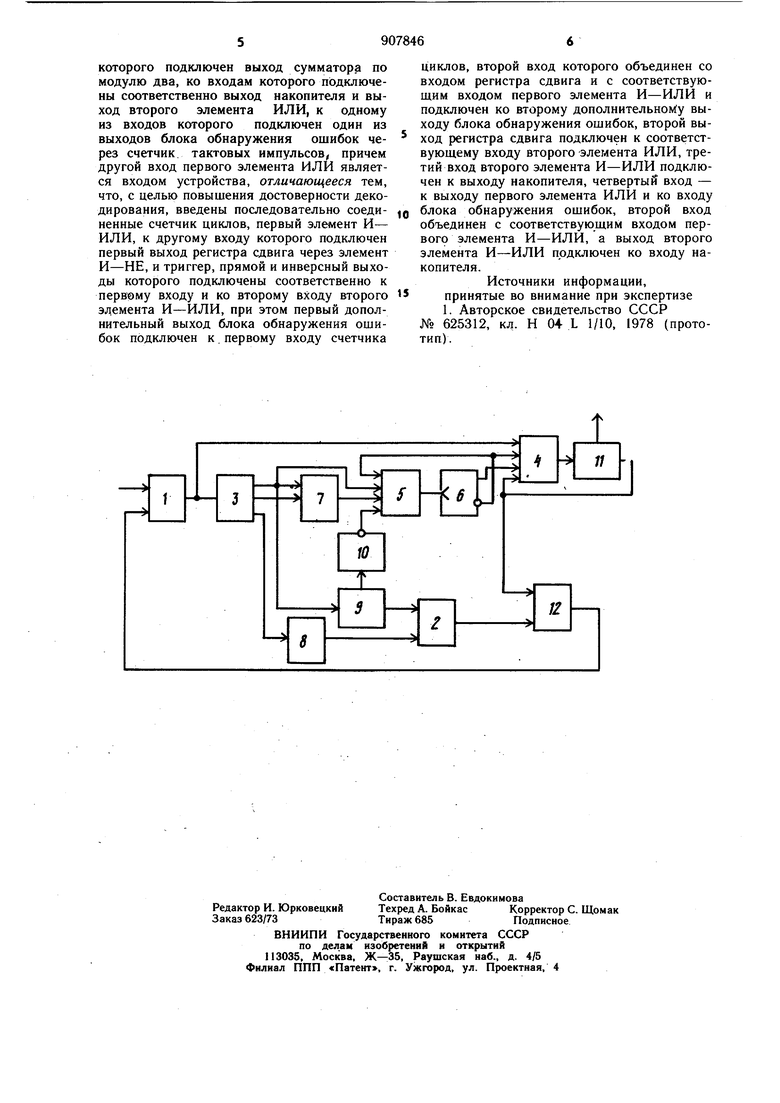

На чертеже представлена структурная электрическая схема декодирующего устройства.

Декодирующее устройство содержит элементы ИЛИ 1 и 2, блок 3 обнаружения ощибок, элементы И-ИЛИ 4 и 5, триггер 6, счетчик 7 циклов, счетчик 8 тактовых импульсов, регистр 9 сдвига, элемент И-НЕ 10, накопитель 11 и сумматор 12 по модулю.два.

Устройство работает следующим образом.

В исходном состоянии сигналы на выходе счетчика 7 циклов отсутствуют, а триггер б установлен в состояние, при котором элемент И-ИЛИ 4 открыт по первому входу, второй вход которого заблокирован потенциалом с прямого выхода триггера 6.

При приеме комбинации запускается счетчик 8 тактовых импульсов, не прекращающий работу до перехода устройства в режим приема очередной комбинации, а принимаемая комбинация через элемент ИЛИ 1 записывается в блок 3 обнаружения ощибок, вход которого через элемент И-ИЛИ 4 соединен с иакопителем 11.

При необнаружении ощибок в комбинации блок 3 обнаружения ошибок разрешает выдачу информационных элементов комбинации из накопителя 11 получателю, а устройство переходит в режим приема очередной комбинации.

При обнаружении ошибок-устройство переходит в режим исправления ошибок. При этом первый импульс обнаружения ошибок поступает в счетчик 7 циклов, а через элемент И-ИЛИ 5 поступает на счетный вход триггера 6, изменяя состояние последнего на противоположное. С изменением состояния триггера б потенциал прямого выхода последнего деблокирует второй вход элемента И-ИЛИ 4, а потенциал инверсного выхода триггера б блокирует первый вход последнего и первый вход элемента И-ИЛИ 5.

В первых п циклах режима исправления ошибок исходная комбинация через сумматор 12 по модулю два и элемент ИЛИ 1 записывается в блок 3 обнаружения, а через элемент И-ИЛИ 4 и в накопитель И. По окончании каждого из циклов блок 3 обнаружения ощибок формирует импульсы необнаружения или иЛпульсы обнаружения ошибок. Поступающие в счетчик 7 циклов, и в регистр 9,сдвига.

В каждом из п циклов на исходную комбинацию в сумматоре 12 по модулю два накладывается вектор одиночной ошибки. В первом цикле режима исправления ошибок счетчик 8 тактовых импульсов с емкостью (n-f-1) выдает импульс переполнения, появляющийся через элемент ИЛИ 2 на втором входе сумматора 12 по модулю два в момент поступления на первом входе последнего первого разряда исходной комбинации, обеспечивающий инвертирование этого разряда. Таким образом, в блок 3 обнаружения ошибок записывается исходная комбинация с

наложенным на нее вектором одиночной ошибки. Во втором цикле вектор одиночной ошибки накладывается на второй разряд исходной комбинации и. т.д.

С завершением п-го цикла режима исправления ощибок в регистре 9 сдвига зарегистрирована п-разрядная комбинация, содержащая единицы в разрядах, номера которых совпадают с номером цикла, заверщивщегося обнаружением ощибки.

По окончании п-го цикла режима исправления ощибок счетчик 7 циклов с емкостью (п+1) выдает импульс переполнения через элемент И-ИЛИ 5 на счетный вход триггера б лищь при наличии на выходе элемента И-НЕ 10 разрещающего потенциала, появляющегося по окончании п-го цикла лищь при регистрации в регистре 9 сдвига меньще чем п импульсов обнаружения ощибки, при этом импульс переполнения счетчика 7 циклов установит триггер б в исходное состояние и потенциал прямого выхода триггера б

S блокирует первый вход элемента И-ИЛЙ4, первый вход которого деблокируется потенциалом инверсного выхода триггера б.

При реализации (пЧ-1) цикла режима исправления ощибок на исходную комбинацию в сумматоре 12 по модулю два налагается п-разрядный вектор ощибок, поразрядно подаваемый на второй вход сумматора 12 по модулю два через элемент ИЛИ 2 с выхода регистра 9 сдвига.

При этом в накопителе 11 запищется комбинация с исправленными ощибками и блок 3 обнаружения ошибок разрешает выдачу информационных элементов комбинации из накопителя 1 получателю, а устройство переходит в режим приема очередной комбинации.

Если по окончании п циклов режима исправления ошибок отождествление комбинации не произойдет, то исходная комбинация стирается, а устройство переходит в режим

S приема очередной комбинации.

Введение регистра сдвига, счетчика циклов, триггера элементов И и И-ИЛИ с соответствующими связями позволяет исправлять как однократные, так и многократные ощибки, что снижает число переспросов информации в системах с решающей обратной связью, снижает потери информации в системах со стиранием и обеспечивает повыщение достоверности принимаемой информации.

Формула изобретения

Декодирующее устройство, содержащее первый элемент ИЛИ, к одному из входов

которого подключен выход сумматора по модулю два, ко входам которого подключены соответственно выход накопителя н выход второго элемента ИЛИ, к одному нз входов которого подключен однн нз выходов блока обнаружения ошибок через счетчик тактовых импульсов причем другой вход первого элемента ИЛИ является входом устройства, отличающееся тем, что, с целью повышения достоверности декодирования, введены последовательно соединенные счетчик циклов, первый элемент И-ИЛИ, к другому входу которого подключен первый выход регистра сдвига через элемент И-НЕ, и триггер, прямой и инверсный выходы которого подключены соответственно к первому входу и ко второму входу второго элемента И-ИЛИ, при этом первый дополнительный выход блока обнаружения ошибок подключен к . первому входу счетчика

циклов, второй вход которого объединен со входом регистра сдвига и с соответствующим входом первого элемента И-ИЛИ и подключен ко второму дополнительнол у выходу блока обнаружения ошибок, второй выход регистра сдвига подключен к соответствующему входу второго элемента ИЛИ, третий вход второго элемента И-ИЛИ подключен к выходу накопителя, четвертый вход - к выходу первого элемента ИЛИ и ко входу блока обнаружения ошибок, второй вход объединен с соответствующим входом первого элемента И-ИЛИ, а выход второго элемента И-ИЛИ подключен ко входу накопителя.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 625312, кл. Н 04 L 1/10, 1978 (прототип).

Авторы

Даты

1982-02-23—Публикация

1980-04-24—Подача