(54) ОДНОРАЗРЯДНЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| Устройство для суммирования | 1978 |

|

SU822183A2 |

| Устройство для суммирования | 1979 |

|

SU868750A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Матричное устройство для извлечения квадратного корня | 1985 |

|

SU1260951A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1104511A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для извлечения квадратного корня | 1976 |

|

SU661550A1 |

| Цифроаналоговый преобразователь с многофазным выходом | 1987 |

|

SU1476611A1 |

| Последовательный сумматор | 1977 |

|

SU696452A1 |

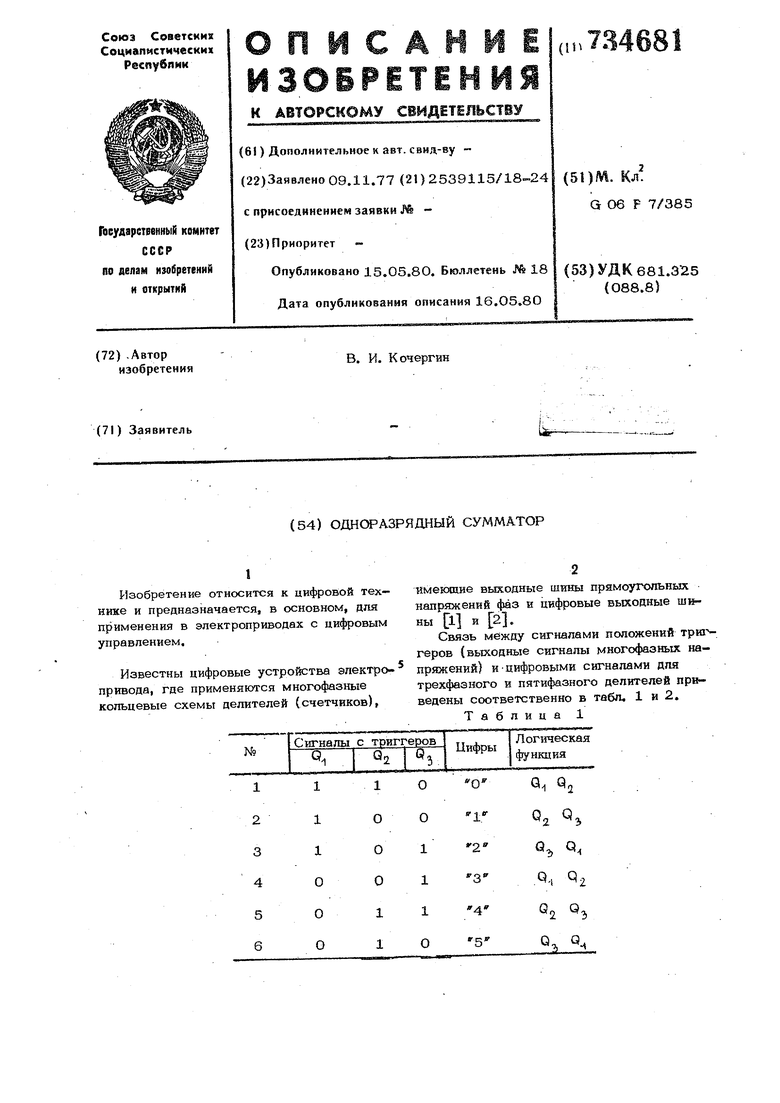

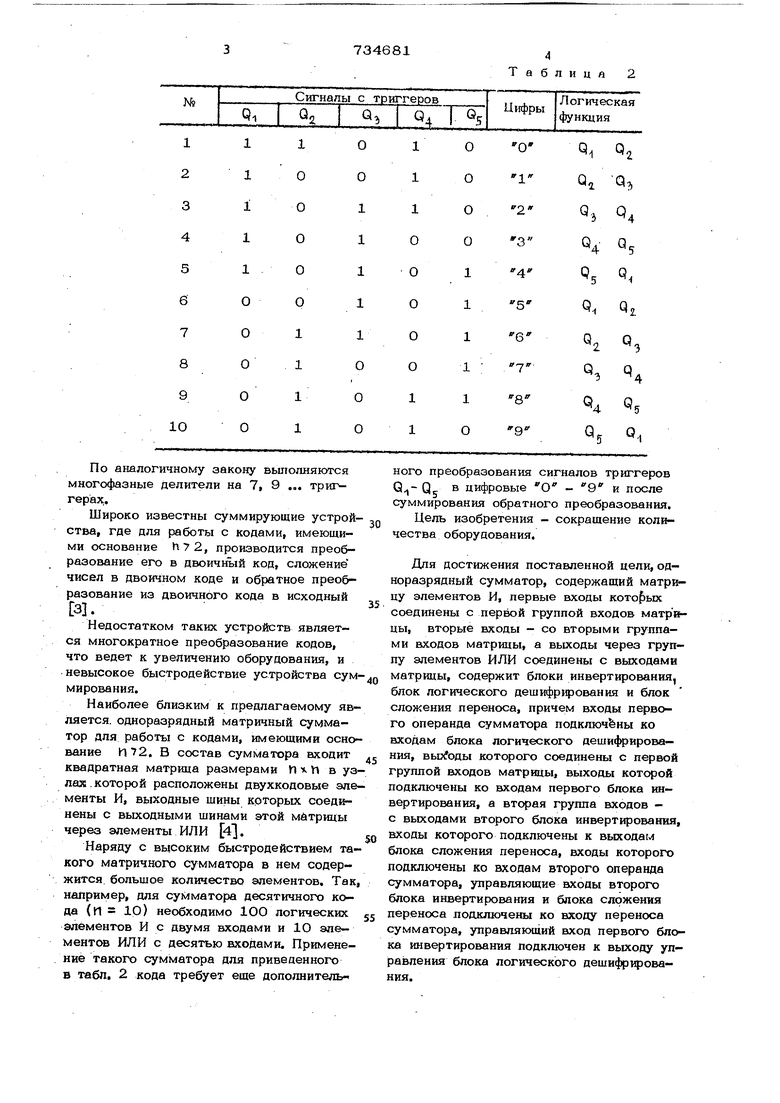

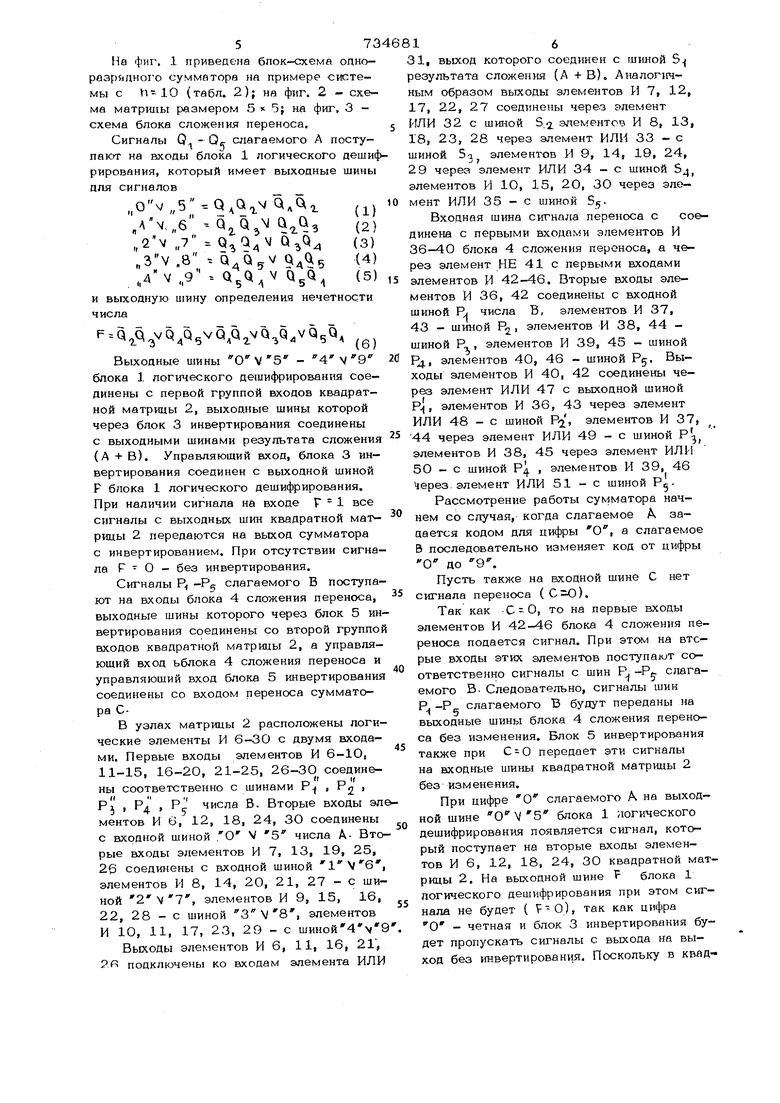

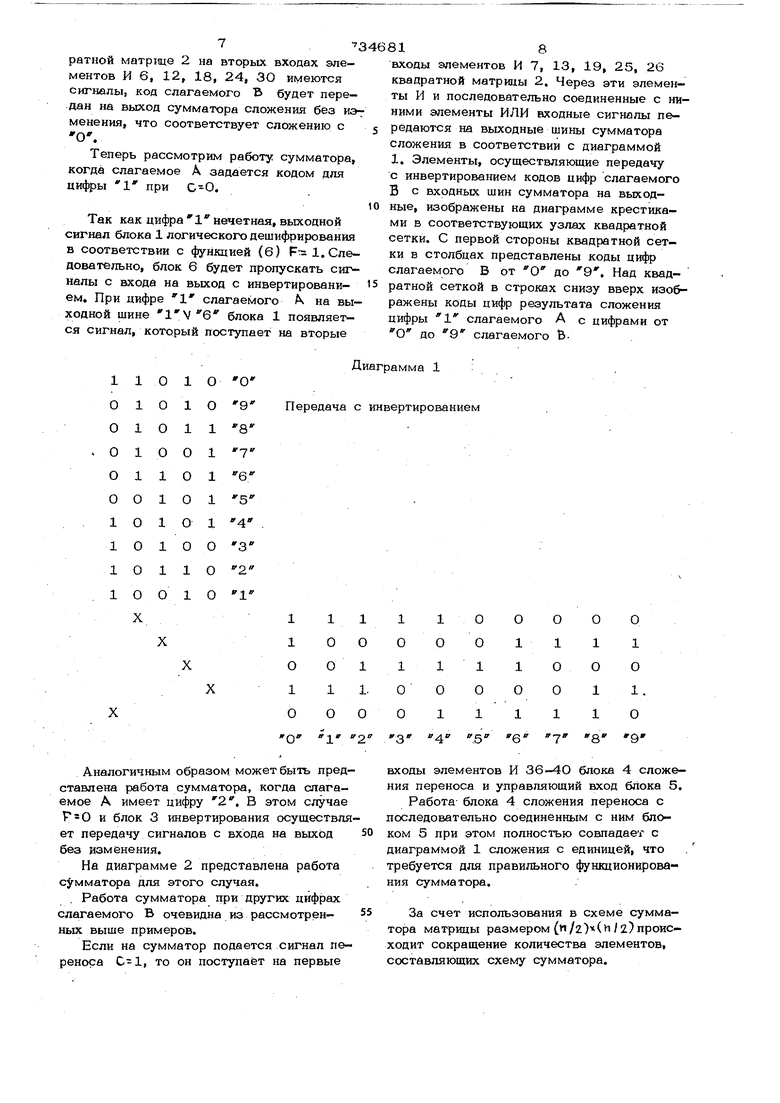

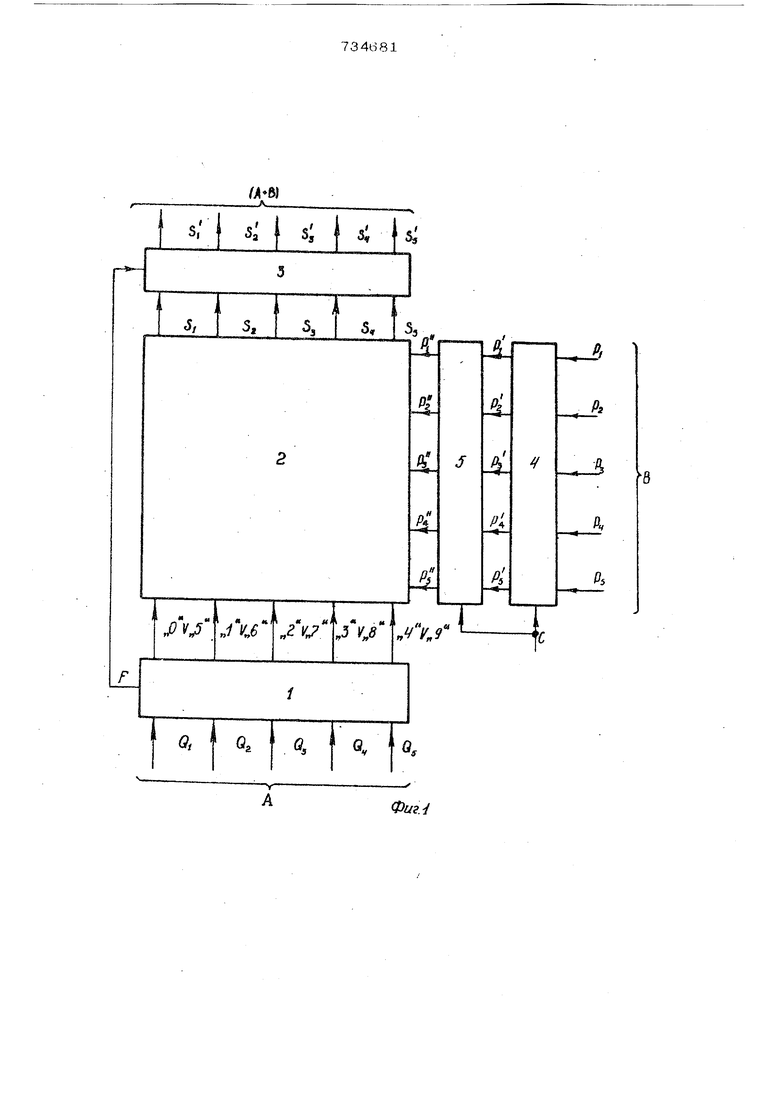

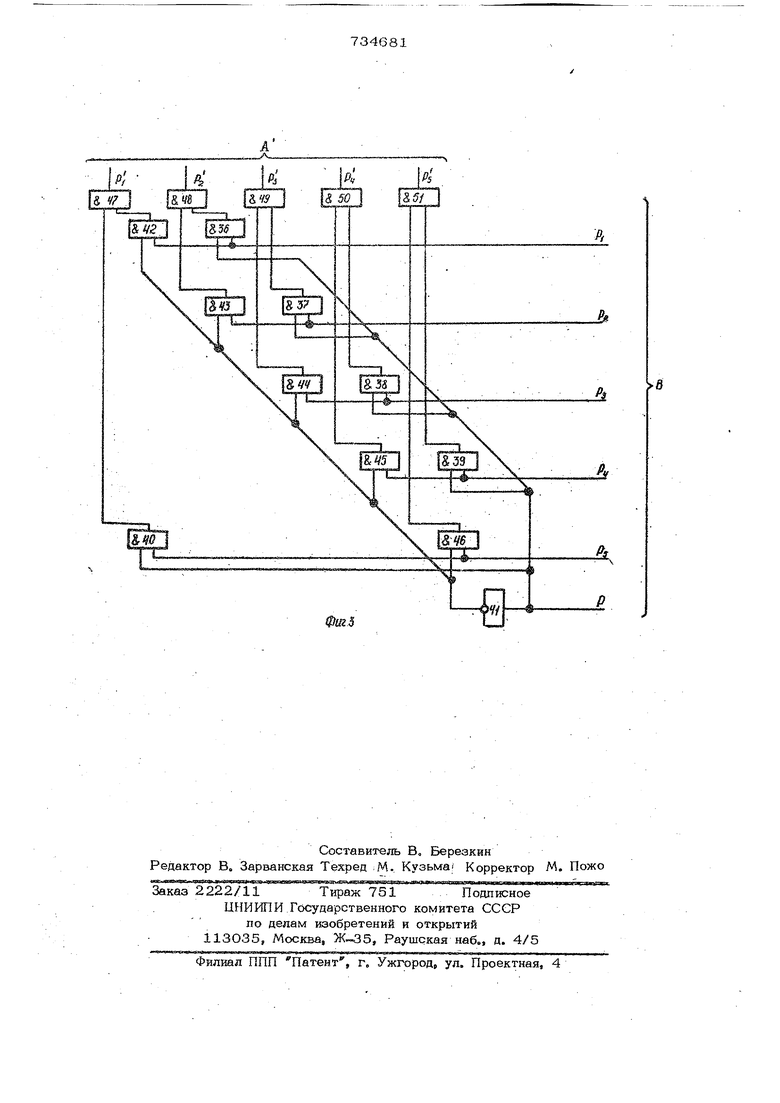

1 Р аобретение относится к цифровой техниже и предназначается, в основном, для применения в электроприводах с цифровым управлением. Известны цифровые устройства электропривода, где применяются многофа31а1е кольцевые схемы делителей (счетчиков), 2 имеющие выходные mmai прямоутч пьных напряженки фаз и цифровые вькоцные шины l и 2. Связь между сигналами положений трш геров (выходные сигналы многофазных напряжений) и-Ц11фровыми сигналами для трехфазного и пятифазного делителей приведены соответственно в табл, 1 и 2. Таблица 1 По аналогичному закону выполняются многофазные делители на 7, 9 .„. трипrepiax. Широко известны суммирующие устройства, где для работы с кодами, имеющими основание П72, производится преобразование его в двоичьШ1й код, сложение чисел в двоичном коде и обратное преоб разование из двоичного кода в исходный Недостатком таких устройств является многократное преобразование кодов, что ведет к увеличению оборудования, и невысокое быстродействие устройства сум мирования. Наиболее близким к предлагаемому является, одноразрядный матричный сумматор для работы с кодами, имеющими осно вание И 72. В состав сумматора входит квадратная матрица размерами h i Ц в уз лах, которой расположены двухкодовые эле менты И, выходные шины крторых соединены с выходными шинами этой мйтрицы через элементы ИЛИ 4. Наряду с высоким быстродействием та кого матричного сумматора в нем содержится большое количество элементов. Так например, для сумматора десятичного кода (п - 1р) необходимо 1ОО логических элементов И с двумя входами и 10 элементов ИЛИ с десятью входами. Применение такого сумматора для приведенного в табл. 2 кода требует еще дополи и тель-Таблица 2 ного преобразования сигналов триггеров Q-i Qc цифровые О - 9 и после суммирования обратного преобразования. Цель изобретения - сокращение количества оборудования. Для достижения поставленной цели, одноразрядный сумматор, содержащий матрицу элементов И, первые входы соединены с первой группой входов матрицы, вторые входы - со вторыми группами входов матрицы, а выходы через группу элементов ИЛИ соединены с выходами матрицы, содержит блоки инвертирования, блок логического дешифрирования и блок сложения переноса, причем входы первого операнда сумматора подключены ко входам блока логического дешифрирования, вьиЛ)ды которого соединены с первой группой входов матрицы, выходы которой подключены ко входам первого блока инвертирования, а вторая группа входов с выходами второго блока инвертирования, входы которого подключены к выходам блока сложения переноса, входы которого подключены ко входам второго операнда сумматора, управляющие входы второго блока инвертирования и блока сложения переноса подключены ко входу переноса сумматора, управляющий вход первого блока инвертирования подключен к выходу управления блока логического дешифрирования. На фиг. 1 приведена блок-схема одноразрядного сумматора на примере системы с И-10 (табл. 2); на фиг. 2 - схема матр1щы размером 5 5} на фиг, 3 схема блока сложения переноса. Сигналь Q - Q слагаемого А поступакп на входы блока 1 логического дешиф рирования, который имеет выходные шины для сигналов ..,,5;;.Q, -а.а. ,.2V „7 Q. ,34.8 -Q,Q,v ,.4 V „9 . 1|Ч И выходную ишну определения нечетности числа .vQ,,,VQ5Q, Выходные шины О V 5 - 4 V 9 блока 1 логического дешифрирования соединены с первой группой входов квадратной матр1щы 2, выходные шины которой через блок 3 инвертирования соединены с выходными шинами результата сложения (А + В). Управляющий вход, блока 3 инвертирования соединен с выходной шиной F блока 1 логического дешифрирования. При наличии сигнала н& входе Г 1 все сигналы с выходных шин квадратной ма1 рицы 2 передаются на выход сумматора с инвертированием. При отсутствии сигна ла F - О - без инвертирования. Сигналы Р -Pg слагаемого Б поступают на входы блока 4 сложения переноса, выходные шины которого через блок 5 ин вертирования соединены со второй группо входов квадратной матрицы 2, а управляющий вход ьблока 4 сложения переноса и управляюший вход блока 5 инвертирования соединены со входом переноса сумматора СВ узлах матр1щы 2 расположены логические элементы И 6-ЗО с двумя входами. Первые входы элементов И 6-10, 11-15, 16-20, 21-25, 26-ЗО соединесоответственно с шинами РН IIt Р , числа В. Вторые входы эл } , Г4 ментов И 6, 12, 18, 24, ЗО соединены с входной шиной .О V 5 числа А- Вто рые входы элементов И 7, 13, 19, 25, 26 соединены с ЕУСОДНОЙ шиной 1 V6 элементов И 8, 14, 20, 21, 27 - с шиной 2МТ, элементов И 9, 15, 16, 22, 28 - с шиной 3V8, элементов И 10, 11, 17, 23, 29 - с шиной4 9 Выходы элементов И 6, 11, 16, 21, R подключены ко входам элемента ИЛИ 31, ВЫХОД которого соединен с ш}шой 5 результата сложения (А +В). Аналогичным образом выходы элементов И 7, 12, 17,22, 27 соединены через элемент ИЛИ 32 с шиной 3,2. элементов И 8, 13, 18,23, 28 через элемент ИЛИ 33 - с шиной элементов И 9, 14, 19, 24, 29 через элемент ИЛИ 34 - с шиной SA элементов И 1О, 15, 20, 30 через элемент ИЛИ 35 - с шиной 85Входная шина сигнала переноса с соединена с первыми входами элементов И 36-40 блока 4 сложения переноса, а через элемент НЕ 41с первыми входами элементов И 42-46. Вторые входы элементов И 36, 42 соединены с входной шиной PJ числа Б, элементов И 37, шиной Р, элементов И 38, 44 , элементов И 39, 45 - шиной Р, элементов 40, 46 - шиной Р. Выходы элементов И 40, 42 соединены через элемент ИЛИ 47 с выходной шиной Р, элементов И 36, 43 через элемент ИЛИ 48 - с шиной Р-2, элементов И 37, 44 через элемент ИЛИ 49 - с шиной Р элементов И 38, 45 через элемент ИЛИ 50 - с шиной PJJ. , элементов И 39, 46 iiepe3. элемент ИЛИ 51 - с шиной РсРассмотрение работы сумматора начнем со случая, когда слагаемое Д задается кодом для цифры О, а слагаемое Б последовательно изменяет код от цифры О до 9. Пусть также на входной шине С нет сигнала переноса ( ). Так как -0 0, то на первые входы элементов И 42-46 блока 4 сложения переноса подается сигнал. При этом на вторые входы этих элементов поступают соответственно сигналы с шин Р. -Р. слагаемого В. Следовательно, сигналы шин Р, -Р слагаемого Б будут переданы на выходные шины блока 4 сложения переноса без изменения. Блок 5 инвертирования также при С 0 передает эти сигналы на входные шины квадратной матрицы 2 без изменения. При цифре О слагаемого Л на выходной шине 0V5 блока 1 логического дешифрирования появляется сигнал, который поступает на вторые входы элементов И 6, 12, 18, 24, 30 квадратной матрицы 2. На выходной шине Р блока 1 логического дешифрирования при этом cvnrнала не будет ( f-O), так как цифра О - четная и блок 3 инвертирования будет пропускать сигналы с выхода на выход без инвертированш. Поскольку в квад73ратной матрще 2 на вторых входах элементов И 6, 12, 18, 24, ЗО имеются сигналы, код слагаемого В будет передан на выход сумматора сложения без иэменения, что соответствует сложению с О. Теперь рассмотрим работу сумматора, когда слагаемое Л задается кодом для цифры при . Так как цифра нечетная, выходной сигнал блока 1 логического дешифрирования в соответствии с функцией (6) .Следовательно, блок 6 будет пропускать сигналы с входа на выход с инвертированием. При цифре слагаемого на вы- ходной шине 1 V6 блока 1 появляется сигнал, который поступает на вторые

Передача с инвертированием

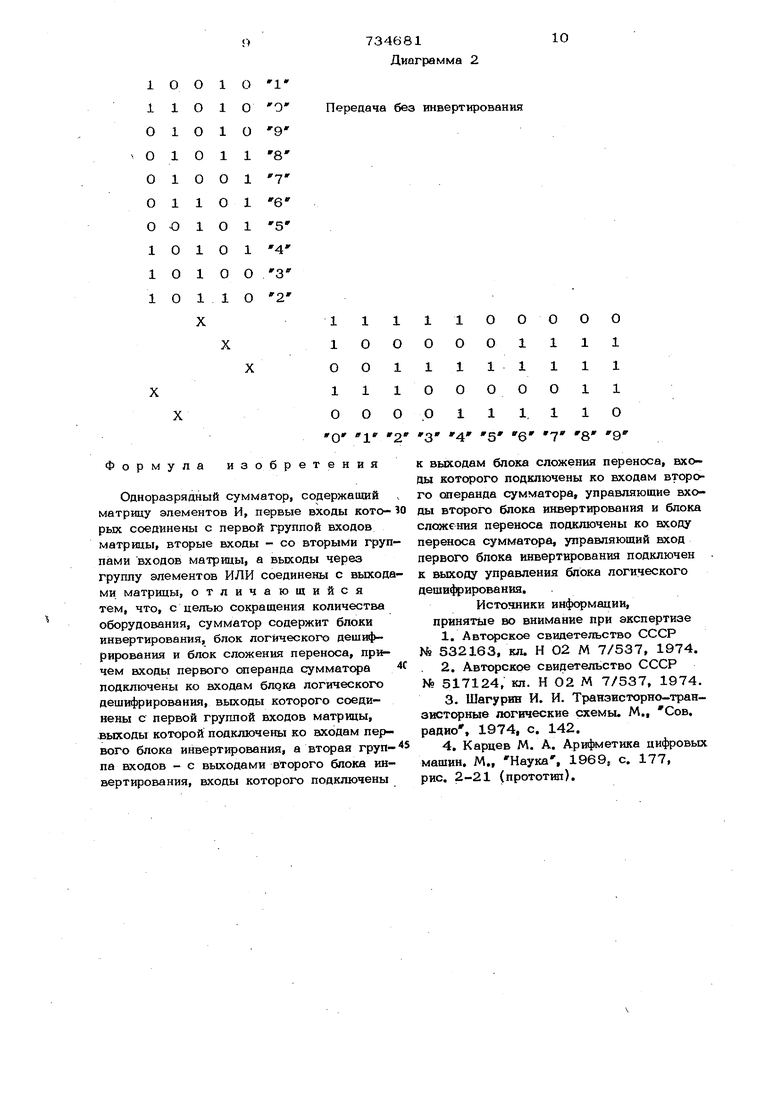

О Аналогичным образом может быть представлена работа сумматора, когда слагаемое А имеет цифру 2, В этом случае Г 0 и блок 3 инвертирования осуществля ет передачу сигналов с входа на выход без изменения. На диаграмме 2 представлена работа с гмматора для этого случая. Работа сумматора при других циф|эах слагаемого В очевидна из рассмотренных выше примеров. Если на сумматор подается сигнал переноса , то он поступает на первые Д

8

vcir ПК.

4

3 818 входы элементов И 7, 13, 19, 25, 26 квадратной матрицы 2, Через эти элементы И и последовательно соединенные с ни- ними элементы ИЛИ входные сигналы передаются на выходные шины сумматора сложения в соответствии с диаграммой 1. Элементы, осуществляющие передачу с инвертированием кодов цифр слагаемого В с входных шин сумматора на выходные, изображены на диаграмме крестиками в соответствующих узлах квадратной сетки. С первой стороны квадратной сетки в столбцах представлены коды цифр слагаемого Б от О до 9. Над квадратной сеткой в строках снизу вверх изо&ражены коды цифр результата сложения цифры I слагаемого А с цифрами от О до 9 слагаемого Вамма 1 : входы элементов И 36-40 блока 4 сложения переноса и управляющий вход блока 5. Работа блока 4 сложения переноса с последовательно соединенным с ним блоком 5 при этом полностью совпадает с диаграммой 1 сложения с единицей, что требуется для правильного функционирования сумматора. За счет использования в схеме сумматора матрицы размером («/2)(п/2) происходит сокращение количества элементов, составляющих схему сумматора.

О 1 23 4 5 6 7 8 9

Формула изобретенияк выходам блока сложения переноса, вхоОдноразрядный сумматор, содержаишй .го операнда сумматора, управляющие вхоматрицу элементов И, первые входы кото- 30дь1 второго блока инвертирования и блока

рых соединены с первой группой входовсложения переноса подключены ко входу

матрицы, вторые входы - со вторыми груп переноса сумматора, управляющий вход

пами входов матрицы, а выходы черезпервого блока инвертирования подключен

группу элементов ИЛИ соединены с выхода-к выходу управления блока логического

ми матрицы, отличающийсядешифрирования,

тем, что, с целью сокращения количестваИсточники информации,

оборудования, сумматор содержит блокипринятые во внимание при экспертизе

инвертирования, блок логического дешиф-1. Авторское свидетельство СССР

рирования и блок сложения переноса, при-Nfe 532163, кл. Н О2 М 7/537, 1974.

чем входы первого операнда сумматора 4С2. Авторское свидетельство СССР

подключены ко входам блдка логического№ 517124, кл. Н 02 М 7/537, 1974.

дешифрирования, выходы которого соеди-3. Шагурин И. И. Транзисторно-траннены с первой группой входов матрицы,эисторные логические схемы. М., Сов.

.выходы которой подключены ко входам пер-радио, 1974, с. 142.

вого блока инвертирования, а вторая rpyn- S4. Карцев М. А. Арифметика цифровых

па входов - с выходами второго блока ий-машин. М., Наука, 19695 с. 177,

вертирования, входы которого подключенырис. 2-21 (прототип). ды которого подключены ко входам второ v

A

Фиг.

CM

д

Авторы

Даты

1980-05-15—Публикация

1977-11-09—Подача