. ;1 . ;

Изобретение относится к вычисяительной технике и предназначается в основном в электроприводах с цифровым управлением.

Известны цифровые устройства электропривода, где применяются многофазные схемы делителей (счетчиков), имеющие . выходные шины прямоугольных напряжений фаз и цифровые В1ыходные шины. Принципы построения принципиальных схем таких делителей на четном и нечетком числе, например RS .триггеров различны И и 2.

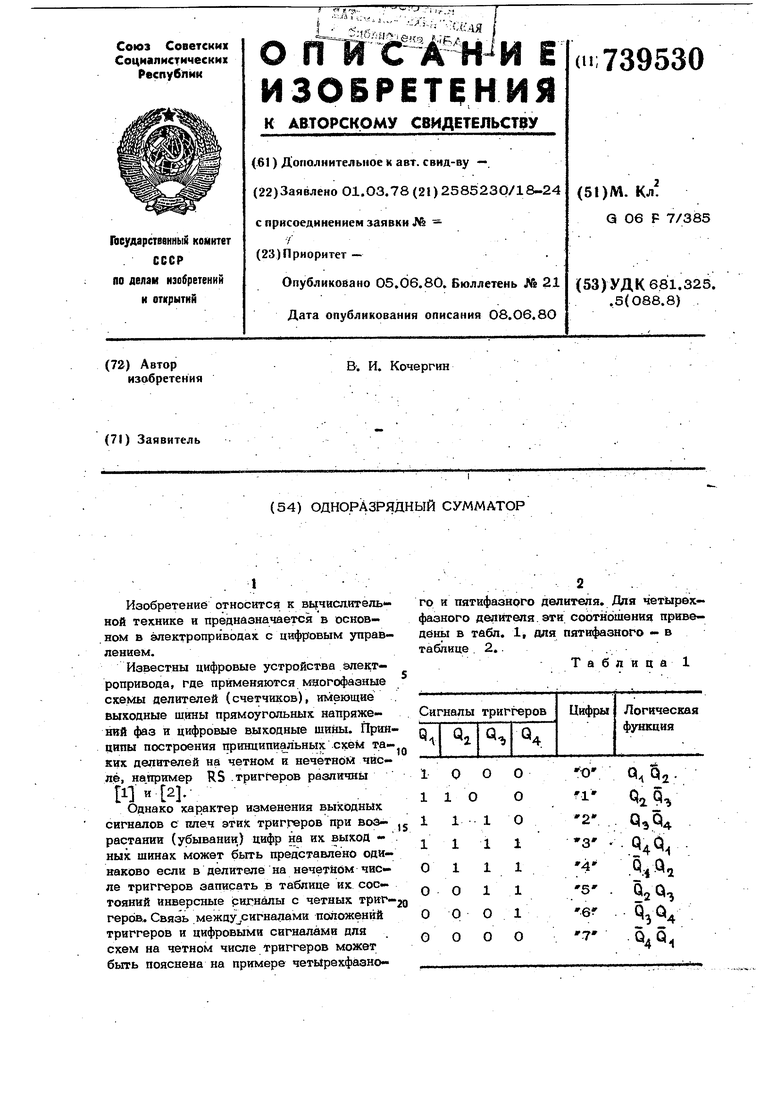

Однако характер изменения выходных сигналов с плеч этих триггеров при воз- j, растании (убывании) цифр на их выход ных шинах может быть представлено одинаково если в делителе на нечетном числе триггеров записать в таблице их состояний инверсные Сигналы с четных тркг-2о геров.. Связь между сигналами положений триггеров и цифровыми сигналами для схем на четном числе триггеров может быть пояснена на примере четЫрахфазного и пятифазного делителя. Для четырех- фазного делителя, эти соотношения приведены в табл. 1, для пятифазного - в таблице. 2.....

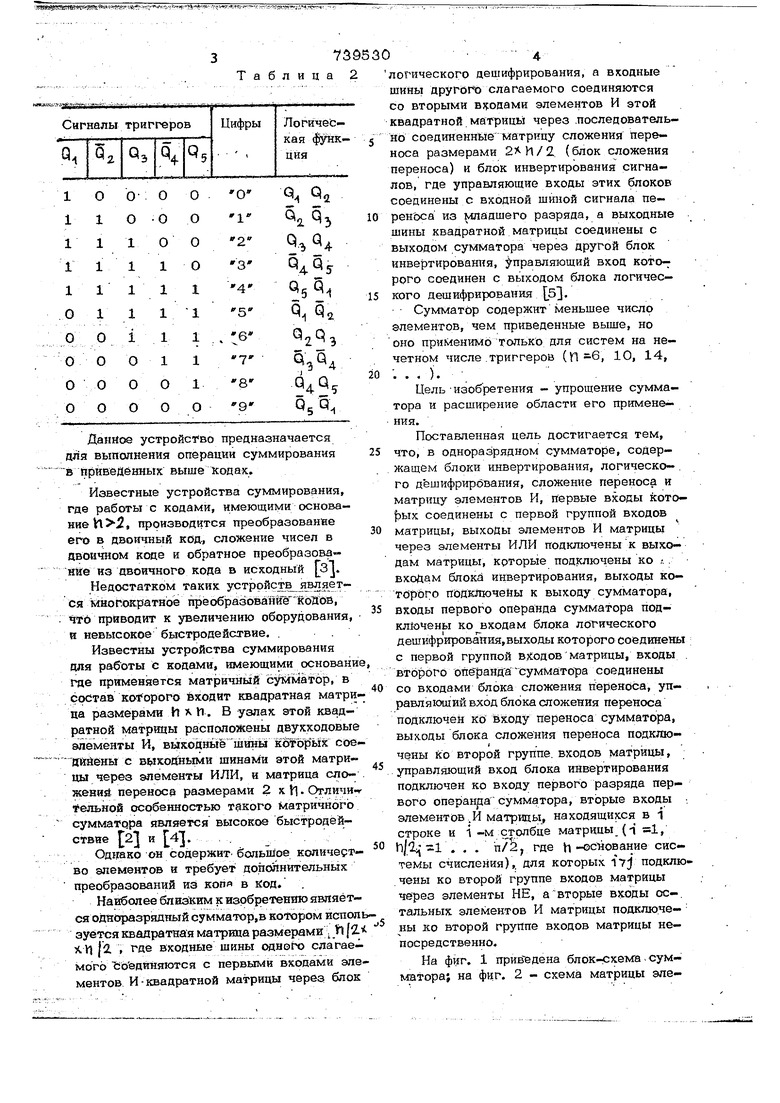

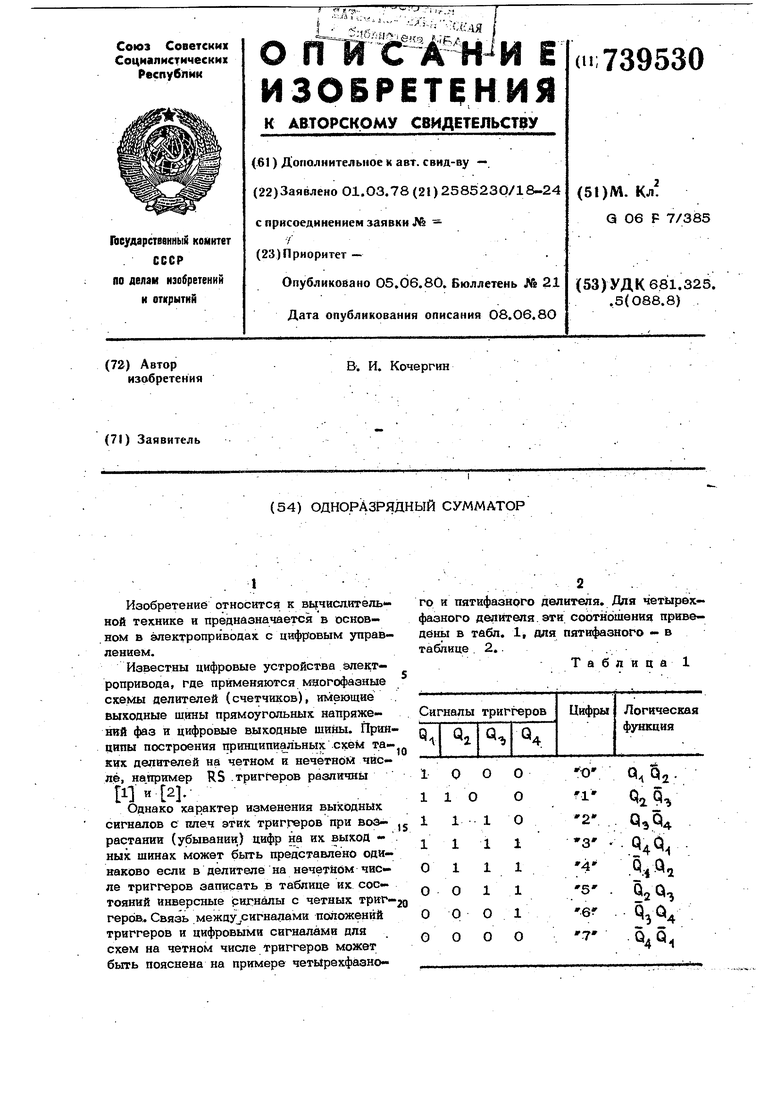

Таблица Таблица Даийое устройство предназначается ОЛЯ выполнения операции суммирования в приведённых выше кодах. Известные устройства суммирования, где работы с кодами, имеющими основание И 2, производится преобразование его в двоичный код, сложение чисел в двоичном коде и обратное преобраасваHife из двоичного кода в исходный З. Недостатком такик устррйств вляется миопократное иреобразованйё к6Жов, что приводит к увеличению оборудования, и невысокое быстродействие. .. Известны устройства суммирования для работы с кодами, имеющими основан где применяется матричный сумматор, в состав которого входит квадратная матри ца размерами ll х П. В узлах этой квадратной матрицы расположены двухходовы элементы И, выходные шины которых сое Дййбны с в 1коцнь1ми шинами этой матрицы через элементы ИЛИ, и матрица еложений переноса размерами 2 х VI. ртличи тельной особенностью такого матричного сумматора является высокое быстродействие и 4.. Оддако он содержит большое количе т во элементов и требует дополнительных преобразований из копп в код. . Наиболее близким к иарбретенйю является одйоразрядный сумматор,в котором испол зуется квадратная матрица размерами ,1П (2 к VI ji V где входные шины одного слагае мого Ьбедйняются с первыми входами эл ментов И-квадратной матрицы через блок логического дешифрирования, а входные шины другого слагаемого соединяются со вторыми входами элементов И этой квадратной матрицы через .последовательно соединенные матрицу сложения переноса размерами (блок сложения переноса) и блок инвертирования сигналов, где управляющие входы этих блоков соединены с входной шиной сигнала переноса из младшего разряда, а выходные шины квадратной матрицы соединены с выходом сумматора через другой блок инвертирования, j-правляющий вход кото рого соединен с выходом блока логического дешифрирования 53 Сумматор содержит меньшее число элементов, чем приведенные выше, но оно применимо только для систем на нечетном числе .триггеров (ri-6i Ю, 14, -. ..).. Цель-изобретения - упрощение сумматора и расширение области его примене- Поставленная цель достигается тем, что, в одноразрядном сумматоре, содержащем блоки инвертирования, логического дешифрирования, сложение переноса и матрицу элементов И, первые входы которых соединены с первой группой входов матрицы, выходы элементов И матрицы через элементы ИЛИ подключены к выходам матрицы, крторые подключены ко ;.. входам блоки инвертирования, выходы котбрбго подключейы к выходу сумматора, входы первого операнда сумматора подключены ко входам блока логического дешифрирования,выходы которого соединены с первой группой вх;сдов матрицы, входы второго операнда сумма;тора соединены со входами блока сложения переноса, управляющий вход блока сложения переноса подключен ко Входу переноса сумматора, выходы блока сложения переноса подклю... чены fco второй группе, входов матрицы, управляющий вход блока инвертирования подключен ко входу первого разряда первого операнда сумматора, вторые входь .. элементов .И матрицы, находящихся в i строке и i -м голбце матрицы (п 1, l -1 . . . п72, где h -основание системы счисления),. для которых 17j подключены ко второй группе входов матрицы через элементы НЕ, авторые входы ос-, тальных элементов И матрицы подключены ко второй группе входов матрицы непосредственно. На фиг. 1 приведена блок-схема. сумматора} на фиг. 2 - схема матрицы элементов И} на фиг. 3 - схема блока сложения переноса. Для рассмотрения принята система с основанием Я 10. Входные шины первого слагаемого А соединены с входом блока 1 логическо- .го дешифрирования, который имеет выходные шины О V 5 ,, Ч Q2,,VQ2Q5, a Vr SQ4 A,N65q;. « Выходные шины блока 1 логического дешифрирования соединены с входными, шинами первого слагаемого квадратной матрицы 2 элементов И. Входные шины второго слагаемого квадратной матрицы 2 соединены с входными шинами второго слагаемого суммиpyiomero устройства через блок 3 сложения переноса. Выходные шины матрицы 2 элементов И подключены ко входам блока 4 инвертирования. В узлах матрицы 2 установлены логические элембнты 5-29 И. Первые входы элементов 5, 11, 17, 23, 29 И. соединены с входной шиной О V 5, элементов 6, 12, 18, 24, 25 И - с шиной V 6; элементов 7, 13, 19, 20, 26 И - с шиной 7; элементов 8, 14 15, 21, 27 И с шиной 3 V 8; элементов 9, 1О, 16 22, 28 И - с шиной 4 9. I Входная шина Р второго слагаемого В соединена с вторыми вх(жами элементов 4-9 И; шина Р- со входами эпемен- тов 11-14 И и через элемёйт 30 НЕ со вторым входом элемента 6 И; шина Р элементов 17-22 И и через элемент 31 НЕ со вторыми входамн элементов 11, 1 15, 16; шина Рд. элементов 23,. 24 и через элемент 32 НЕ со втооыми входами элементов И на F со Вторы входом элемента 29 И и через элемент 33 НЕ со вторым входом элементов 2S28 И.. Выходные шины элементов .5, 10, 15 20, 25 И через элемент 34 ИЛИ соединены, с выходной шиной 5 квадратной мат рицы 2; выходы элементов 6, 11, 16, 2li 26 И через алемент 35 ИЛИ - с выходной шиной З, выходы элементов 7,12, 17, 22, 27 И через элемент 36 , ИЛИ - с шиной S, выходы элементов 8,13, 18, 23, через элемент 37 ИЛИ - с шиной 5д J выходы элементов 9,14. 19, 24, 29 И - с выходной шаной . . 73 О Входная шина сигнала переноса С через элемент 39 НЕ соединена с первыми входами элементов 40-44 И, а первые входы элементов 45-49 И соединены непосредственно с этой шиной. Вторые вкоды элементов 40, 45 И соединены с входной ши;ной Rf , вторые элементов 41, 46 И.- с шиной R. ; вторые входы элементов 42, 47 И - с шиной R, вторые входы элементов 43, 48 И - с шиной РЛ . Входная шина Р соединена со вторым входом элементов 44 И и через элемент 5 О НЕ - со вторым входом элемента 49. Выходы элементов 4 О, 49 И соединены через элемент 51 ИЛИ - с выходной шиной выходы элем4н- тов 41,45 И через элемент 52 ИЛИ с шиной РЗ выходы элементов 42, 46 И через элемент 53 ИЛИ - с шиной Р ; выходы элементов 43, И через элемент 54 ИЛИ - с шиной РА , выходы элементов 44, 48 И через элемент 55 ИЛИ - с шиной PZ. Выходные шины квадратной матрицы элементов И соединяются с выходными шинами сумматора через блок 4 инвертирования, который пропускает сигналы с выходных шин к&адратной матрицы 2 без изменения при наличии сигнала на управляющей шине блока 4, которая соединена с входной шиной Q первого слагаемого, и изменяет.все сигналы на обратные при отсутствии сигнала Q, . Работу сумматора первоначально рас- сматривают при отсутствии сигнала на шине переноса . В этом случае сигналы слагаемого В будут переданы на вход квадратной матрицы 2 через блок 3 сложения переноса без изменения, так как на первые входы элементов 4О-44И блока 3 сложения переноса поступают сигналы 1, а на вторые входы поступают сигналы слагаемого В. При цифрак О - 4 слагаемого А (см. табл. 2) и, следовательно, блок 4 инвертирования будет пропускать сигналы квадратной матрицы 2 без изменения на выходные шины сумматора. В квадратной, матрице 3 при цифре О слагаемого А {ОN 5 - 1) элементы 5, 11, 17, 23, 29 И главной диагонали пропускают сигналы слагаемого В на выходные Шины суммирующего устройства без изменения, что соответствует сложению цифр слагаемого А с цифрой О слагаемого В. При цифре I слагаемого А ( ) Р( слагаемого В будет

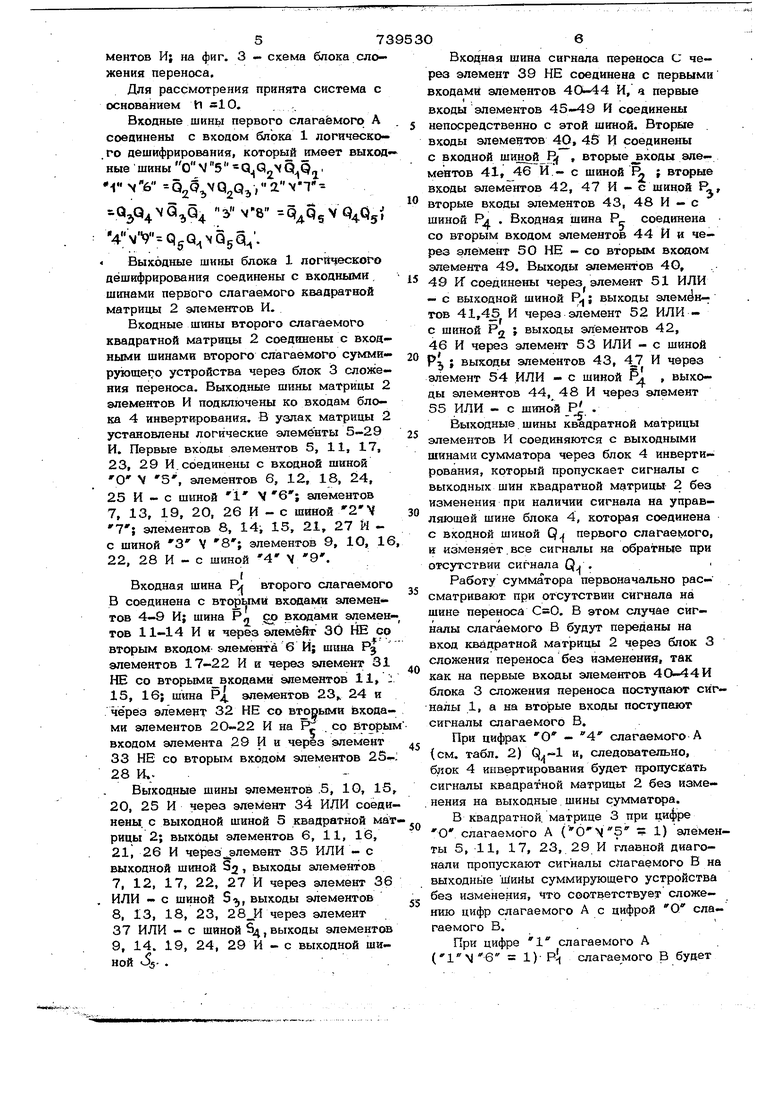

п аредан на выходную шину ; сигнал Р.2 - на шину .5 j: сигнал Pj - на шину S; сигнал pi - на шину S,.; сигнал PC будет передан с инверсией на выходную шину 5, Всё это схематически изображено на диаграмме 1, где в узлах квадратной сетки покааань п|р6водящие элементы (знак + (плюс) проводящие без изменения сигнала, знак - плинус) - инвертирующие входные с игналы). Эт и эле менты пропус кают сигналы слагаемого В на выходные ши-

Диаграмма 1

8

739530

йы суммирующего устройства. Когда коды числа В изменяются от цифры О до цифры 9, на выходных шинах суммируюшего устройства будут соответственно появляться коды сигналов цифр , 2, . . . 9, О, что соответствует сложению цифр числа В с цифрой числа А.

Сложение цифр слагаемого В с цифрой 2 числа А происходит аналогичным образом, диаграмма 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор | 1977 |

|

SU734681A1 |

| Устройство для суммирования | 1978 |

|

SU822183A2 |

| Устройство для суммирования | 1979 |

|

SU868750A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1979 |

|

SU922728A1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для алгебраического сложения | 1985 |

|

SU1297035A1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

л. 1 го

О

Диаграмма 2

В диа грамме 2 при измёйёййй кЩов числа В or цифры О до 9 на выходиго О

9

8

7

6

4

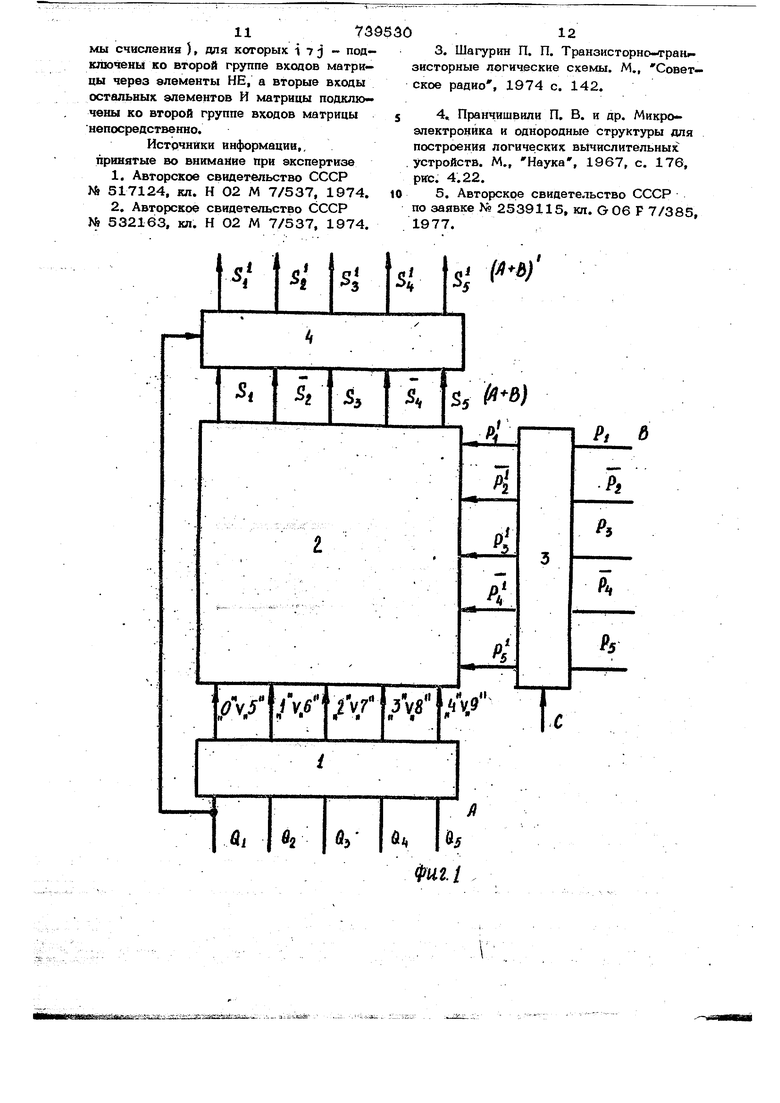

ных шина.х суммирующего устройства будут соответственно появляться коды 97 цкфр 2, 3. . . ., 9, 0. , что соответствует сложению цифр числа В с цифрой 2 числа А. Работа устройства при цифрах 3, 4 числа А проходит аналогичным обраэом. При цифрах 5 - 9 слагаемого А Gt О V и блок 4 инвертирования будет из менять выходные сигналы квадратной мат- о РИДЫ 2 на обратные. Работа квадратной Диаграмма 3 Изменение кодов цифр числа В от О до 9 при этом будет приводить к изменению кодов на выходе суммирующе.го уст ройства в следующем порядке Т, 8 9, О, . . . 6, что соответствует сложению цифр числа В сцифрой 7 числа А и т. д. Если на суммирующее устройство подается сигнал переноса с младшего разряда , то он поступает на входы элементов 45 - 49 И блока 3 сложения переноса, на другие входы которых поступают коды сигналов цифр слагаемого В. Работа блока 3 сложения переноса при этом будет совпадать с диаграммой 1, что требуется для правильного функционирования сумматора в целом. По сравнению с известным количество оборудования в предлагаемом сумматоре уменьшено. Кроме того данный сумматор применим не только для систем с основанием t1 - О, 10, 14но и для П -4, 6, 8, 10, 12, 14, ... Формула изобретения Одноразрядный сумматор, содержащий блоки инвертирования, логического дешиф-

eSSSi-ib«;-;s- Jif-a-;i

О 2 3 4

8

5 б 7 0 матрицы при этом полностью будет совпа дать с работой при кодах цифр О 4 числа А , но на выходе сумматора сигналы будут изменены на обратные. Например, при цифре 7 числа А работа сумматора будет описываться диаграммой 3, отличие которой от диаграммы 2 для цифры 2 заключается в инвертирований всех выходных сигналов, что может быть представ- лено изменением знаков проводящих эле- ментов в узлах квадратной сетки. pиpoвaнvIя, сложения переноса, и матрицу элементов И, первые входы которых соединены с первой группой входов матрицы, выходы элементов И матрицы через элементы ИЛИ подключены к выходам матрицы, которые подключены к входам блока инвертирования, выходы которого подключены к выходу сумматора, выходы первого операнда сумматора подключены к входа-м блока логического дешифрирования, выходы которого соединены с первой группой входов матрицы, входы второго Операнда сумматора соединены со входами блока сложения переноса., управ.ляющий вход блока сложения переноса, подключен ко входу переноса сумматора, отличающийся тем, что, с целью упрощения сумматора и расширения области, егб применения, вьгходы бяока сложения переноса подключены ко второй группе входов матрицы, управляющий вход блока инвертирования подключен ко входу первого разряда первого операнда сум1 атора, вторые входы элементов И матрицы, находл-щихся (Е Ч-ой строке и j -ом- столбце матрицы ( 1 +1 . . . п/2, J 1 . . . п/2, где Ц -основание системы счисления ), для которых i 7 j - подключены ко второй группе входов матрицы через элементы НЕ, а вторые входы остальных элементов И матрицы подключены ко второй группе входов матрицы непосредственно.

Источники информации,, принятые во внимание при экспертизе

6 517124, кл. Н 02 М 7/537, 1974.

NJ 532163, кл. Н О2 М 7/537, 1974.

4, Пранчишвили П. В. и др. Микроэлектроника и однородные структуры для построения логических вычислительных устройств. М., Наука, 1967, с. 176, рис. 4.22.

Авторы

Даты

1980-06-05—Публикация

1978-03-01—Подача