(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1979 |

|

SU922728A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1989 |

|

SU1633393A1 |

| Устройство для умножения | 1979 |

|

SU826341A1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| Устройство для суммирования | 1978 |

|

SU822183A2 |

| Одноразрядный сумматор | 1977 |

|

SU734681A1 |

| Цифроаналоговый преобразователь с многофазным выходом | 1987 |

|

SU1476611A1 |

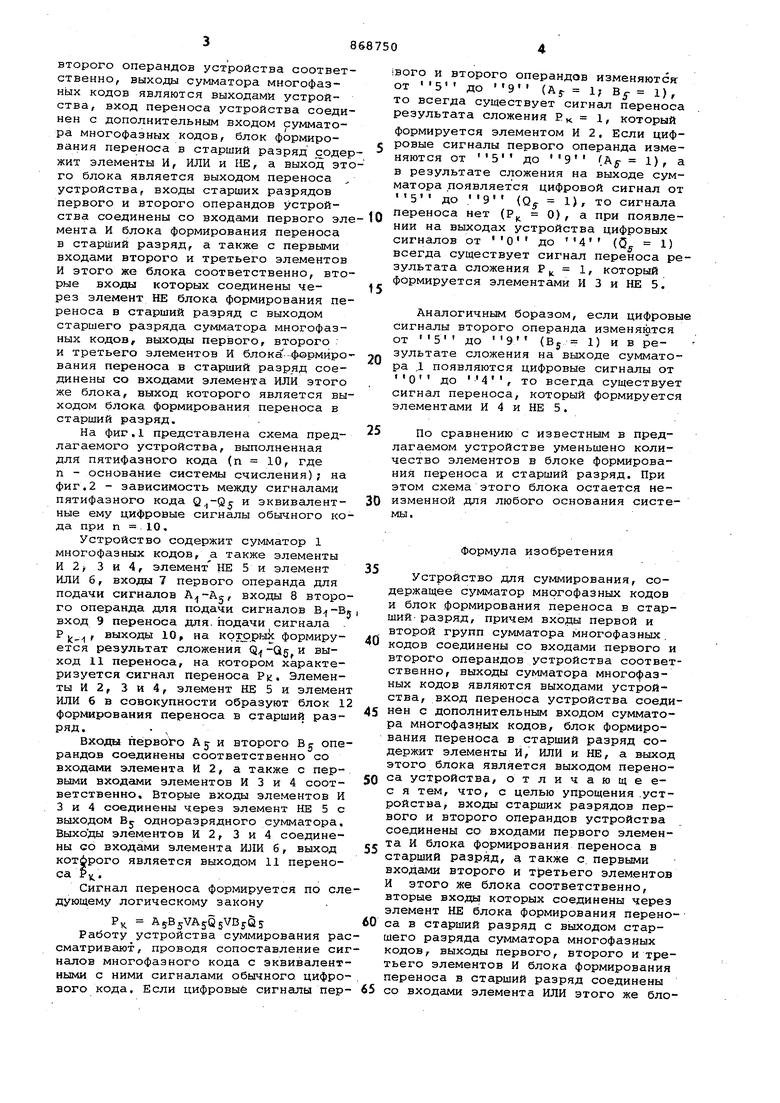

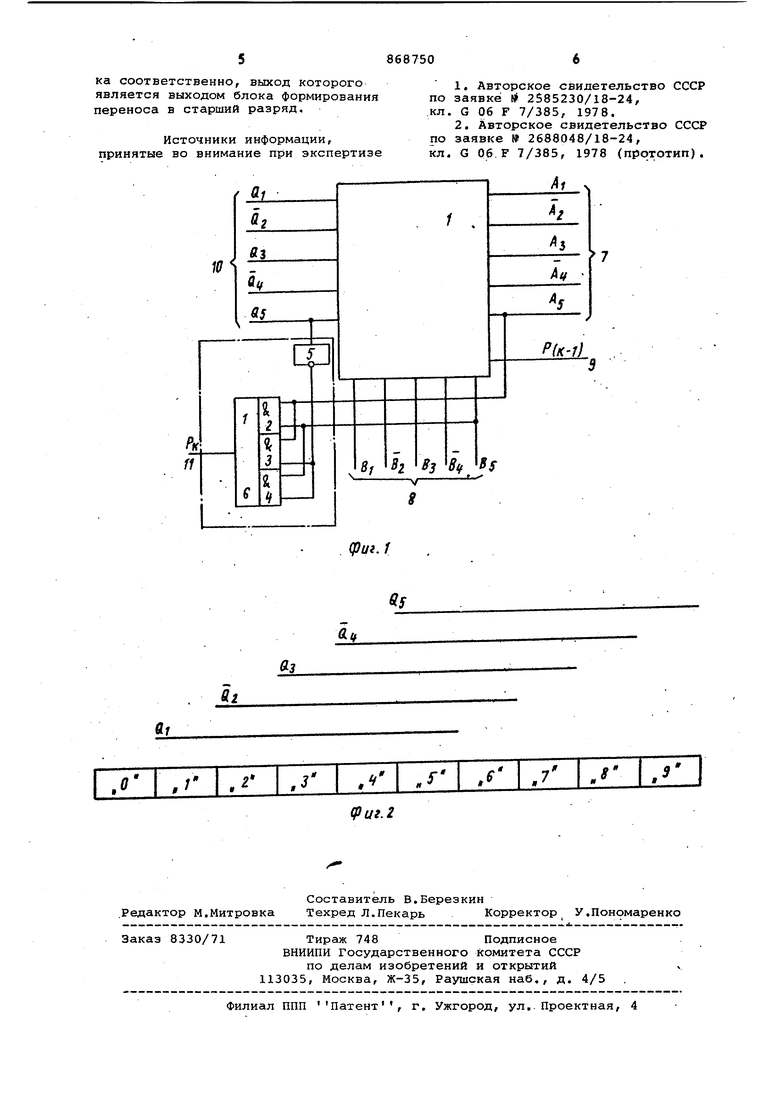

Изобретение относится к вычислительной технике и предназначается, в основном, для использования в электро приводах постоянного и переменного тока с цифровым управлением. Известен одноразрядный сумматор для работы с многофазными кодами, в котором используется квадратная матрица из двухвходовых элементов И раз мерами П/2ХП/2, где входные шины од ного слагаемого соединяются с первыми йходами элементов И квадратной матрицы через блок логического дешиф рирования, а входные шины другого сл гаемого соединяются со вторыми входа ми элементов И этой квадратной матри цы через блок сложения переноса (мат рица сложения переноса) размерами 2 5(,п/2. Выходные шины Квадратной мат ришл соединены с выходными шинами успхэйства через блок инвертирования управляющий вход которого соединен со входной шиной второго слагаемого 1 . Этот сумматор отличается высоким быстродействием, содержит небольшое количество элементов, но обладает ог раниченными функциональными возможностями, поскольку не формирует сигнал переноса в старший разряд, что не позволяет строить на его основе схемы многоразрядных сумматоров. Известно также устройство для суммирования, осуществляющее суммирование многофазных кодов, в котором формируется сигнал переноса в старший разряд, что позволяет осуществлять суммирование многоразр:ядных чисел. Это устройство содержит дешифратор, матрицу элементов И, блок сложения переноса и инверсный блок, образующие сумматор многофазных кодов, и блок формирования переноса в старший разряд, который содержит четыре элемента И, два элемента ИЛИ и два элемента НЕ 2 . Недостатком указанного устройства является его сложность, обусловленная, в частности, сложностью выполнения блока формирования переноса в старший разряд. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройстве для суммирования, содержащем сумматор многофазных кодов и блок формирования переноса в старший разряд, причем входы первой и второй групп сумматора многофазных кодов соединены со входами первого и второго операндов устройства соответственно, выходы сумматора многофазных кодов являются выходами устройства, вход переноса устройства соединен с дополнительным входом сумматора многофазных кодов, блок формирования переноса в старший разряд содер жит элементы И, ИЛИ и IIE, а выход это го блока является выходом переноса , устройства, входы старших разрядов первого и второго операндов устройства соединены со входами первого эле мента И блока формирования переноса в старший разряд, а также с первыми входами второго и третьего элементов И этого же блока соответственно, вторые входы которых соединены через элемент НЕ блока формирования переноса в старший разряд с выходом старшего разряда сумматора многофазных кодов, выходы первого, второго и третьего элементов И блока ф©рмиро вания переноса в старший разряд соединены со входами элемента ИЛИ этого же блока, выход которого является вы ходом блока формирования переноса в старший разряд. На фиг.1 представлена схема предлагаемого устройства, выполненная для пятифазного кода (п 10, где п - основание системы счисления); на фиг,2 - зависимость между сигналами пятифазного кода и эквивалентные ему цифровые сигналы обычного ко да при п 10, Устройство содержит сумматор 1 многофазных кодов, а также элементы И 2, 3 и 4, элемент НЕ 5 и элемент ИЛИ б, входы 7 первого операнда для подачи сигналов , входы 8 второ го операнда для подачи сигналов В-| -B вход 9 переноса для. подачи сигнала . Р 1 , выходы 10, на котгорых формируется результат сложения , и выход 11 переноса, на котором характеризуется сигнал переноса РК. Элементы И 2, 3 и 4, элемент НЕ 5 и элемен ИЛИ 6 в совокупности образуют блок 1 формирования переноса в старший разряд. Входы первого Aj и второго В опе рандов соединены соответственно со входами элемента И 2, а также с первыми входами элементов И 3 и 4 соответственно. Вторые входы элементов И 3 и 4 соединены через элемент НЕ 5 с выходом Bj одноразрядного сумматора. Выходы элементов И 2, 3 и 4 соединены со входами элемента ИЛИ 6, выход котброго является выходом 11 переноса Р. Сигнал переноса формируется по сл дующему логическому закону Р A5B5VA5Q5VBjQ5 Работу устройства суммирования ра сматривают, проводя сопоставление си налов многофазного кода с эквивалент ными с ними сигналами обычного цифро вого кода. Если цифровые сигналы пер вого и второго операндов изменяются от 5 до 9 (AS- 1; Bf 1), то всегда существует сигнал переноса результата сложения РК 1, который формируется элементом И 2, Если цифровые сигналы первого операнда изменяются от 5 до 9 (А 1), а в результате сложения на выходе сумматора появляется цифровой сигнал от 5 до 9 (Q 1), то сигнала переноса нет (Р 0), а при появлении на выходах устройства цифровых сигналов от О до {Q 1) всегда существует сигнал переноса результата сложения РК 1, который формируется элементами И 3 и НЕ 5. Аналогичньом боразом, если цифровые сигналы второго операнда изменяю.тся от до 9 (By 1) и в результате сложения на выходе сумматора ,1 появляются цифровые сигналы от О до 4 , то всегда существует сигнал переноса, который формируется элементами И 4 и НЕ 5. По сравнению с известным в предлагаемом устройстве уменьшено количество элементов в блоке формирования переноса и старший разряд. При этом схема этого блока остается неизменной для любого основания системы. Формула изобретения Устройство для суммирования, содержащее сумматор многофазных кодов и блок формирования переноса в старший- разряд, причем входы первой и второй групп сумматора многофазных кодов соединены со входами первого и второго операндов устройства соответственно, выходы сумматора многофазных кодов являются выходами устройства, вход переноса устройства соединен с дополнительным входом сумматора многофазных кодов, блок формирования переноса в старший разряд содержит элементы И, ИЛИ и НЕ, а выход этого блока является выходом переноса устройства/ отличающеес я тем, что, с целью упрощения .устройства, входы старших разрядов первого и второго операндов устройства соединены со входами первого элемента И блока формирования переноса в старший разряд, а также с. первыми входами второго и третьего элементов И этого же блока соответственно, вторые входы которых соединены через элемент НЕ блока формирования переноса в старший разряд с выходом старшего разряда сумматора многофазных кодов, выходы первого, второго и третьего элементов И блока формирования переноса в старший разряд соединены со входами элемента ИЛИ этого же блока соответственно, выход которого является выходом блока формирования переноса в старший разряд. Источники информации, принятые во внимание при экспертизе 8687

(риг. 2 50 1.Авторское свидетельство СССР по заявке N 2585230/18-24, кл. G 06 F 7/385, 1978. 2.Авторское свидетельство СССР по заявке 2688048/18-24, кл. G 06 F 7/385, 1978 (прототип).

Авторы

Даты

1981-09-30—Публикация

1979-05-22—Подача