(54) УСТРОЙСТВО ДЛЯ ВЬ1ЧИСЛЕНИЯ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления оценок математического ожидания и дисперсии | 1983 |

|

SU1280392A1 |

| АНАЛИЗАТОР НАПРЯЖЕНИЯ | 1990 |

|

RU2024880C1 |

| Устройство для моделирования вероятностных сетевых графиков | 1982 |

|

SU1022177A1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1383398A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Адаптивный вычислитель оценки математического ожидания | 1981 |

|

SU982014A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Вероятностный коррелометр | 1978 |

|

SU942037A1 |

| Адаптивный статический анализатор | 1985 |

|

SU1305730A1 |

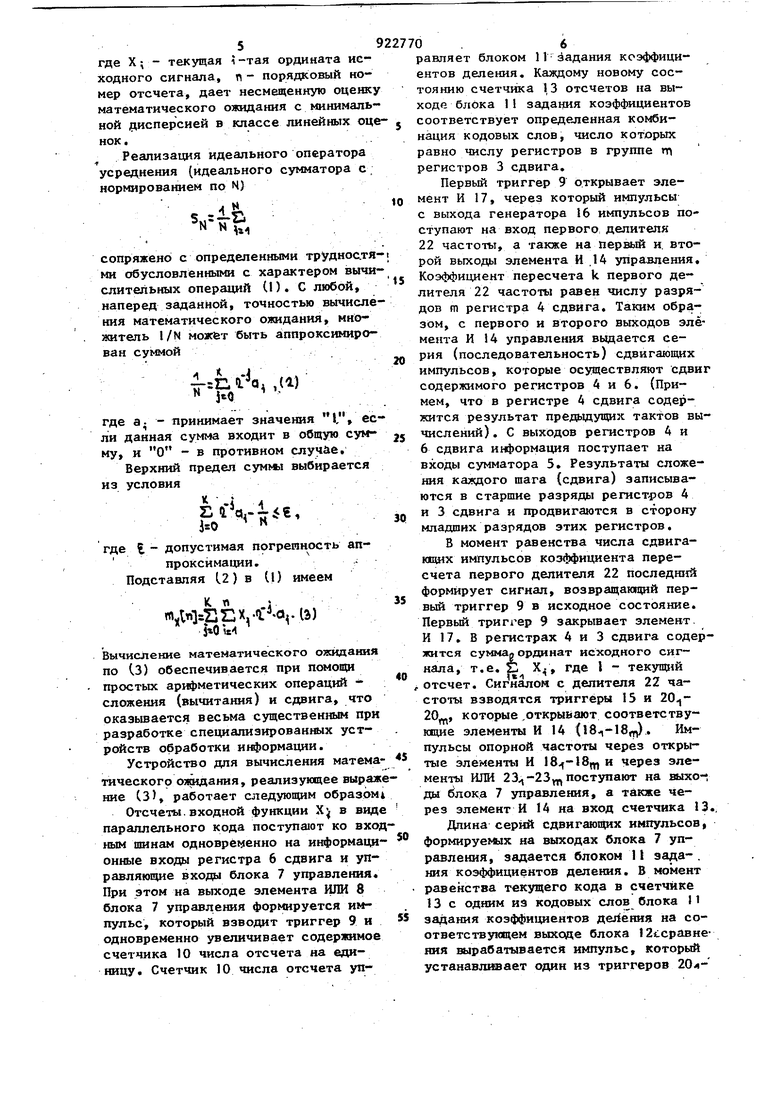

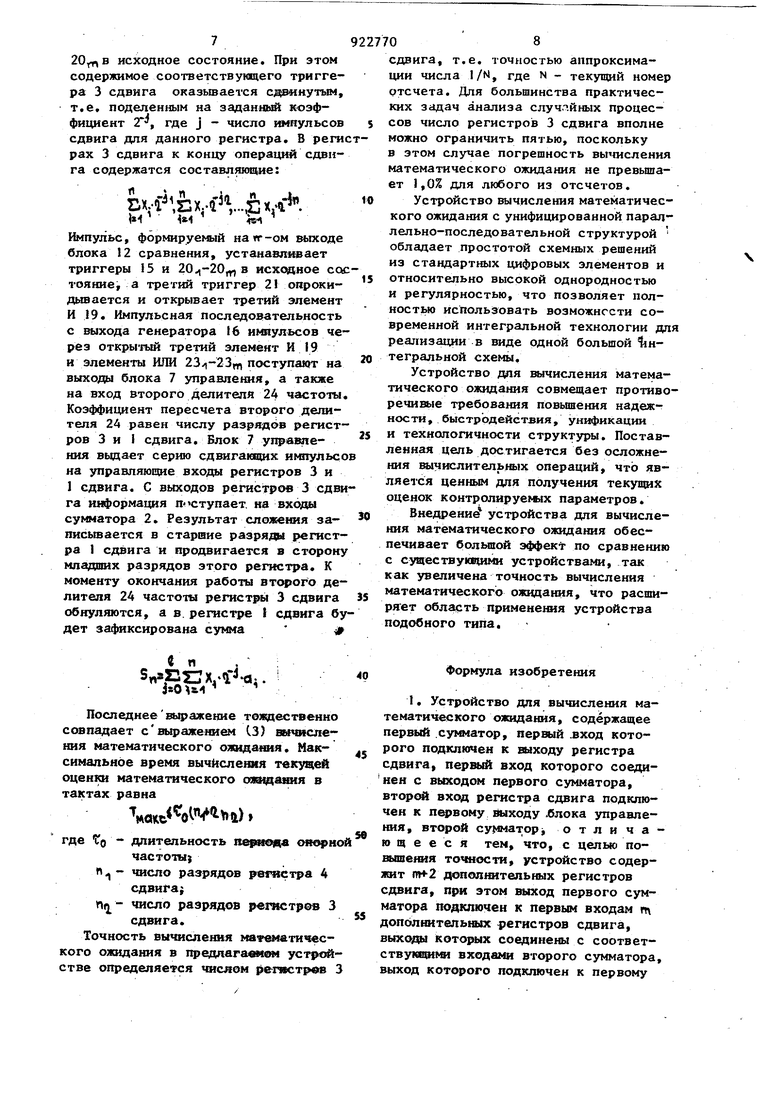

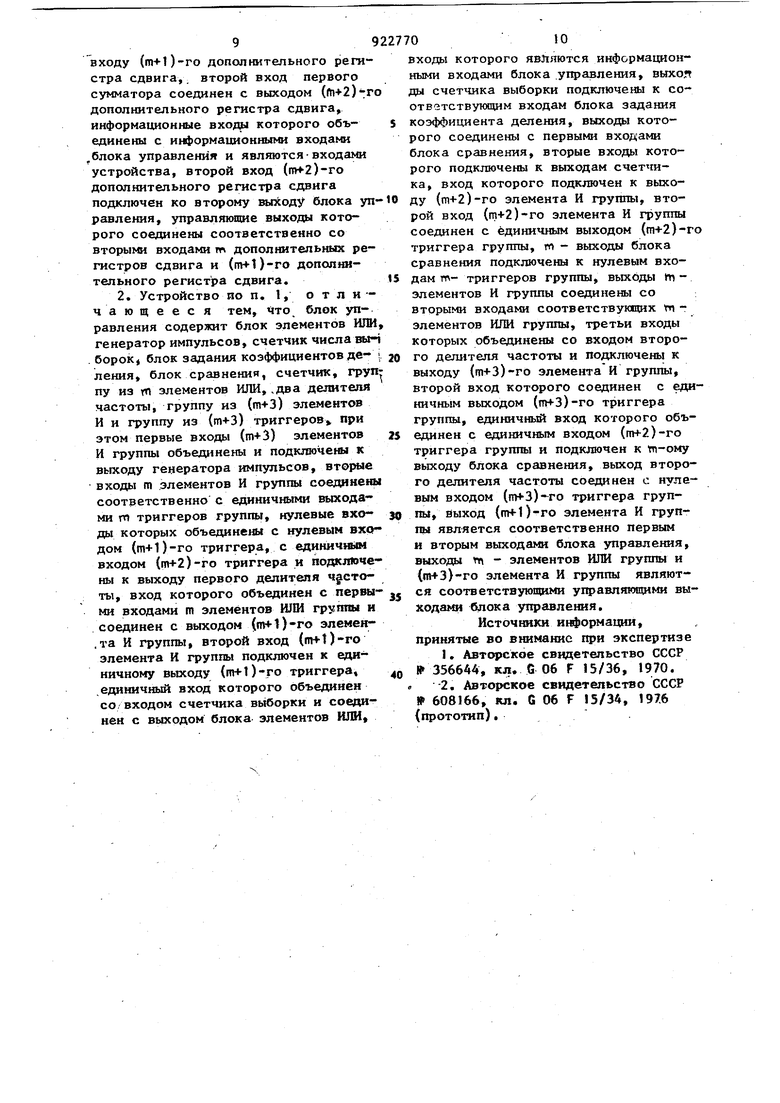

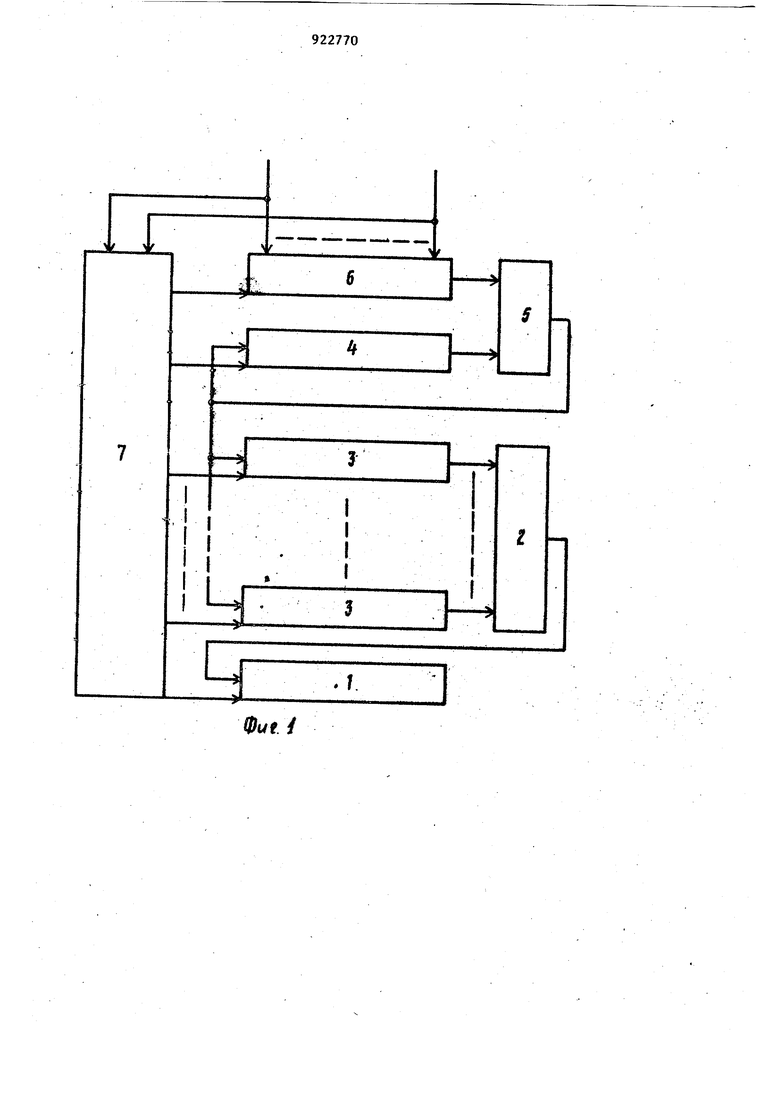

, 1 Изобретение относится к автоматике и вычислительной технике и может бЫ1 использовано для аппаратурного анализ процессов и статистической обработки массивов данных. Известно сглаживающее устройство, содержащее регистр, первый сумматор, два элемента И, элемент ИЛИ, триггер знака, Это устройство реализует алгоритм согласно рекуренткой формуле СгкГ тл - T5 iVA где Xgfn гАч-Т соответственно } и (1-1)ое значение сглаживаемого сигнала: Хц - текущая I-тая ордината исходного сигнала tn. Это устройство имеет более простую схему, однако оценка математического ожидания, вычисляемая е помощью приведенного алгоритма, является недостаточно эффективной, в связи с чем устройство имеет низкое быстродействие. Наиболее близким к предлагаемому по технической сущности является цифровое сглаживающее устройство, содержащее первый сумматор, первый вход которого подключен к выходу регистра сдвига, первый вход которого соединен с выходом первого сумматора, второй вход регистра сдвига подключен к первому выходу блока управления, второй сумматор 2. - Недостатком устройства является низкая точность вычисления математического ожидания, так как вычисление математического ожидания дает смещенную оценку из-за неоптимальности реализуемого оператс а усреднения. Данный метод вычисления характеризуется также накоплением ошибок, что также увеличивает общую погрешность вычисления математического ожидания. Это ограничивает применение данного устройства при анализе случайных процессов. Цель изобретения - повьшение точности устройства. Поставленная цель достигается тем что устройство для вычисления математического ожидания, содержит т+2 дополнительных регистров сдвига, при этом выход первого сумматора подключен к первым входам т- дополнительн регистров сдвига, выходы которых сое динены с соответствующими .входами второго сумматора, выход которого подключен к первому входу tntl дополнительного регистра сдвига, второй вход первого сумматора соединен с выходом (т+2)-го дополнительного ре гистра сдвигов, информационные входы которого объединены с инфррмащюнньо 1и входами блока управления и явля ются входами устройства, второй вход (т+2)то дополнительного регистра сдвига подключен ко второму выходу управления, управляющие выходы которого соединены соответственно со вторыми входами m дополнительных ; регистров сдвига и (m+l)-ro дополнительного регистра сдвига. ,; Кроме того, отличакнцееся тем, что блок управления содержит блок элемеитов ИЛИ, генератор импульсов счетчик числа выборо,, блок задания коэффициентов деления, блок сравнения, счетчик группу из тп - элементов ИЛИ, два делителя частоты, группу из (т+З) элементов И и группу из () триггеров, при этом первьш вхо ды () элементов И группы объеданены и подключены к выходу генератора импульсов, вторые входы m элемен тов И группы соединены соответственно с единичными выходами m - триггеров группы, нулевые входы которых « ъединены с нулевым входом (пн-1)-го триггера, с еда ничным входом (т+2)-го триггера и подключены к выходу первого делителя частоты, вход которого объединен с первыми входами тп элементов ИЛИ группы и соединение выходом (пн-1)-го элемента И группы, второй вход (tn+1)-ro элемента И группы подключен к единичному выходу (m+t)-ro триггера, единичный вход которого объединен со входом счет- i чиха выборки и соединен с выходом блокд элементов ИЛИ, входы которого являются информационными входами блока управления, выходы счетчика выборки подключены к соответствуюпщм входам блока задания коэффициента деления, выходы которого соединены с первыми входами блока сравнения, вторые входы которого подключемз к выходам счетчика, вход которого подключен к выходу (т+2)-го элемента И группы, второй вход (пИ-2)-го элемента И группы соединен с единичным выходом (гп+2)-го триггера группы mвыходы блока сравнения подключеш) к нулевым входам т-триггеров группы, выходы m - элементов И группы соединены со вторыми входами соответствукнцих элементов ИЛИ группы, третьи входы которых объединены со входом второго делителя частоты и подкшочены к выходу (т+З)-го элемента И группы, второй вход которого соединен с единичным выходом (т+3)-го триггера группы, единичный вход которого объединен с единичным вхоДом (т+2)-го триггера группы и подключен кw-ому выходу блока сравнения, выход второго делителя частоты соединен с нулевым входом {т+3)-го , триггера группы, выход {m+l)-ro элемента И группы является соответственно первым и вторым выходами блока управ пения, выходы m - элементов ИЛИ группы и vni+3)-ro элемента И группы являются соответствуннцими управляющими выходами блока управления. I . . . , , , На фиг, 1 представлена структурная схема устройства;; на фиг. 2 - блоксхема блока управления.Устройство для вычисления математического ожидания содержит первый доп.олнитепЬ1г 1й регистр 1 сдвига, второй сумматор 2, т- регистров 3 сдвига, регистр 4 сдвига, первый сумматор 5, второй дополнительный регистр 6 сдвига, блок 7 управления. Блок управления 6, представленный на фиг. 2, содержит блок 8 элементов ИЛИ, первый триггер 9, счетчик 1о числа отсчетов , блок 11 задания коэффициентов деления, блок 12 сравнения, счетчик 13, второй элемент И 14, второй триггер 15, генератор 16 импульсов, элемент И 17, группу m элементов И ,, третий элемент И 19, группу тп триггеров , третий триггер 21, первый делитель 22 частоты, группу m элементов ИЛИ ,, второй елитель частоты 24. Среднеарифметическое значение m х fn случайной величины X .x, .И) где X; - текущая i-тая ордината исходного сигнала, п- порядковый номер отсчета, дает несмещенную оценк математического ожидания с минималь ной дисперсией в классе линейных оц нок. Реализация идеального оператора усреднения (идеального сумматора с; нормированием по N) I -1Г сопряжено с определенными труднос.тя ми обусловленными с характером вычи слительных операций (I). С любой, наперед заданной, точностью вычисле ния математического ожидания, множитель 1/N может быть аппроксимирован суммой Н/-- где а. - принимает значения I,, ес ли данная сумма входит в общую сумму, и О - в противном случае. Верхний предел сум выбирается из условия . где - допустимая погрешность аппроксимации,Подставляя (.2} в U) имеем .-гЦ.1з) Вычисление математического ожидания по (.3) обеспечивается при помощи простых арифметических операций сложения (вычитания) и сдвига, что окаэьшается весьма существенным при разработке специализированялх устройств обработки информации. Устройство дпя вычисления матема тического ожидания, реализующее выраж ние СЗ, работает следующим образом Отсчеты.входной функции Х в вид параллельного кода поступают ко вхо ным шинам одновременно на информаци онные входы регистра 6 сдвига и управляющие входы блока 7 управления При этом на выходе элемента ИЛИ 8 блока 7 управления формируется импульс, который взводит триггер 9 и одновременно увеличивает содержимое счетчика 10 числа отсчета на единицу. Счетчик 10 числа отсчета управляет блоком 11 задания коэффициентов деления. Каждому новому состоянию счетчика 13 отсчетов на выходе блока 11 задания коэффициентов соответствует определенная комбинация кодовых слов, число которых равно числу регистров в группе гп регистров 3 сдвига. Первый триггер 9 открывает элемент И 17, через который импульсы с выхода генератора 16 импульсов поступают на вход первого делителя 22 частоты, а также на первый и. второй выходы элемента И ,14 управления. Коэффициент пересчета k первого делителя 22 частоты равен числу разрядов m регистра 4 сдвига. Таким образом, с первого и второго выходов элемента И 14 управления ведается серия (последовательность) сдвигающих импульсов, которые осуществляют сдвиг содержимого регистров 4 и 6. (Примем, что в регистре 4 сдвига содержится результат предьщущих тактов вычислений) . С выходов регистров 4 и 6 сдвига информация поступает на входы сумматора 5, Результаты сложения каждого шага (сдвига) записываются в старшие разряды регистров 4 и 3 сдвига и продвигаются в сторону младших раэрядов этих регистров, В момент равенства числа сдвигаюпшх импульсов коэффициента пересчета первого делителя 22 последний формирует сигнал, возвращающий первый триггер 9 в исходное состояние. Первый триггер 9 закрывает элемент. И 17. В регистрах 4 и 3 сдвига содержится суммап ординат исходного сигнала, т.е. С Х, где I - текущий отсчет. Сигналом с делителя 22 частоты взводятся триггеры 15 и , которые .открывают соответствукщие элементы И 14 (l8-,-18). Импульсы опорной частоты через открытые элементы И и через элементы ИЛИ 23 -23 поступают на выходы блока 7 управления, а также через элемент И 14 на вход счетчика 13., Длина серий сдвигающих импульсов, формируемых на выходах блока 7 управления, задается блоком 11 зада- . ния коэффициентов деления. В момент равенства текущего кода в счетчике 13 с одним из кодовых слов блока П задания коэффициентов дeJieния на соответствующем выходе блока 12 :сравнения вырабатывается импульс, который устанавливает одии из триггеров 20л20 в исходное состояние. При этом содержимое соответствугацего триггера 3 сдвига оказьшается сда-инутым, т.е. поделенным на задан1шй коэффициент 2, где j - число да«иульсов сдвига для данного регистра. В регис рах 3 сдвига к концу операций сдвнга содержатся составляншдае: Бх....а .... |и NH 5:1 Импульс, формируеьялй на гг -ом выходе блока 12 сравнения, устанавливает триггеры 15 и 20 -20ff B исходное сос тояние, а третий триггер 2 опрокидывается и открывает третий элемент И 19. Импульсная последовательность с выхода генератора 16 импульсов через открыплй третий элемент И 19 и элементы ИЛИ поступают на выходы блока 7 управле1шя, а также на вход второго делителя 24 частоты. Коэффициент пересчета второго делителя 24 равен числу разрядов регистров 3 и I сдвига. Блок 7 управпеНИН выдает серию сдвигакщих ию1ульсо на управляющие входы регистров 3 и 1 сдвига. С выходов регистров 3 сдви га информация шютупает. на входы сумматора 2. Результат сложения записьюается в старшие разряф регистра 1 сдвига и продвигается в сторону младших разрядов этого регистра. К моменту окончания работы второго делителя 24 частоты регистры 3 сдвига обнуляются, а в. регистре I сдвига бу дет зафиксирована сумма Ф в п. vpi::x.. jsOUl Последнеевыражение теэедественно совпадает свыражением (.3) вычисления математического ожндаш1я. Максимальное время вычисления текущей оценки математического в тактах равна Wc otViH) где - длительность я й1едв offopH частоты п - число разрядов рвшстра 4 сдвига; число разрядов регистров 3 сдвига. Точность вычисления матш-штического ожидания в предлагаемом уст( стве определяется числом ре-п стрев сдвига, т.е. точностью аппроксимации числа 1/N, где N - текущий номер отсчета. Для большинства практических задач анализа случайных процессов число регистров 3 сдвига вполне можно ограничить пятью, поскольку в этом случае погрешность вы шсления математического ожидания не превьшает 1,0% для любого из отсчетов. Устройство вычисления математического ожидания с унифицированной параллельно-последовательной структурой обладает простотой схемных решений из стандартных цифровых элементов и относительно высокой однородностью и регулярностью, что позволяет полностью использовать возможности современной интегральной технологии для реализации в виде одной большой IIHтегральной схемы. Устройство для вычисления математического ожидания совмещает противоречивые требования повьппения надежности, быстродействия, унификации и технологичности структуры. Поставленная цель достигается без осложнения шлчислительных операций, что является ценным для получения текущих оценок контролируемых параметров. Внедрение устройства для вычисления математического ожидания обеспечивает большой эффект по сравнению с существуквщми устройствами, так как увеличена точность вычисления математического ожццания, что расширя ет область примене1шя устройства подобного типа. Формула изобретения 1. Устройство для вычисления математического ожидания, содержащее первый .сумматор, первый .вход которого подключен к выходу регистра сдвига, вход которого соединен с выходом первого сумматора, вторс вход регистра сдвига подключен к первому выходу .блока управления , второй сумматор -, отличающееся тем, что, с целью повыше1ШЯ точности, устройство содержит пн-2 допол1Штельных регистров сдвига, щж этом выход первого сумматора подключеи к первым входам m дополнительных регистров сдвига, выходы Которых соединены с соответCTByra iw входами второго сумматора, выход которого подключен к первому 9 входу (m+l)-ro дополнительного регистра сдвига, второй вход первого сумматора соединен с выходом ():r дополнительного регистра сдвига, информационные входы которого объединены с информаиионныни входами .блока управления и являютсявходами устройства, второй вход (т+2)-го дополнительного регистра сдвига подключен ко второму исходу блока уп равления, управляющие выходы которого соединены соответственно со вторыми входами m дополнительных регистров сдвига и (nn-l)-ro дополнительного регистра сдвига. 2. Устройство по п. 1, отличающееся тем, Что, блок управления содержит блок элементов ИЛИ генератор импульсов, счетчик числа вьН . борок, блок задания коэффициентов де- jo ления, блок сравнения, счетчик, группу из гп элементов ИЛИ,.два делителя частоты, группу из (т+З) элементов И и группу из () триггеров при этом первые входы (т+3) элементов И группы объединены и подключены к выходу генератора импульсов, вторые входы m элементов И группы соединены соответственно с единичными выходами m триггеров групты, нулевые вхо- 39 ды которых объединены с нулевым входом (т+1)-го триггера, с единичи)М входом (пН-2)-го триггера и подаелючены к выходу первого делителя Ч|стоты, вход которого объединен с первыми входами m элементов ИЛИ группы и соединен с выходом ()-го элемен.та И группы, второй вход (nn-t)-ro элемента И группы подключен к единичному выходу {m+t)-ro триггера .единичный вход которого объединен со/входом счетчика выборки и соединен с выходом блока элементов ИЛИ 25 40 010 входы которого являются информационными входами блока управления, выхо ды счетчика выборки подключены к соответствующим входам блока задания коэффициента деления, выходы которого соединены с первыми входами блока сравнения, вторые входы которого подключены к выходам счетчика, вход которого подключен к выходу (ni+2)-ro элемента И группы, второй вход (т+2)-го элемента И группы соединен с единичным выходом (т+2)-го триггера группы, т - выходы блока сравнения подключены к нулевым входам т- триггеров группы, выхода mэлементов И группы соединены со вторыми входами соответствующих тп элементов ИЛИ группы, третьи входы которых объединены со входом второго делителя частоты и подключень к выходу (т+3)-го элемента И группы, второй вход которого соединен с еди ничным выходом (пн-З)-го триггера группы, единичный вход которого объединен с единичным входом (пн-2)-го триггера группы и подключен к w-oMy выходу блока сравнения, выход второго делителя частоты соединен с. нулевым входом (пн-3) триггера группы, выход {пН-1)-го элемента И группы является соответственно первым и вторым выходами блока управления, выходы п - элементов ИЛИ группы и {iiH3}-ro элемента И группы являются соответствующими управляющими выходами блока управления, Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 356644, кл. б 06 F 15/36, 1970. -2. Авторское свидетельство СССР 9 608166, кл. G 06 F 15/34, 1976 {прототип).

f

Фие /

H

Авторы

Даты

1982-04-23—Публикация

1980-05-21—Подача