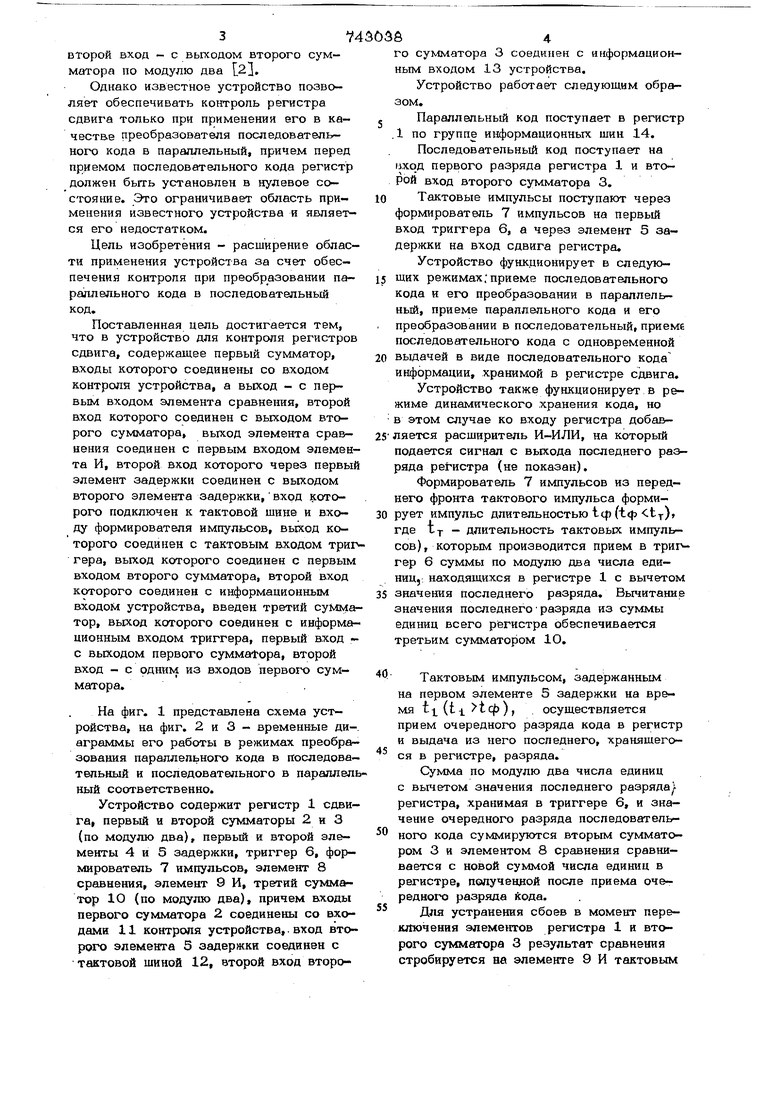

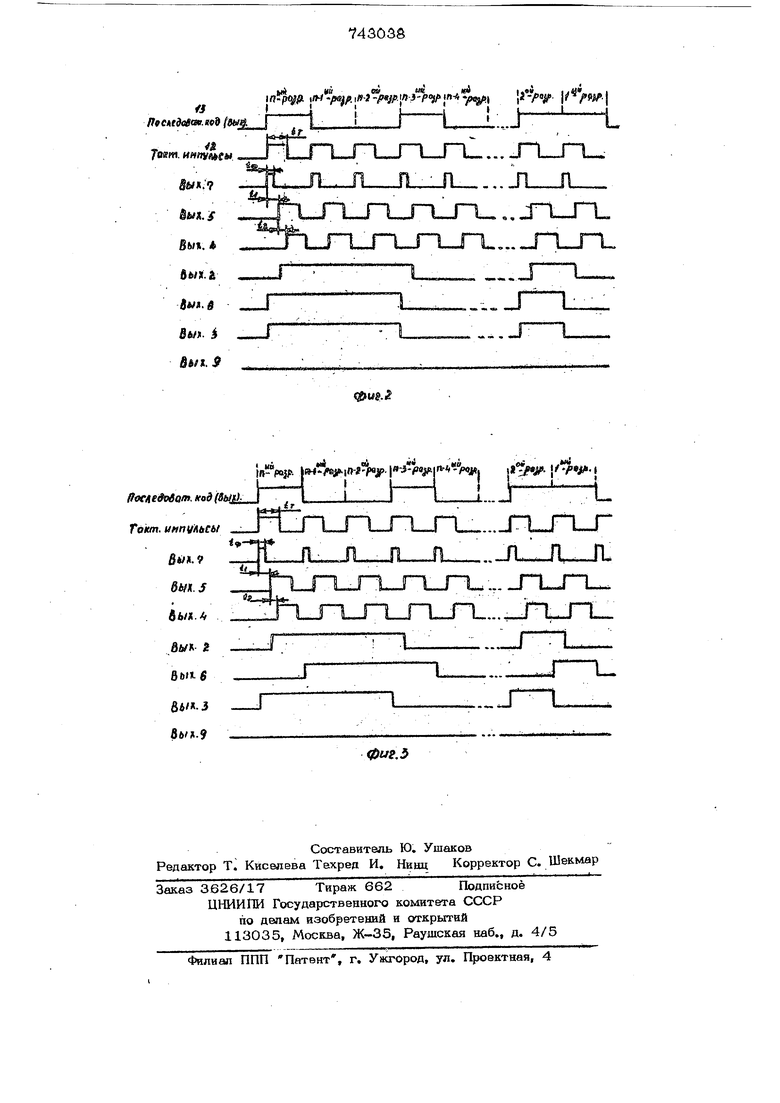

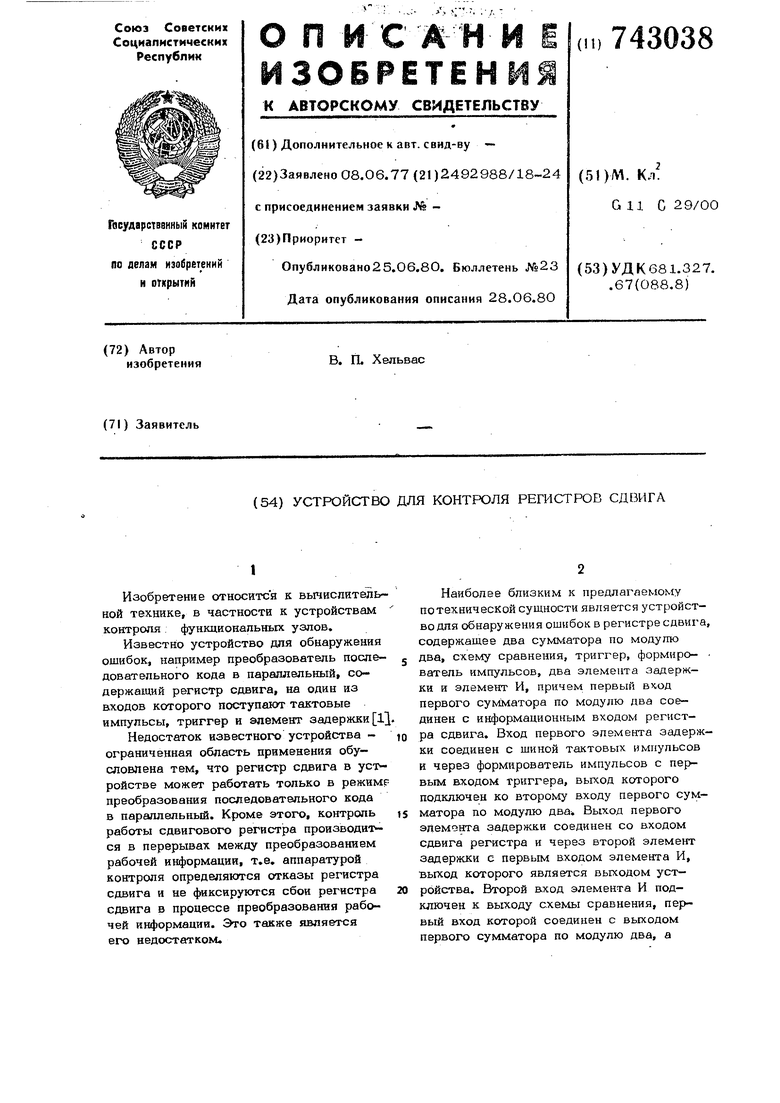

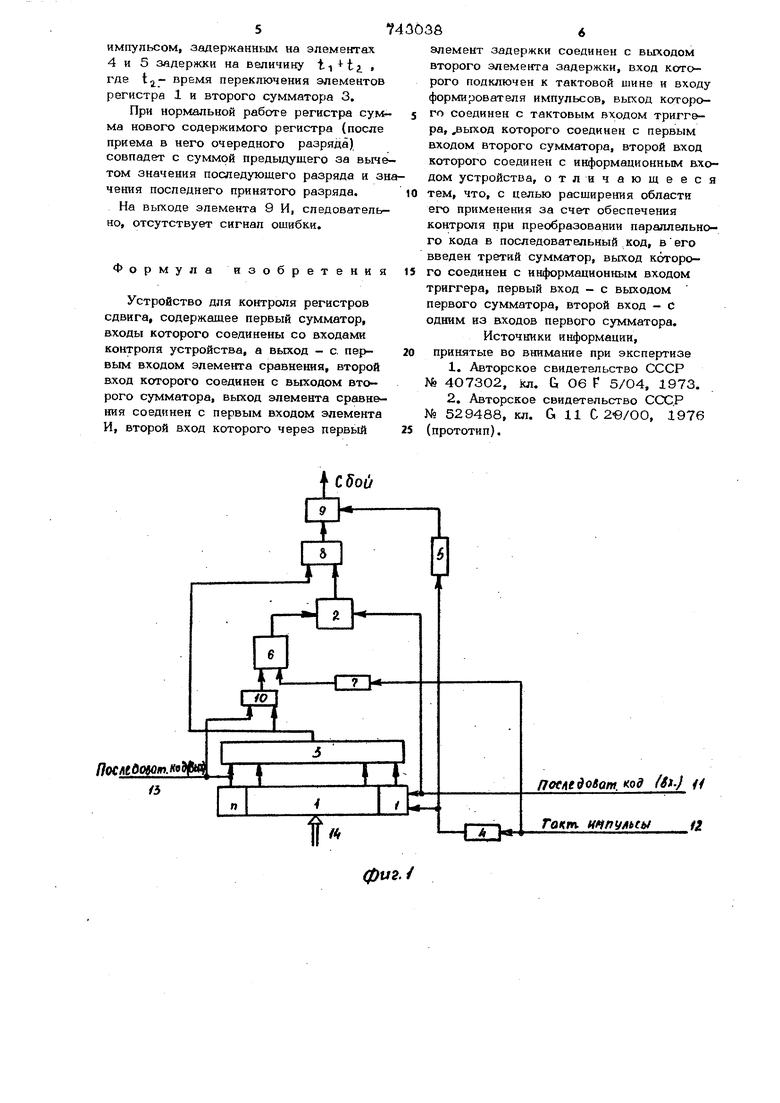

Изобретение относится к вычиспительной технике, в частности к устройствам контроля функциональных узлов. Известно устройство для обнаружения ошибок, например преобразователь последовательного кода в параллельный, содержащий регистр сдвига, на один из входов которого поступают тактовые импульсы, триггер и элемент задержки Недостаток известного устройства ограниченная область применения обусловпена тем, что регистр сдвига в устройстве может работать только в режим преобразования последовательного кода в параллельный. Кроме этого, контроль работы сдвигового регистра производит ся в перерывах между преобразованием рабочей информации, т.е, аппаратурой контроля определяются отказы регистра сдвига и не фиксируются сбои регистра сдвига в процессе преобразования рабочей информации. Это также является его недостатком. Наиболее близким к предлагаемому потехнической сущности является устройство для обнаруа ения ошибок в регистре сдвига, содержащее два сумматора по модулю два, схему сравнения, триггер, формиро- ватель импульсов, два элемента задержки и элемент И, причем первый вкод первого сумматора по модулю два соединен с информационным входом регистpa сдвига. Вход первого элемента задержки соединен с шиной тактовых импульсов и через формирователь импульсов с первьпл входом триггера, выход которого подключен ко второму входу первого сумматора по модулю два Выход первого элемента задержки соединен со аходом сдвига регистра и через второй элемент задержки с первым входом элемента И, выход которого является выходом устройства. Второй вход элемента И подключен к выходу схемы сравнения, первый вход которой соединен с выходом первого сумматора по модулю два, а второй вход - с выходом второго сумматора по модулю два 21. Однако известное устройство позволяет обеспечивать контроль регистра сдвига только при применении его в качестве преобразователя последовательного кода в параллельный, причем перед приемом последовательного коДа регистр должен быть установлен в нулевое состояние. Это ограничивает область применения известного устройства и является его недостатком. Цель изобретения - расширение области применения устройства за счет обеспечения контроля при преобразовании параллельного кода в последовательный код. Поставленная цель достигается тем, что в устройство для контроля регистров сдвига, содержащее первый сумматор, входы которого соединены со входом контроля устройства, а выход - с первым входом элемента сравнения, второй вход которого соединен с выходом второго сумматора, выход элемента сравнения соединен с первым входом элемен та И, второй вход которого через первы элемент задержки соединен с выходом второго элемента задержки,вход которого подключен к тактовой шине и входу формирователя импульсов, выход которого соединен с тактовым входом триг гера, выход которого соединен с первым входом второго сумматора, второй вход которого соединен с информационным входом устройства, введен третий сумма тор, выход которого соединен с информа ционным входом триггера, первый вход с выходом первого сумматора, второй вход - с рдним из входов первого сумматора. На фиг. 1 представлена схема устройства, на фиг. 2 и 3 - временные диаграммы его работы в режимах преобра зования параллельного кода в последова тельный и последовательного в параллел ный соответственно. Устройство содержит регистр 1 сдви га, первый и второй сумматоры 2 и 3 (по модулю два), первый и второй элементы 4 и 5 задержки, триггер 6, формирователь 7 импульсов, элемент 8 сравнения, элемент 9 И, третий сумматор 1О (по модулю два), причем входы первого сумматора 2 соединены со входами 11 контроля устройства, вход второго элемента 5 задержки соединен с тактовой шиной 12, второй вход второго сумматора 3 соединен с информацион- Hbnvi входом 13 устройства. Устройство работает следующим образом. Параллельный код поступает в регистр 1 по группе информационных шин 14. Последовательный код поступает на вход первого разряда регистра 1 и второй вход второго сумматора 3. Тактовые импульсы поступают через формирователь 7 импульсов на первый вход триггера 6, а через элемент 5 задержки на вход сдвига регистра. Устройство функционирует в следующих режимах; приеме последовательного кода и его преобразовании в параллельный, приеме параллельного кода и его преобразовании в последовательный, приеме последовательного кода с одновременной выдачей в виде последовательного кода информации, хранимой в регистре сдвига. Устройство также функционирует в режиме динамического хранения кода, но в этом случае ко входу регистра добавляется расширитель И-ИЛИ, на который подается сигнал с выхода последнего разряда регистра (не показан). Формирователь 7 импульсов из переднего фронта тактового импульса формирует импульс длительностью 1ф(1с}э Ьт), где t-|- - длительность тактовых импульсов), которым производится прием в триггер 6 суммы по модулю два числа единиц,: находящихся в регистре 1 с вычетом значения последнего разряда. Вычитание значения последнего разряда из суммы еди1гац всего р вгистра обеспечивается третьим сумматором 10. Тактовым импульсом, задержанньшс на первом элементе 5 задержки на времяtj(), . осуществляется прием очередного разряда кода в регистр и выдача из него последнего, хранящегося в регистре, разряда. Сумма по модулю два числа единиц с вычетом значения последнего разряда регистра, хранимая в триггере 6, и значение очередного разряда последовательного кода суммируются вторым сумматором 3 и элементом 8 сравнения сравнивается с новой суммой числа единиц в регистре, пелученлой после приема очередного разряда кода. Для устранения сбоев в момент переключення элементов регистра 1 и второго сумматора 3 результат сравнения стробируется на элементе 9 И тактовым импульсом, задержанным на элементах 4 и 5 зйдерюси на величину , где время переключения элементов регистра 1 и второго сумматора 3. При нормальной работе регистра сумма нового содержимого регистра (после приема в него очередного разряда) совпадет с суммой предыдущего за выче том значения последующего разряда и зн чения последнего принятого разряда. На выходе элемента 9 И, следовательно, отсутствует сигнал ошибки. Формула зобретения Устройство для контроля регистров сдвига, содержащее первый сумматор, входы которого соединены со входами контроля устройства, а выход - с. первым входом элемента сравнения, второй вход которого соединен с выходом второго сумматора, выход элемента сравнения соединен с первым входом элемента И, второй вход которого через первый

C5ou Y S6 элемент задержки соединен с выходом второго элемента задержки, вход которого подключен к тактовой шине и входу формирователя импульсов, выход которого соединен с тактовым входом триггера, ыход которого соединен с первым входом второго сумматора, второй вход которого соединен с информационным RXOдом устройства, отличающееся тем, что, с целью расширения области его применения за счет обеспечения контроля при преобразовании параллельного кода в последовательный код, вего введен третий сумматор, выход которого соединен с информационным входом триггера, первый вход - с выходом первого сумматора, второй вход - С одним из входов первого сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР NO 4О7302, кл. G, Об F 5/04, 1973. 2.Авторское свидетельство СССР № 529488, кл. G 11 02-8/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля регистров сдвига | 1980 |

|

SU924759A1 |

| Устройство для обнаружения ошибок в регистре сдвига | 1975 |

|

SU529488A1 |

| Устройство для контроля информации по модулю три | 1988 |

|

SU1580369A1 |

| Генератор последовательности чисел | 1983 |

|

SU1166089A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Устройство для умножения в дополнительных кодах | 1988 |

|

SU1695307A2 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Преобразователь кодов | 1985 |

|

SU1259494A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

Послебмоп.1(оШ

t/. / tM/Bj tft-i/Wjp. Iff- PajJ. Ноелевобот. код fSuni. Такт, инпчльсы BlH).9 вых. 5 бб/Х.Л flfi/Л г вЬ(1в б4Х-3 вбм.9 | -5-#Mj jfr«1 hH .

0wp,3 . j/., ... .....JI.-JUJI .J

Авторы

Даты

1980-06-25—Публикация

1977-06-08—Подача