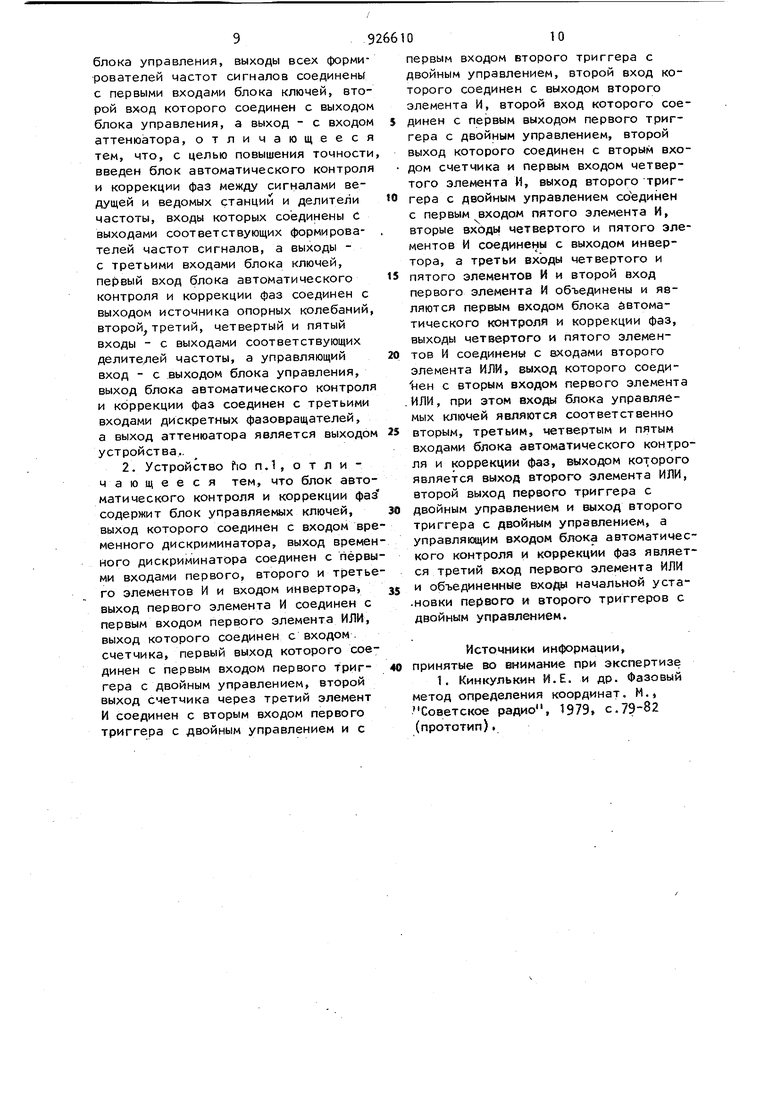

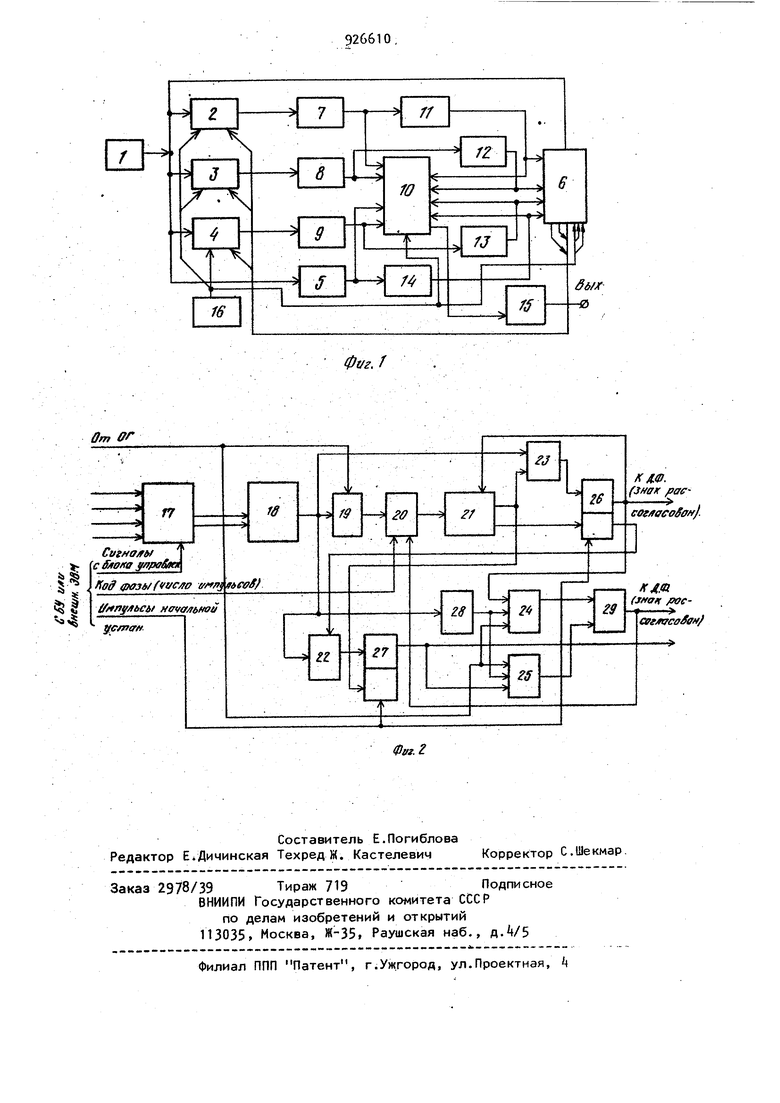

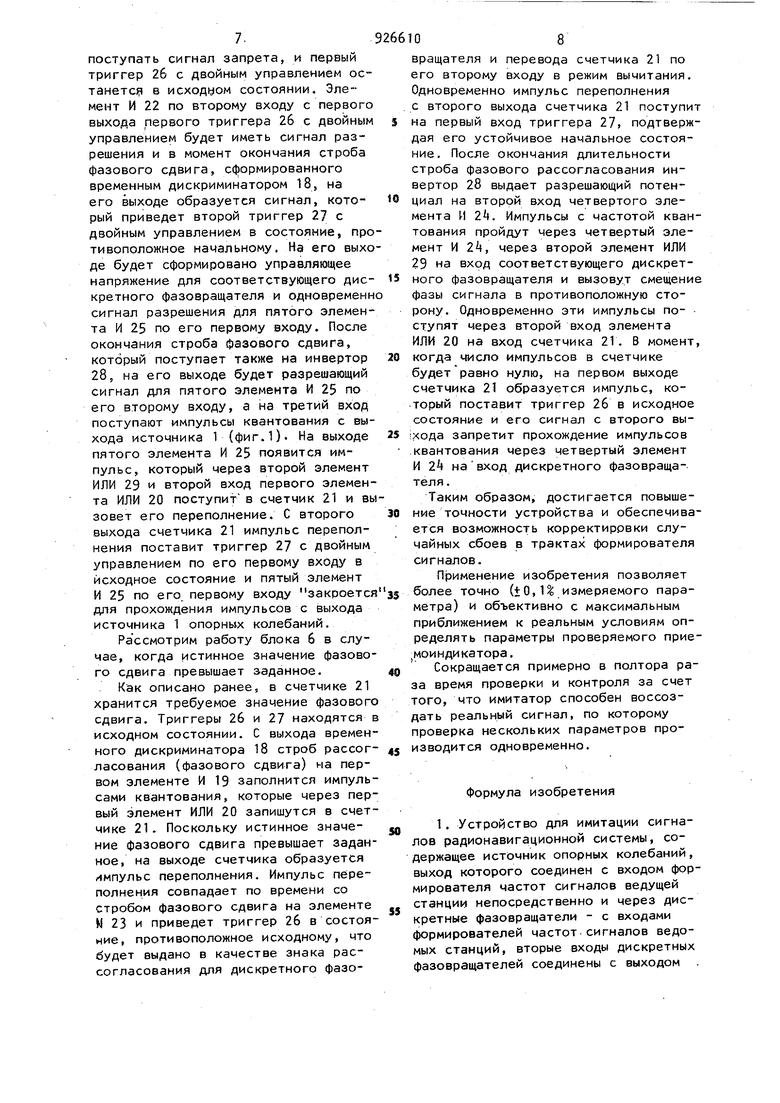

39 станции и делители частоты, входы ко торых соединены с выходами соответст вующих формирователей частот сигналов, а вььходы - с третьими входами блока ключей, первый вход блока автематического контроля и коррекции фаз соединен с выходом источника опорных колебаний, второй, третий, четвертый и пятый входы - с выходами соответствующих «делителей частоты а управляющий вход с выходом блока управления, выход блока автоматического контроля и коррекции фаз, соединен с третьими входами дискретных фазовращателей, а выход аттенюатора является выходом устройства. При этом блок автоматического кон троля и коррекции фаз содержит блок управляемых ключей, выход которого соединен с входом временного дискриминатора, выход временного дискриминатора соединен с первыми входами первого, второго и третьего элементо И и йходом инвертора, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом счетчика, первый выход которого соединен с первым входом первого триггера с двойным уп равлением, второй выход счетчика через третий злемент И соединен со вторым входом первого триггера с двойным управлением и с первым входом второго триггера с двойным управ лением, второй вход которого соединен с выходом второго элемента И, второй вход которого соединен с первым выходом первого триггера с двойным управлением, второй выход которо го соединен с вторым входом сметчика Л первым входом четвертого элемента И, выход второго триггера с двойным управлением соединен с первым входом пятого элемента И, вторые входы четвертого и пятого элементов И соедине ны с выходом инвертора, а третьи вхо ды четвертого и пятого элементов И и второй вход первого элемента И объединены и являются первым входом блока автоматического контроля и коррекции фаз, выходы четвертого и пятого элементов И соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ при этом входы блока управляемых ключей являются соответственно вторым, третьим, четвертым и пятым входами блока автоматического контроля и кор04рекции фаз, выходом которого является выход Bjoporo элемента ИЛИ, второй выход первого триггера с двойным управлением и выход второго триггера с двойным управлением, а управляющим входом блока автоматического контроля и коррекции фаз является третий вход первого элемента ИЛИ и объединённые входы начальной установки первого и второго триггера с двойным управлением. На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг,2 - вариант реализации блока автоматического контроля и коррекции фаз. Устройство (фиг.1) содержит источник 1 опорных колебаний, дискретные фазовращатели 2-k, формирователь 5 частот сигналов ведущей станции, блок 6 автоматического контроля и коррекции фаз, формирователи 7-9 частот сигналов ведомых станций, блок 10 ключей, делители 11-14 частоты, аттенюатор 15 и блок 16 управления. Блок автоматического контроля и коррекции фаз (фиг.2) содержит блок 17 управляемых ключей, временной дискриминатор 18, первый элемент И 19, первый элемент ИЛИ 20, счетчик 21, второй элемент И 22, третий элемент И 23, четвертый Элемент И 24, пятый элемент И 25, первый 2б и второй 27 триггеры с двойным управлением, инвертор 28 и второй элемент ИЛИ 29. Устройство работает следующим образом. С выхода источника 1 опорных колебаний сигнал частоты f поступает на первые входы дискретных фазовраща-телей 2-4, на вход формирователя 5 частот сигналов ведущей станции и на первый вход блока 6. С помощью дискретных фазовращателей 2-4 устанавливается любая фаза сигнала относительно фазы сигнала ведущей станции частоты 6f. Выход блока 16 управления связан с вторым входом дискретных фазовращателей 2-4. Блок 16 управле ия задает скорость изменения фазы сигналов (величину и направление). С выходов дискретных фазовращателей 2-4 сигналы частоты fp поступают на входы формирователей 7-9 частот 5 6f 9f, выходы KOTOpbix соединены с первыми входами блока 10 ключей и с входами соответствующих делителей

59

П-Ш частоты в 5,6,8 и 9 раз, которые обеспечивают приведение частот сигналов станций точной сети к одинаковой частоте If грубой сети,.являющейся их общим наибольшим делителем и служащим для устранения многозначности фазовых отсчетов на частоте If

Выходы делителей 11-Т соединены с третьими входами блока 10 ключей и входами блока 6. Сигналы с выхода блока 10 ключей через аттенюатор 15 поступают на выход устройства. Выход блока 6 соединен с третьими входами дискретных фазовращателей Z-.

Блок 1б управления (или ЭВМ) связан по выходу также с вторым входом блока 10 ключей и соответствующим входом блока 6. Блок 6 задает режим работы дискретных фазовращателей 2блока 10 ключей и блока 6, обеспечивая выдачу сигналов точной и грубой сети по заданной временной диаграмме работы радионавигационной системы и изменения фаз сигналов с соответствующими скоростями при имитации двйжения объекта.

Блок 6 анализирует текущее значение фазового рассогласования между сигналами ведущей и соответствующими ведомыми станциями с заданным значеиием этой величины, полученным с блока 16 управления; В случае неравенства этих значений блок 6 вырабатывает сигнал ошибки и ее знак, которые поступают на третий вход соответствуюего дискретного фазовращателя. Под действием этого сигнала соответствующий дискретный фазовращатель сдвигает фазу сигнала несущей частоты, чтобы эта ошибка сводилась к нулю.

Рассмотрим работу блока 6 в соответствии с представленным на фиг.2 одним из возможных вариантов его выполнения .

Сигналы с частотой U с выходов делителей частоты 1.1-I ведомых и ведущего каналов (фиг.2) поступают на блок 17 управляемых ключей. Ключи управляются соответствующими сигналами, поступающими с блока 16 управления (или от внешней ЭВМ). Выходные сигналы с управляемых ключей (сигнал ведущей станции и соответствующей ведомой станции) поступают на вход временного дискриминатора 18. На выходе временного дискриминатора 18 формируется строб, длительность которого пропорциональна текущему

в

значению фазового сдвига между сигналами ведущей и ведомыми станциями. Этот строб в качестве управляющего напряжения поступает на первый вход первого элемента И 19, где он заполняется частотой квантования f, поступающей с выхода источника 1 (фиг.2) на второй вход первого элемента И 19. Таким образом, временной интервал преобразуется в число импульсов (или код). С выхода первого элемента И 19 импульсы через первый вход первого элемента ИЛИ 20 поступают на вход счетчика 21. В счетчик 21 через третий вход первого элемента ИЛИ 20 предварительно записывается (в обратном коде) требуемое значение фазового сдвига сигнала по заданной ведомой станции относительно сигнала ведущей станции. Это значение вводится с блока 1б управления (или с внешней ЭВМ). С выхода блока 16 управления поступают также импульсы начальной установки на входы начальной установки триггеров 27 и 26 с двойным управлением.

Таким образом, в счетчике 21 записано в обратном коде требуемое значение фазового сдвига по сигналам выбранной пары станций, и триггеры 2б и 27 с двойным управлением находятся в исходном состоянии.

Рассмотрим работу блока 6 в случае, когда требуемое значение фазового сдвига равно измеренному.

С приходом сигнала управления от блока 1б управления на блок 17 управляемых ключей с них на временной дискриминатор 18 будут поступать сигналы частоты If ведущей и выбранной ведомой станции. На выходе временного дискриминатора 18 будет возникать строб, который на первом элементе И 19 будет заполнен импульсами квантования с частотой fon Эти импульсы через первый элемент ИЛИ 20 поступят в счетчик 21. Емкость счетчика выбра на исходя из требования установки максимального фазового сдвига, равного 2ii(360). На счетчике 21 произойдет суммирование предварительно записанного числа импульсов и числа импульсов измеренного временного интервала (фазового сдвига).

Если требуемое значение фазового двига равно измененному, то с втоого выхода счетчика 21 на второй ход третьего элемента И 23 будет поступать сигнал запрета, и первый триггер 26 с двойным управлением останется в исходном состоянии. Элемент И 22 по второму входу с первого выхода первого триггера 26 с двойным управлением будет иметь сигнал разрешения и в момент окончания строба фазового сдвига, сформированного временным дискриминатором 18, на его выходе образуется сигнал, который приведет второй триггер 27 с двойным управлением в состояние, про тивоположное начальному. На его выхо де будет сформировано управляющее напряжение для соответствующего дискретного фазовращателя и одновременн сигнал разрешения для пятого элемента И 25 по его первому входу. После окончания строба фазового сдвига, который поступает также на инвертор 28, на его выходе будет разрешающий сигнал для пятого элемента И 25 по его второму входу, а на третий вход поступают импульсы квантования с выхода источника 1 (фиг.1). На выходе пятого элемента И 25 появится импульс, который через второй элемент ИЛИ 29 и второй вход первого элемента ИЛИ 20 поступит в счетчик 21 и вы зовет его переполнение. С второго выхода счетчика 21 импульс переполнения поставит триггер 27 с двойным управлением по его первому входу в исходное состояние и пятый элемент И 25 по его. первому входу закроется для прохождения импульсов с выхода источника 1 опорных колебаний, Рассмотрим работу блока 6 в случае, когда истинное значение фазового сдвига превышает заданное. Как описано ранее, в счетчике 21 хранится требуемое значение фазового сдвига. Триггеры 2б и 27 находятся в исходном состоянии. С выхода временного дискриминатора 18 строб рассог ласования (фазового сдвига) на первом элементе И 19 заполнится импульсами квантования, которые через первый элемент ИЛИ 20 запишутся в счетчике 21. Поскольку истинное значение фазового сдвига превышает заданное, на выходе счетчика образуется импульс переполнения. Импульс переполнения совпадает по времени со стробом фазового сдвига на элементе М 23 и приведет триггер 26 в состояние, противоположное исходному, что будет выдано в качестве знака рассогласования для дискретного фазовращателя и перевода счетчика 21 по его второму входу в режим вычитания. Одновременно импульс переполнения с второго выхода счетчика 21 поступит на первый вход триггера 27, подтверждая его устойчивое начальное состояние. После окончания длительности строба фазового рассогласования инвертор 28 выдает разрешающий потенциал на второй вход четвертого элемента И 2. Импульсы с частотой квантования пройдут через четвертый элемент И 2k, через второй элемент ИЛИ 23 на вход соответствующего дискретного фазовращателя и вызовут смещение фазы сигнала в противоположную сторону. Одновременно эти импульсы поступят через второй вход элемента ИЛИ 20 на вход счетчика 21. В момент, когда число импульсов в счетчике будет равно нулю, на первом выходе счетчика 21 образуется импульс, которы й поставит триггер 26 в исходное состояние и его сигнал с второго запретит прохождение импульсов .квантования через четвертый элемент И 2k навход дискретного фазовращателя . Таким образом, достигается повышение точности устройства и обеспечивается возможность корректировки случайных сбоев в трактах формирователя сигналов. П|эименение изобретения позволяет более точно (iО,1 измеряемого параметра) и объективно с максимальным приближением к реальным условиям определять параметры проверяемого приемоиндикатора. Сокращается примерно в полтора раа время проверки и контроля за счет ого, что имитатор способен воссозать реальный сигнал, по которому роверка нескольких параметров прозводится одновременно. Формула изобретения 1. Устройство для имитации сигнаов радионавигационной системы, соержащее источник опорных колебаний, выход которого соединен с входом формирователя частот сигналов ведущей станции непосредственно и через дискретные фазовращатели - с входами ормирователей частот сигналов ведомых станций, вторые входы дискретных фазовращателей соединены с выходом .

99

блока управления, выходы всех формирователей частот сигналов соединены с первыми входами блока ключей, второй вход которого соединен с выходом блока управления, а выход - с входом аттенюатора, отличающееся тем, что, с целью повышения точности введен блок автоматического контроля и коррекции фаз между сигналами ведущей и ведомых станций и делители частоты, входы которых соединены С выходами соответствующих формирователей частот сигналов, а выходы с третьими входами блока ключей, первый вход блока автоматического контроля и коррекции фаз соединен с выходом источника опорных колебаний, второй третий, четвертый и пятый входы - с выходами соответствующих делителей частоты, а управляющий

вход - с выходом блока управления, выход блока автоматического контроля и коррекции фаз соединен с третьими входами дискретных фазовращателей, а выход аттенюатора является выходом устройства..

2. Устройство fio П.1 , о т л и чающееся тем, что блок автоматического контроля и коррекции фаз содержит блок управляемых ключей,

выход которого соединен с входом временного дискриминатора, выход временного дискриминатора соединен с первыми входами первого, второго и третьего элементов И и входом инвертора, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом . счетчика, первый выход которого соединен с первым входом первого триггера с двойным управлением, второй выход счетчика через третий элемент И соединен с вторым входом первого триггера с двойным управлением и с

10

10

первым входом второго триггера с двойным управлением, второй вход которого соединен с выходом второго элемента И, второй вход которого соединен с первым выходом первого триггера с двойным управлением, второй выход которого соединен с вторым входом счетчика и первым входом четвертого элемента И, выход второго триггера с двойным управлением соединен с первым входом пятого элемента И, вторые входы четвертого и пятого элементов И соединены с выходом инвертора, а третьи входы четвертого и пятого элементов И и второй вход первого элемента И объединены и являются первым входом блока автоматического контроля и коррекции фаз, выходы четвертого и пятого элементов И соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента .ИЛИ, при этом входы блока управляемых ключей являются соответственно вторым, третьим, четвертым и пятым входами блока автоматического контроля и коррекции фаз, выходом которого является выход второго элемента ИЛИ, второй выход первого триггера с двойным управлением и выход второго триггера с двойным управлением, а управлякщим входом блока автоматического контроля и коррекции фаз является третий вход первого элемента ИЛИ и объединенные вхо/ начальной уста.новки первого и второго триггеров с двойным управлением.

Источники информации, принятые во внимание при экспертизе 1. Кинкулькин И.Е. и др. Фазовый метод определения координат, М. Советское радио, 1979, с.79-82 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОНАВИГАЦИОННАЯ СИСТЕМА (БАГИС-А) | 1995 |

|

RU2097780C1 |

| Фазометрическое устройство | 1984 |

|

SU1221611A1 |

| Цифроаналоговая следящая система | 1986 |

|

SU1405025A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1121691A1 |

| КВАЗИМОНОИМПУЛЬСНЫЙ ВТОРИЧНЫЙ РАДИОЛОКАТОР | 2016 |

|

RU2622399C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Преобразователь код-угол | 1976 |

|

SU693416A1 |

| Стабилизированный вентильный электропривод с комбинированным управлением | 1987 |

|

SU1610588A1 |

| Устройство для управления ведущим шаговым двигателем | 1981 |

|

SU999022A1 |

От 0f

I

SI К АФ. fjfffffc раеcogfacoSffffl(JftOfI flOCсеглуса ам/

Авторы

Даты

1982-05-07—Публикация

1980-08-04—Подача