Изобретение касается способа и cxeNttii обработки сигнала трех уровней, используемого для передачи бинарной информации в вычислительной технике по зданиям и большим производственным объектам, особенно для передачи между ЭВМ и периферийными устройствами, находящимися на больших расстояниях от ЭВМ.

Из-вестен способ, в котором используют прямое разграничение временной последовательности комплементарных уровней сигнала трех уровней после обработки в компараторах напряжения разделением на два канала с уровнями ТТЛ и переменным блокированием указанных ветвей моностабильными схемами в зависимости от полярности первой части бита так, что импульс с точки зрения времени соответствующий второй части бита появится лишь на выходе одного кангша по логическому содержанию бита.

Недостатком устройства для реализации известного способа является нестойкость к помехам, которые могут проникать, даже к входам обоих каналов , или же могут блокировать путь положительного сигнала.

Известен также способ, в котором используют косвенное разграничение временной последовательности комплементарных уровней .сигнала трех уровней путем преобразования на простой треугольный сигнал с помощью интегратора, причем моментальная полярность таким образом полученного .сигнала соответствует очереди уровней

10 напряжения сигнгша трех уровней, т.е. также логическому содержанию , бита.

Недостатком является то, что устройство для реализации известного,

15 способа требует сигнала трех уровней с нулевым средним значением.

.Предлагается способ обработки бинарной информации, содержащейся в сигнале трех уровней, образованном

20 временной последовательностью положительных, отрицательных и нулевых уровней напряжения с определенным постоянным временем продолжения нулевых уровней, отдельные биты кото25рого созданы последовательностью положительного, отрицательного и нулевого уровней в рамках последовательности одного бита, использующего обработку сигнала трех уровней в

двух компараторах напряжения, решающие уровни которых определены источником порогового напряжения, причем в зависимости от полярности .принимаемого уровня напряжения сигнала трех уровней возникает простой импульс на выходе первого или второго компараторов напряжения, сущность которого заключается в том, что с помощью переднего фронта первого полученного таким образом импульса на выходе одного из пары компараторов напряжения запускается первая схема задержки, которая генерирует импульс с уменьшением времени, чем время импульса на выходе компаратор напряжения, соответствующего первому уровню напряжения в рамках последовательности одного бита сигнала трех уровней, а с помощью заднего фронта импульса-от первой схемы задержки реализуется первичная запись логических уровней от выходов обоих компараторов напряжения в.первзпо пару однобитных памятей при условии что состояния выходов Компараторов напряжения в момент первичной записи являются взаимно инверсионными, Причем в каждом другом случае запись не реализуется и однобитные памяти останутся в исходном положении подготовленными к приему; в случае, если запись произошла, запускается вторая схема задержки генерирующая импульс, задний фронт которого определяется ко времени появления регулярного импульса на выходе второго из пары компараторов напряжения, соответствующего уровню напряжения противоположной полярности в рамках последовательности того же бита сигнала трех уровней, и с помощью заднего фронта импульса от второй схемы задержки реализуется вторичная запись логических уровней от выходов обоих компараторов напряжения во вторую Пару однобитных памятей при условии, что состояние выхода каждого компаратора напряжения в момент вторичной записи является инверсионным по отношению к предшествующему состоянию, записанному в первой паре однобитных памятей, а в каждом другом случае запись не реализуется и все однобитные памяти проводятся в исходное положение или после Окончания импульса от второй схемы задержки, или после окончания импульса на выходе хотя бы одного компаратора напряжения, причем в случае, если запись реализована, все однобитные памяти приводятся в исходное состояние после окончания импульса на выходе второго из пары компараторов напряжения и этим самым достигается обработка информации путем получени импульса на выходе одной из второй

пары однобитных памятей по логическому содержанию принятого бита.

Изобретение обеспечивает уменьшение вероятности возникновения ошибочной обработки, которая может возникнуть на основе случайной помехи на линии передачи под влиянием использованного моделирующего принципа и логического обеспечения, подавляющего обработку неправильной последовательности полярностей напряжения сигнала трех уровней.

Для реализации способа обработки бинарной информации, содержащейся в сигнале трех уровней, служит соединение с симметрирующим элементом и двумя компараторами соответственно изобретению, сущность чего заключается в том, что выход первого компаратора напряжения соединен с Прямым входом первой логической ингибиторной схемы, а первым входом первой логической суммирующей схемы, с ингибиторным входом второй логической ингибиторной схемы и с первым входом схемы для логической функции отрицания суммы, выход второго компаратора напряжения соединен с ингибиторным входом первой логической ингибиторной схемы, со вторым входом первой логической суммирующей схемы, с прямым входом второй логической ингибиторной схемы и со вторым входом для логической функции отрицания суммы, вы5сод первой логической суммирующей схемы соединен с запускающим входом первого замедляющего элемента, выход первого элемента задержки соединен с временными входами первой и второй однобитной памяти, выход первой индикаторной логической схемы связан с входом данных первой однобитной памяти и первым входом первой логической схемы произведения, выход второй логической ингибиторной схемы связан с входом данных второй однобитной памяти и с первым входом второй логической схемы произведения, выход данных первой однобитной памяти соединен с первьлм входом второй логической суммирующей cxeivftj и со вторым входом второй логической схемы произведения, выход данных второй однобитной памяти соединен со вторым входом второй логической (однобитной памяти) суммирующей схемы и-со вторым входом первой Логической схемы произведения, выход второй логической суммирующей схемы соединен с запускающим входом второго элемента задержки, выход второго элемента задержки соединен с временными входами третьей и четвертой однобитной памяти, далее с третьим входом схемы для логической функции отрицания суммы и с блокирующим входом первого элемента задержки, выход первой логической схемы произведения соединен с выходом данных третьей однобитной памяти и выход второй логической схемы произведения соединен с входом данных четвертой однобитной памяти,выход схемы для логической функции отрицания суммы связаны с нулирующими входами всех однобитных памятей, выходы третьей и четвертой однобитных памятей являются выходами простых импульсов для обработки бинарной информации, содержащейся в сигнале трех уровней на входе симметрирующего элемента.

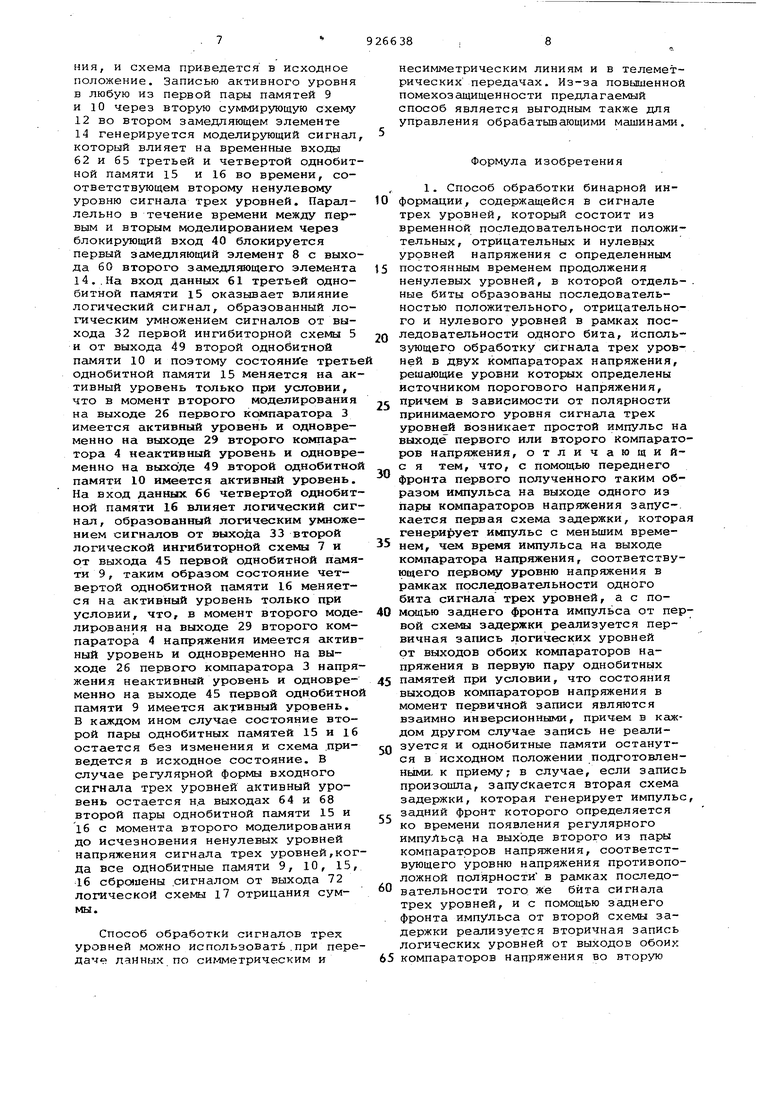

На чертеже дана блок-схема, реализующая предлагаемый способ.

Сигнал трех уровней поступает на вход 20 симметрирующего элемента 1, первцй вход которого 21 соединен с первым входом .24 первого компаратора 3 напряжения и второй выход 22 соединен с первым входом 28 второго компаратора 3 напряжения и второй вход 27 второго компаратора 4 напряжения соединен с выходом 23 источника 2 порогового напряжения. Выход 26 первого компаратора 3 напряжения соединен с прямым входом/30 первой логической ингибиторной схемы 5, с первым входом 33 первой логической суммирующей схемы 6, с ингибиторным входом 36,второй логической ингибиторной схемы 7 и с первым 71 схемы 17, которая реализует логическую функцию отрицания суммы. Выход 29 второго компаратора 4 напряжения связан с ингибиторным вхо дом 31 первой логической ингибиторной схемы 5, со вторым входом 34 первой логической суммирующей схемы 6,, с прямым входом 37 второй ингибиторной схемы 7 и со вторым входом 70 схемы 17, которая реализует логическую функцию отрицания суммы, выход 35 первой логической суммир щей схемы 6 соединен с запуск.ающим входом 39. первого замедляющим элементом 8, выход 41 первой схемы 8 задержки соединен с задним фронтом через реагирующие часовые входы 43 и 46 первой и второй однобитной памяти 9 и 10, выход 32 первой ингибиторной схемы 5 связан со входом данных 42 первой однобитной памят/тл 9 и с первым входом 50 первой логической 11 схемы произведения, выход 38 второй логической ингибиторной схемы 7 связан со входом данных 47 второй однобитной памяти 10 и с первым входом 57 второй логической схемы 13 произведения. Выход данных 45 первой однобитной памяти 9 связан с первым входом 53 второй логической суммирующей схемы 12 и со вторым входом 56 второй логической схемы 13 произведения. Выход данных

49 второй однобитной памяти 10 соединен со вторым входом 54 второй логической суммирующей схемы 12 и со вторым входом 51 первой логической схемы 11 произведения, выход 55 5 второй логической суммирующей схемы 12 связан с запускающим входом 59 второго элемента 14 задержки. Выход 60 второго элемента 14 задержки соединен с задним фронтом через реагирующие часовые входы 62 и 65 третьей и четвертой однобитной памяти 15 и 16, Далее с третьим входом 69 схемы 17, которая реализует отрицание суммы и с блокирующим входом 40 первого элемента 8 задержки, выход 5J2 первой логической схемы 11 произведения связан со входом данных 61 третьей однобитной памяти. 15 и выход 58 второй логической схемы 13 произведения связан со входом данных 66 четвертой однобитной памяти 16. Выход 72 cxeNSJ 17, которая реализует отрицанием суммы соединен с нулирую14ИМИ входами 44, 48, 63, 67 всех

5 однобитных памятей 9, 10, 15, 16. Выходы 64 и 68 третьей и четвертой однобитной памяти15 и 16 являются выходами, с которых принимается обработанная бинарная информация.

« В примере подключения симметрирующий элемент 1 разделяет входной сигнал трех уровней на два комплементарные сигнала, моментальный уровень напряжения которых сравнивается в компараторах 3 и 4 с напряжением, поступающим от источника 2 порогового напряжения. На выходах

26 и 29 компар.аторов 3 .и 4 в случае, если соответствующий входной сигнал превышает значение порогового напряжения, то появляется бинарный сигнал в виде простого импульса.

Первым таким образом, полученным бинарным сигналом через первую суммирующую схему 6 в- первом замедляющем элементе 8 генерируется моделирующий сигнал, который влияет на временные входы 43 и 46 первой и второй однобитной памяти 9 и 10 во

Q время, соответствующее первому ненулевому уровню сигнала трех уровней. Входы данных 42 и 47 первой и второй однобитной памяти 9 и 10 от выходов 26 и 29 первого и второго компаратора 3 и 4 напряжения отделены Первым и вторым- ингибиторным элементом 5 и 7, которые обеспечивают запись состояния выходов 26 и 29 в первую и вторую однобитную память 9 и Ю лишь при условии,

0 что в момент моделирования логические уровни, находящиеся на выходах 26 и 29 компараторов 3 и 4 взаимно инверсионны. В каждом ином случае состояние первой пары однобитных

65 памятей 9 и 10 остается без изменеяия, и схема приведется в исходное положение. Записью активного уровня в любую из первой пары памятей 9 и Ю через вторую суммирующую схему 12 во втором замедляющем элементе 14 генерируется моделирующий сигнал который влияет на временные входы 62 и 65 третьей и четвертой однобит ной памяти 15 и 16 во времени, соответствующем второму ненулевому уровню сигнала трех уровней. Параллельно в течение времени между первым и вторым моделированием через блокирующий вход 40 блокируется первый замедляющий элемент 8 с выхо да 60 второго замедляющего элемента 14..На вход данных 61 третьей однобитной памяти 15 оказывает влияние логический сигнал, образованный логаческим умножением сигналов от выхода 32 первой ингибиторной схемы 5 и от выхода 49 второй однобитной памяти 10 и поэтому состояние треть однобитной памяти 15 меняется на ак тивный уровень только при условии, что в момент второго иоделирования на выходе 26 первого компаратора 3 имеется активный уровень и одновременно на выходе 29 второго компаратора 4 неактивный уровень и одновре менно на выходе 49 второй однобитно памяти 10 имеется активный уровень. На вход данных 66 четвертой однобит ной памяти 16 влияет логический сиг нал, образованный логическим умноже нием сигналов от выхода 33 второй логической ингибиторной схемы 7 и от выхода 45 первой однобитной памя ти 9 , таким образом состояние четвертой однобитной памяти 16 меняется на активный уровень только при условии, что, в момент второго моде лирования на выходе 29 второго компаратора 4 напряжения имеется актив ный уровень и одновременно на выходе 26 первого компаратора 3 напря жения неактивный уровень и одновременно на выходе 45 первой однобитно памяти 9 имеется активный уровень. В каждом ином случае состояние второй пары однобитных памятей 15 и 16 остается без изменения и схема .приведется в исходное состояние. В случае регулярной формы входного сигнала трех уровней активный уровень остается н.а выходах 64 и 68 второй пары однобитной памяти 15 и 16 с момента второго моделирования до исчезновения ненулевых уровней напряжения сигнала трех уровней,ког да все однобитные памяти 9, Ю, 15, 16 сброшены .сигналом от выхода 72 логической схемы 17 отрицания суммы. Способ обработки сигналов трех уровней можно использовать.при пере даче данных по сиглметрическим и несимметрическим линиям и в телеметрических передачах. Из-за повышенной помехозащищенности предлагаемый способ является выгодным также для управления обрабатывающими машинами. Формула изобретения 1. Способ обработки бинарной информации, содержащейся в сигнале трех уровней, который состоит из временной последовательности положительных, отрицательных и нулевых уровней напряжения с определенным постоянным временем продолжения ненулевых уровней, в которой отдель- . ные биты образованы последовательностью положительного, отрицательного и нулевого уровней в рамках последовательности одного бита, использующего обработку сигнала трех уровней в д,эух компараторах напряжения, решающие уровни которых определены Источником порогового напряжения, причем в зависимости от полярности принимаемого уровня сигнала трех уровней возникает простой импульс на выходе первого или второго компараторов Напряжения, отличающийс я тем, что, с помощью переднего фронта первого полученного таким образом импульса на выходе одного из пары компараторов напряжения запускается первая схема задержки, которая генерирует импульс с меньшим временем, чем время импульса на выходе компаратора напряжения, соответствующего первому уровню напряжения в рамках последовательности одного бита сигнала трех уровней, а с помощью заднего фронта импульса от первой схемы задержки реализуется первичная запись логических уровней от выходов обоих компараторов напряжения в первую пару однобитных памятей при условии, что состояния выходов компараторов напряжения в момент первичной записи являются взаимно инверсионными, причем в каждом другом случае запись не реализуется и однобитные памяти останутся в исходном положении подготовленными, к приему; в случае, если запись произошла, запускается вторая схема задержки, которая генерирует импульс, задний фронт которого определяется ко времени появления регулярного импульсу На выходе второго из пары компараторов напряжения, соответствующего уровню напряжения противоположной полярности в рамках последовательности того же бита сигнала трех уровней, и с помощью заднего фронта импульса от второй схемы задержки реализуется вторичная запись логических уровней от выходов обоих компараторов напряжения во вторую

пару однобитных памятей при условии, что состояние выхода каждого компаратора напряжения в момент вторичной записиявляется инверсионным по отношению к предшествующему состоянию, записанному в первой паре однобитных памятей, а в каждом другом случае запись Не реализуется и все однобитные памяти приво цятся в .исходное положение или после окончания импульса от второй схемы задержки, или, после окончания импульса на выходе хотя бы одного компаратора напряжения, причем в случае, если запись была реализована, все однобитные памяти приводятся в исходное положание после окончания импульса на выходе второго из пары компараторов напряжения и этим самым достигается обработка информации путем получения простого импульса на выходе одной из второй пары однобитных памятей по логическому содержанию принятого бита.

2. Схема для осуществления способа по п. 1с cимгv eтpиpyющим элементом и. двумя компараторами, отличающаяся тем, что выход 26 первого компаратора напряжения 3 cog единен с прякЬ&г входом 30 первой логической ингибиторной схеша 5, с первым входом 33 первой логической суммирующей схемы 6, с ингибиторным входом 36.второй логической ингибиторной схемы 7 и с первым входом 71 схемы 17 для логической функции отрицания суммы, выход 29второго компаратора напряжения 4 соединен с ингибиторным входом 31 первой логической, ингибиторной схемы 5, со вторым входом 34 перво-й логической суммирующей схемы 6, с прямым входом 37 второй логической ингибиторной схемы 7 и со вторым входом 70 схемы 17 для логической функции отрицания суммы, выход 35 первой логической . суммируквдей схеглы 6 соединен с запускающим входом 39 первого элемента задержки 8, выход 41 первого элемента задержки 8, соединен с часовыми входами 43- и 46 первой и второй однобитной памяти 9 и 10 выход 32 первой ингибиторной логической схемы 5 связан с входом данных 42 первой однобитной памяти 9 и с первым входом 50 первой логической схемы произведения 11, выход 38 второй логической ингибиторной схемы 7 соединен с входом данных 47 второй однобитной памяти 10 и с первым входом 57 второй логической схемы произведения 13, выход данных 45 первой однобитной памяти 9 соединен с первьм входом 53 второй логической суммирующей схемы 12 и со вторым входом 56 второй логической схемы произведения 13, выход данных 49 второй однобитной памяти 10 соединен со вторым входом 54 второй логической суммирующей схемы 12 и со вторым входом 51 первой логической схемы произведения 41, выход 55 второй логической суммирующей схемы 12 соединен с запускающим входом 59 второго элемента задержки 14, выход 60 второго элемента задержки 14 связан с часовыми входами 62 и 65 третьей и четвертой однобитной памяти 15 и 16 далее с третьим входом 69 схемы 17 для логческой функции отрицания суммы и с блокирующим входом 40 первого элемента задержки 8, выход 52 первой-логической схемы произведения 11 соединен с выходом данных 61 третьей однобитной памяти 15 и выход 58 второй логической схемы произведения 13 соединен с входом данных 66 четвертой (функции отрицания ) однобитной памяти 16, выход 72 17 для логической Функции отрицания суммы связан с нулирующим входами всех однобитных памятей, вьсходы 64 и 68 третьей и четвертой однобитных памятей 15 и 16 являются выходагли простых импульсов для обработки бинаной информации, которая содержится в сигнале трех уровней на входе 20 симметрирующие го элемента 1.

Признано изобретением по результатам экспертизы, осуществленной Ведомством по изобретательству Чехословацкой Социсшистической Республики.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРИЕМА ДВОИЧНЫХ ФАЗОМАНИПУЛИРОВАННЫХ НА 180 ГРАДУСОВ СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2146078C1 |

| ПРИЕМНИК СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1997 |

|

RU2118054C1 |

| Генератор программ для управляемого синтаксического контроля | 1989 |

|

SU1672467A1 |

| Низкоскоростной дельта-модулятор | 1984 |

|

SU1203706A1 |

| Устройство группового программного управления технологическими процессами | 1989 |

|

SU1663603A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Устройство для регистрации сейсмических сигналов | 1989 |

|

SU1681288A1 |

| Устройство для передачи бинарной информации | 1988 |

|

SU1757117A1 |

| ПРОЦЕССОРЫ, СПОСОБЫ, СИСТЕМЫ И КОМАНДЫ ДЛЯ СЛОЖЕНИЯ ТРЕХ ОПЕРАНДОВ-ИСТОЧНИКОВ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 2014 |

|

RU2656730C2 |

| СПОСОБ РАДИОПЕРЕДАЧИ И РАДИОПРИЕМА ПОТОКА ЦИФРОВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2101862C1 |

Авторы

Даты

1982-05-07—Публикация

1980-03-18—Подача