Изобретение относится к автоматике и вычислительной технике и предназначено для управления робототехнологическим оборудованием в автоматических линиях.

Цель изобретения - обеспечение независимого управления группой асинхронных технологических процессов в режиме разделенного времени.

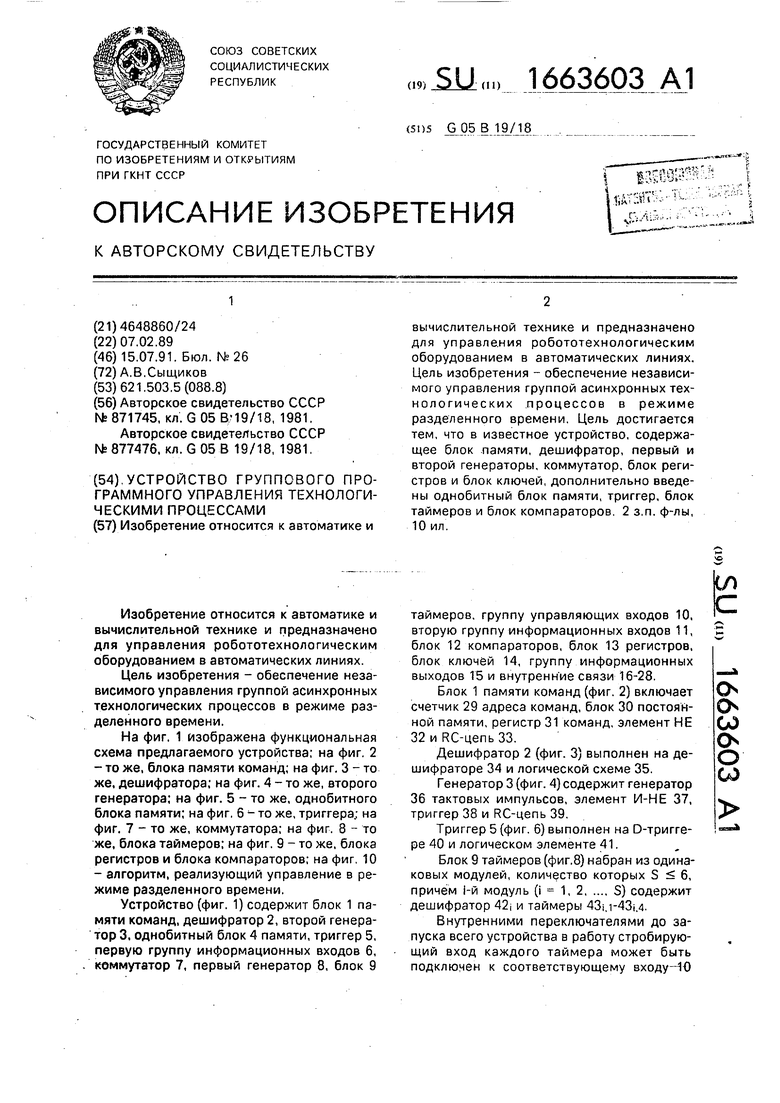

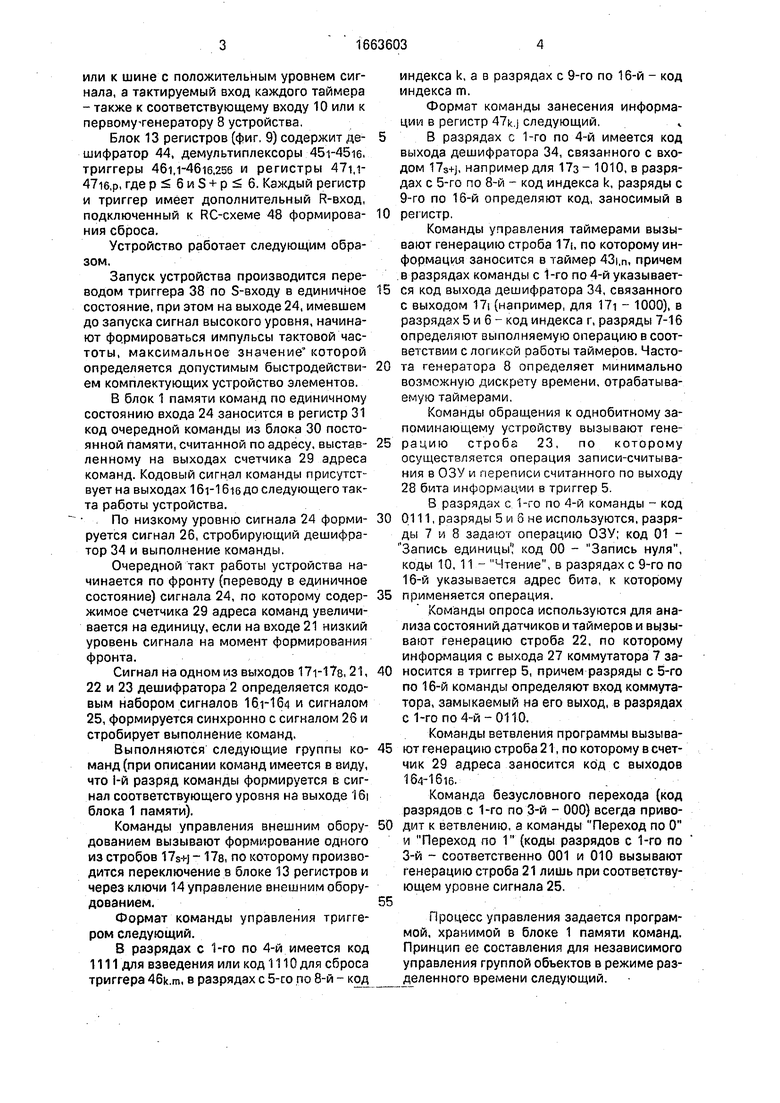

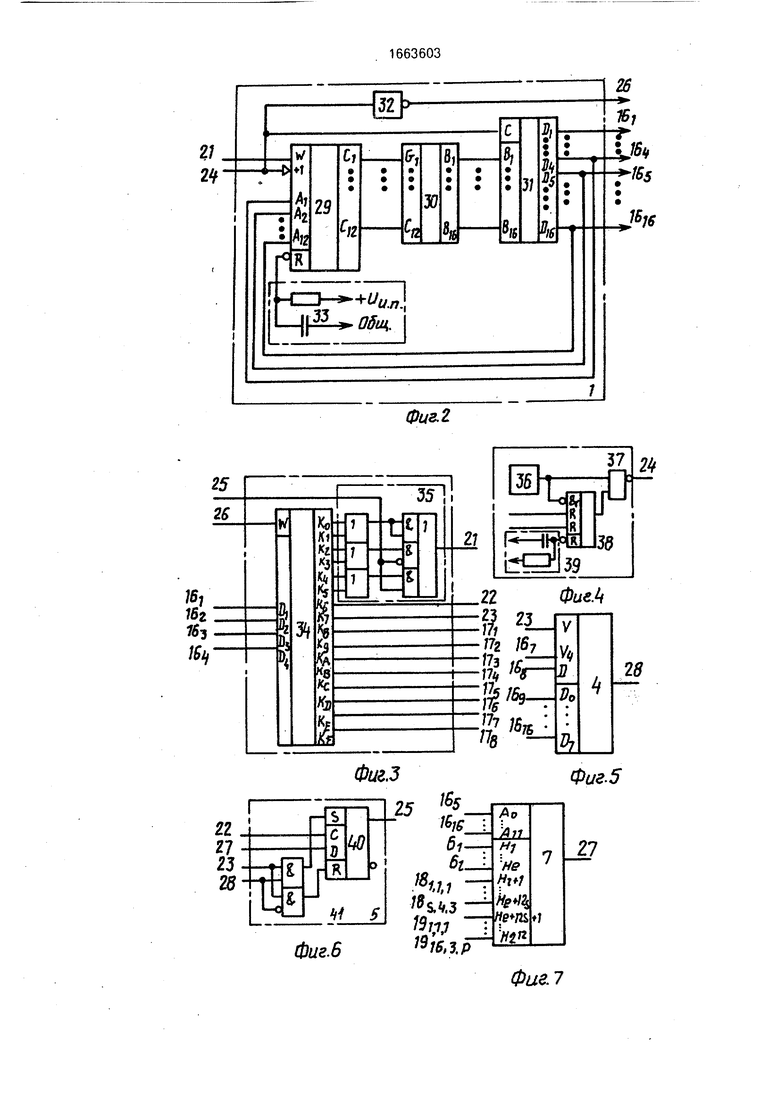

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2

-то же, блока памяти команд; на фиг. 3 - то же, дешифратора; на фиг. 4 - то же, второго генератора; на фиг. 5 - то же, однобитного блока памяти; на фиг. 6 - то же, триггера; на фиг. 7 - то же, коммутатора; на фиг. 8 - то же, блока таймеров; на фиг. 9 - то же, блока регистров и блока компараторов; на фиг 10

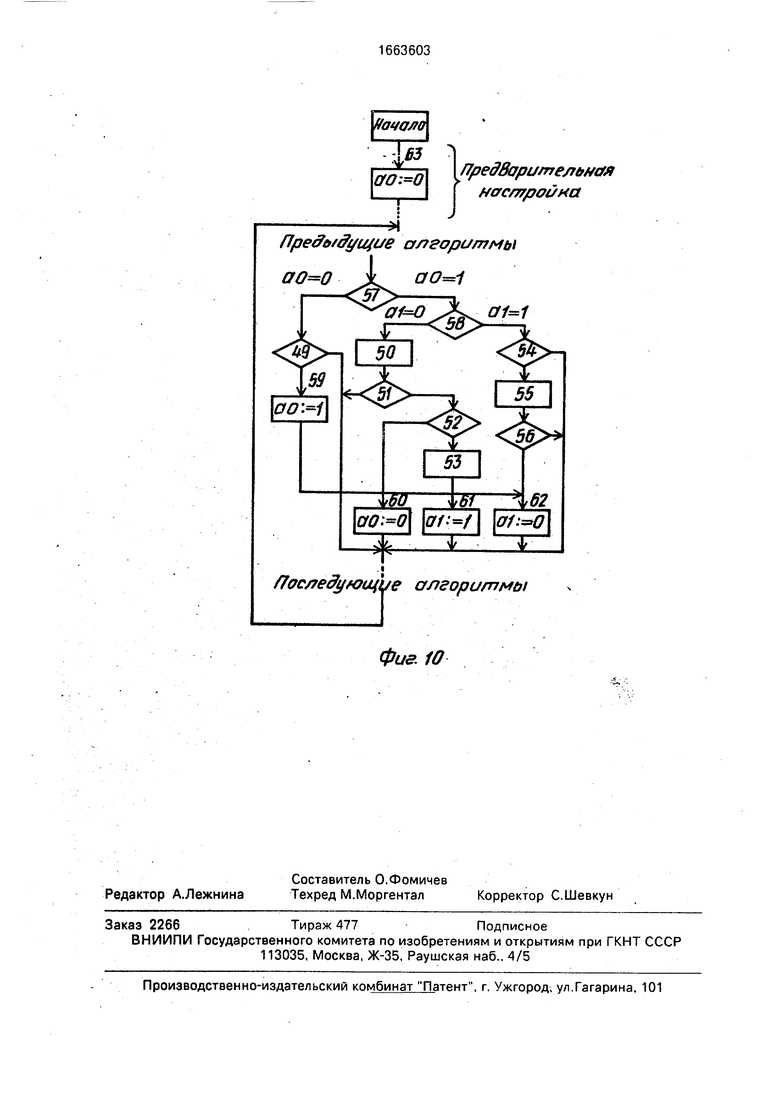

-алгоритм, реализующий управление в режиме разделенного времени.

Устройство (фиг. 1) содержит блок 1 памяти команд, дешифратор 2, второй генератор 3. однобитный блок 4 памяти, триггер 5, первую группу информационных входов 6, коммутатор 7, первый генератор 8, блок 9

таймеров, группу управляющих входов 10, вторую группу информационных входов 11, блок 12 компараторов, блок 13 регистров, блок ключей 14, группу информационных выходов 15 и внутренние связи 16-28.

Блок 1 памяти команд (фиг. 2) включает счетчик 29 адреса команд, блок 30 постоянной памяти, регистр 31 команд, элемент НЕ 32 и RC-цепь 33.

Дешифратор 2 (фиг. 3) выполнен на дешифраторе 34 и логической схеме 35.

Генератор 3 (фиг. 4) содержит генератор 36 тактовых импульсов, элемент И-НЕ 37, триггер 38 и RC-цепь 39.

Триггер 5 (фиг. 6) выполнен на D-тригге- ре 40 и логическом элементе 41.

Блок 9 таймеров (фиг.8) набран из одинаковых модулей, количество которых S 6,

причем 1-й модуль (i 1,2 S) содержит

дешифратор 42, и таймеры 43,,i-43i.4

Внутренними переключателями до запуска всего устройства в работу стробирую- щий вход каждого таймера может быть подключен к соответствующему входу-10

DS

о

СА) О О Ы

или к шине с положительным уровнем сигнала, а тактируемый вход каждого таймера - также к соответствующему входу 10 или к первомутенератору 8 устройства.

Блок 13 регистров (фиг. 9) содержит дешифратор 44, демультиплексоры 45t-45i6, триггеры 46i,1-4616,256 и регистры 47i,i- 47ie,p, где + . Каждый регистр и триггер имеет дополнительный R-вход, подключенный к RC-схеме 48 формирования сброса.

Устройство работает следующим образом,

Запуск устройства производится переводом триггера 38 по S-входу в единичное состояние, при этом на выходе 24, имевшем до запуска сигнал высокого уровня, начинают формироваться импульсы тактовой частоты, максимальное значение которой определяется допустимым быстродействием комплектующих устройство элементов.

В блок 1 памяти команд по единичному состоянию входа 24 заносится в регистр 31 код очередной команды из блока 30 постоянной памяти, считанной по адресу, выставленному на выходах счетчика 29 адреса команд. Кодовый сигнал команды присутствует на выходах 16Н 6ie до следующего такта работы устройства.

По низкому уровню сигнала 24 формируется сигнал 26, стробирующий дешифратор 34 и выполнение команды.

Очередной такт работы устройства начинается по фронту (переводу в единичное состояние) сигнала 24, по которому содержимое счетчика 29 адреса команд увеличивается на единицу, если на входе 21 низкий уровень сигнала на момент формирования фронта.

Сигнал на одном из выходов 17i-1 8,21, 22 и 23 дешифратора 2 определяется кодовым набором сигналов 16г1б4 и сигналом 25, формируется синхронно с сигналом 26 и стробирует выполнение команд.

Выполняются следующие группы команд (при описании команд имеется в виду, что 1-й разряд команды формируется в сигнал соответствующего уровня на выходе 16| блока 1 памяти).

Команды управления внешним оборудованием вызывают формирование одного из стробов 17s+j- 17s, по которому производится переключение в блоке 13 регистров и через ключи 14 управление внешним оборудованием.

Формат команды управления триггером следующий.

8 разрядах с 1-го по 4-й имеется код 1111 для взведения или код 1110 для сброса триггера 46k.m, в разрядах с 5-со по 8-й - код

индекса к, а в разрядах с 9-го по 16-й - код индекса т.

Формат команды занесения информации в регистр 47k.j следующий.,.

В разрядах с 1-го по 4-й имеется код

выхода дешифратора 34, связанного с входом 17s+j, например для 17з 1010, в разрядах с 5-го по 8-й - код индекса k, разряды с 9-го по 16-й определяют код, заносимый в

регистр.

Команды управления таймерами вызывают генерацию строба 17|, по которому информация заносится в таймер 43|,п, причем в разрядах команды с 1-го по 4-й указывается код выхода дешифратора 34, связанного с выходом 17j (например, для 17i - 1000), в разрядах 5 и 6 - код индекса г, разряды 7-16 определяют выполняемую операцию в соответствии с логикой работы таймеров. Частота генератора 8 определяет минимально возможную дискрету времени, отрабатываемую таймерами.

Команды обращения к однобитному запоминающему устройству вызывают генерацию строба 23, по которому осуществляется операция записи-считывания в ОЗУ и переписи считанного по выходу 28 бита информации в триггер 5.

В разрядах с 1-го по 4-й команды - код

0111, разряды 5 и б не используются, разряды 7 и 8 задают операцию ОЗУ; код 01 - Запись единицы ,1 код 00 - Запись нуля, коды 10, 11 - Чтение, в разрядах с 9-го по 16-й указывается адрес бита, к которому

применяется операция.

Команды опроса используются для анализа состояний датчиков и таймеров и вызывают генерацию строба 22, по которому информация с выхода 27 коммутатора 7 заносится в триггер 5, причем разряды с 5-го по 16-й команды определяют вход коммутатора, замыкаемый на его выход, в разрядах с 1-го по 4-й-0110.

Команды ветвления программы вызывают генерацию строба 21, по которому в счетчик 29 адреса заносится код с выходов

164-1616.

Команда безусловного перехода (код разрядов с 1-го по 3-й - 000) всегда приво- дит к ветвлению, а команды Переход по О и Переход по 1 (коды разрядов с 1-го по 3-й - соответственно 001 и 010 вызывают генерацию строба 21 лишь при соответствующем уровне сигнала 25.

Процесс управления задается программой, хранимой в блоке 1 памяти команд. Принцип ее составления для независимого управления группой объектов в режиме разделенного времени следующий.

Исходные алгоритмы управления каждым объектом преобразуются в рабочие, которые основываются на поэтапной реализации отдельных фрагментов исходного. Если в исходном алгоритме происходит ожидание завершения очередной операции для перехода к выполнению следующей, то в рабочем при незавершении очередной операции управление передается алгоритму, реализующему процесс управления другим объектом, что и обеспечивает параллельность управления процессами в режиме разделенного времени.

Такая организация рабочего алгоритма предполагает при входе в него выполнение блока операторов поиска точки входа в алгоритм, т.е. Оператора, с которого алгоритм должен быть продолжен. Для указания точки входа используется ряд двоичных переменных, хранимых в однобитном блоке 4 памяти. После выполнения анализа состояния этих переменных по так называемому дереву поиска управление передается ветви алгоритма, по которой были не завершены определенные действия.

Если же анализ внешних сигналов показывает, что завершены все заданные в выполняемой ветви действия, то осуществляется изменение кодового набора двоичных переменных дерева поиска, что при очередном входе в алгоритм приводит к передаче управления следующей его ветви.

Например, необходимо преобразовать следующий алгоритм (управления объектом) для включения его в группу алгоритмов, реализующих процесс управления оборудованием в режиме разделенного времени (рядом проставлены номера блоков соответствующего преобразованного алгоритма).

Блок 49. Если нажата кнопка Пуск, начать управление,

БлокбО. Движение механизма вверх (ограничено упором).

Блок 51. Если движение вверх завершено, продолжить выполнение алгоритма.

Блок 52. Если нажата кнопка Стоп, перейти к блоку 49.

Блок 53. Запустить таймер на время Т,

Блок 54. Если таймер отработал время Т, продолжить выполнение алгоритма.

Блок 55. Движение механизма вниз.

Блок 56. Если движение вниз завершено, перейти к блоку 50.

В исходном алгоритме блоки 49, 51. 52, 54 и 56 приводят к зацикливанию внутри алгоритма. В рабочем алгоритме эти блоки (фиг. 10) размыкаются на передачу управления следующему алгоритму. При этом вводятся дополнительные блоки 57 и 58, образующие дерево поиска точки входа, в которых анализируются вспомогательные переменные аО и а1, и блоки 59, 60, 61 и 62,

присваивающие новые значения этим переменным. Блок 63, присваивающий переменной аО первоначальное значение, вынесен в группу блоков предварительной настройки. Таким образом может быть составлен

0 алгоритм, а следовательно, и реализующая его программа управления группой процессов, имеющих дискретный характер, либо поддающихся дискретизации путем квантования управления по времени.

5Кроме того, возможна модификация алгоритмов управления как по внешним сигналам, так и по внутренним состояниям, т.е. возможно адаптивное управление объектами.

0 Формула изобретения

1. Устройство группового программного управления технологическими процессами, содержащее первый и второй генераторы импульсов, блок памяти команд, управляю5 щий выход которого соединен с первым раз- решающим входом дешифратора, информационные выходы которого соединены с первой группой информационных входов блока регистров, группа информаци0 онных выходов старших разрядов блока памяти команд соединена с второй группой информационных входов блока регистров и адресными входами коммутатора, а младших разрядов - с группой информационных

5 входов дешифратора, выходы блока регистров соединены с входами блока ключей, выходы которых являются выходами внешнего управления устройства, отличающее- с я тем, что, с целью обеспечения независи0 мого управления группой асинхронных технологических процессов в режиме разделенного времени, в устройство введены однобитный блок памяти, блок таймеров и триггер, информационный вход которого

5 соединен с информационным выходом коммутатора, а выход триггера - с вторым разрешающим входом дешифратора, первый управляющий выход дешифратора соединен с разрешающим входом блока гамяти

0 команд, группа информационных выходов старших разрядов которого соединена с информационными и адресными входами однобитного блока памяти, выход которого соединен с первым управляющим входом

5 триггера, второй и третий управляющие выходы дешифратора соединены соответственно с вторым и третьим управляющими входами триггера, третий управляющий выход дешифратора соединен с разрешающим входом однобитного блока памяти,

выход второго генератора импульсов соединен с синхровходом блока памяти команд, информационные выходы дешифратора соединены с группой разрешающих входов блока таймеров, выходы которого соединены с второй группой информационных входов коммутатора, первая группа информационных входов которого является первой группой информационных входов устройства, группа информационных выходов старших разрядов блока памяти команд соединена с группой информационных входов блока таймеров, синхровход которого соединен с выходом первого генератора импульсов.

0

5

2.Устройство по п. 1,отличающее- с я тем, что содержит блок управляемых таймеров, группа управляющих входов которого является группой управляющих входов устройства.

3.Устройство поп, 1,отличающее- с я тем, что содержит блок компараторов, выходы которого соединены с третьей группой информационных входов коммутатора, выходы блока регистров соединены с первой группой информационных входов блока компараторов, вторая группа информационных входов которого является второй группой информационных входов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый логический контроллер | 1984 |

|

SU1497616A1 |

| Центральный процессор | 1980 |

|

SU890400A1 |

| Устройство для подготовки данных | 1988 |

|

SU1617429A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267413A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для управления робототехнологическим оборудованием в автоматических линиях. Цель изобретения - обеспечение независимого управления группой асинхронных технологических процессов в режиме разделенного времени. Цель достигается тем, что в устройство, содержащее блок памяти, дешифратор, первый и второй генераторы, коммутатор, блок регистров и блок ключей, дополнительно введены однобитный блок памяти, триггер, блок таймеров и блок компараторов. 2 з.п. ф-лы, 10 ил.

Фиг.1

21 24

16, 16г э

16if

Фиг. 2

Фиг.З

Фиг.5

Фие.7

Фиг. в

7fc

w

V

: 17.

br

Йс/г

U7 .t

Низ

&u

SsJJ

AJ В

%

Sll/

«

гН

flpefo/tfyuji/e алгоритмы

ОО

«

Яосяедующие алгоритмы

С

ачало

/7ред8ари/гте/тьнсгя насгяройна

| jL . ФФ

фиг. 10

| Устройство для программного управления группой станков | 1970 |

|

SU871745A3 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления технологическими процессами | 1979 |

|

SU877476A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-07-15—Публикация

1989-02-07—Подача