1

Изобрете}ше относится к устройствам контроля схем обработки дискретной информации, в частности к схемам контроля сумматороввычитателей электронных щфровых вычислительных машин.

Известны схемы контроля сумматоров, применяемые в цифровых ЭВМ и спецвычислителях, позволяющие повысить достоверность переработки двоичной информации 1. ,.

Наиболее близким по технической сущности к предлагаемому является сумматор с функциональной зависимостью суммы и переноса, содержащий логические элементы И, ИЛИ, схему сравнения 2.

Недостатком этих устройств является недостаточно высокая достоверность результатов контроля в процессе обработки информации.

Цель изобретения - повышение достоверности контроля.

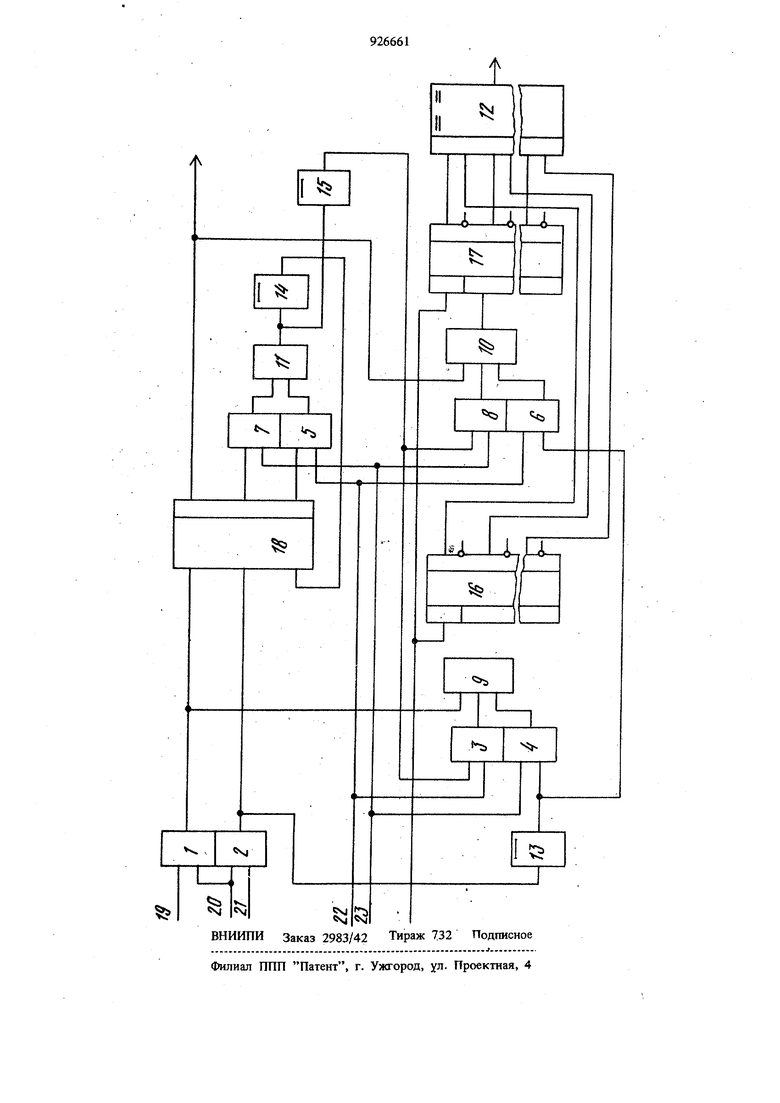

Эта цель достигается тем, что в устройство для контроля сумматора вычитателя последовательного действия, содержащее элементы И, элементы ИЛИ, схему сравнения, причем первые входы первого и второго элементов И являются информационньтми входами устройства, вторые входы являются синхршшзирующими входами устройства, выходы подалючены к входам слагаемых контролируемого сумматора-вычитателя соответственно, причем выход первого элемента И подключен к первому входу первого элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами третьего и четвертого эле10ментов И, первые входы которых являются входами управления сложением и вычитанием устройства и подключены соответственно к первым входам пятого и шестого элементов И и седьмого и восьмого элементов И, вы15ход суммы контролируемого сумматора-вычитателя подключен к первому входу второго элемента ИЛИ, выходы заема и переноса подключены к вторым входам -соответственно пятого и седьмого элементов И, выходы ко20торых соединены с входами третьего элемента ИЛИ, выходы шестого и восьмого элементов И соединены с входами второго элемента ИЛИ, введены два счетчика, три элемента эа3Д(;ржки, причем вход первого элемента задер ки соединен с выходом втсфого элемента И 2, а выход - с вторыми входами четвертого и шестого элементов И, первые входы счетчиков являются входом сброса устройства, счетный вход первого счетчика соединен с выходом первого элемента ИЛИ, а выходы подключены к первой группе входов схемы сравнения, выход второго элемента ИЛИ подключен к счетному входу второго счетчика, выходы которого подключены к второй группе входов схемы сравнения, выход которой является выходом ошибки устройства, вход . переноса контролируемого сумматора-вычитателя соединен с выходом второго элемента задержки, вход которого подключен к выходу третьего элемента ИЛИ и к входу третье элемента задержки, выход которого подключен к вторым входам третьего и седьмого элементов И. На чертеже представлена функциональная схема контроля сумматора-вычйтателя. Схема содержит логические элементы И 1-8, логические элементы ИЛИ 9-11, схему 12 сравнения, элементы задержки 13, 14 и 15, счетчики 16 и 17, сумматор-вычитатель 18, информационные шины 19 и 21 шину 20 синхронизации, управляющие шины 22 и 23 сложеьшя и вычитания. Общий принцип работы схемы контроля основан на том, что по завершении операции сложения суммарное количество единиц в слагаемых и суммарное количество единиц в сумме и возникающих переносах будет одинаково, т.е. No + N6 NC + ND где NO, Nb - количество единиц в слагаемом А и В; NC и NH - количество единиц в сумме и переносах соответственно. Соотношение (1) легко доказывается таблицей истинности, составленной для двух одн разрядных чисел. Переносы Слагаемые По завершении операции вычитания конт роль выполняется в соответствии с выраже-. нием (2), при этом предполагается, что вычитается из одного числа меньишеили равное по модулю другое число. Na - NI N6 -f NP, где NP и Nj - количество единиц в раз)ости и займах соответственно. Схема контроля при выполнении сложения работает следующим образом. Слагаемые А и В по входам 19 и 21 элементов И 1 и 2 синхронизируемые сигналом 20, подаются на входы сумматора-вычйтателя 18. В то же время слагаемое А с выхода элемента И 1 подается на вход элемента ИЛИ 9 и с его выхода на вход счетчика 16. Второе слагаемое с выхода элемента И 2 подается на вход элемента 13 задержки и с его выхода 30 на вход элемента И 6 на вход которого по шине 23 поступает сигнал Сложение. С выхода элемента И 4 второе слагаемое поступает на вход элемента ИЛИ 9 и с его выхода на вход счетчика 16. Таким образом, на счетчике 16 фиксируется суммарное количество единиц слагаемых в соответствии с левой частью выражения (1). Сумма с выхода сумматора 18 подается на вход элемента 10 ИЛИ и с его выхода на вход счетчика 17. Перенос с выхода элемента ИЛИ II подается на вход элемента 15 задержки и с ее выхода на вход элемента И 8 управляемого по входу сигналом Сложение, поступающим по шине 23. Выход элемента И 8 соединен с входом элемента ИЛИ 10, выход которого подан на вход счетчика 17. Таким образом, на счетчике 17 фиксируется суммарное количество единиц в сумме и переносах в соот- . ветствии с правой частью выражения (1). С выходов счетчиков 16 и 17 сигналы подаются на схему 12 сравнения, обеспечивающую проверку выполнения соотношения (1). Схема контроля при выполнении вычитания работает следующим образом. Уменьшаемое А и вычитаемое В аналогично слагаемым через элементы И 1 и И 2 подаются на входы сумматора-вычйтателя. Уменьшаемое А точно также как и слагаемое А подается на вход счетчика 16. На вход этого же счетчика подается сигнал займа через элемент И 3 по его входу при наличии на входе управляющего сигнала Вычитание, поступающего по шине 22. Таким образом, и:, счетчике 16 фиксируется суммарное количест во единиц в первом слагаемом и единиц эай мов. Разность точно так. же как и при ело жении с выхода сумматора-вычитатепя 18 поступает на вход счётчика 17,апычитаемое с выхода элемента 13 -задержки через вход лтсмёнта И 6 управляемого сигналом Вычитание по входу поступает на выход и далее на вход элемента ИЛИ 10. Таким обра зом, на счетчике 17 фиксируется суммарное количество единиц вычитаемого и разности в соответствии с правой частью выражения (2). Функция схемы 12 сравнения в этом сл чае сводится к проверке выполнения соотнош ния (2). Элементы 13 и 15 задержки осуществляют задержку на полтакта, обеспечива йодачу на входы счетчиков 16 и 17 сигналов слагаемых, суммы и переносов. Сшиал на выходе схемы 12 сравнения появляется в случае невыполнения соотношения (1) или (2) и используется как сигнал ошибки, при выполнении указанных соотношений сигнал ошибки не выдается. Формула изобретения Устройство для контроля сумматора-вычитателя последовательного действия, содержащее элементы И, элементы ИЛИ, схему срав нения, причем перв1 1е входы первого и второго элементов И являются информационнь ми входами устройства, вторые входы являются синхронизируюшими. входами устройства, выходы подключены к входам слагаемых контролируемого сумматора-вычитатепя соответственно, причем выход первого элеме та И подключен к первому входу первого элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами третьего и четвертого элементов И, первые входы которых являются входами )гправлени сложением и вычитанием устройства и подключены соответственно к первым входам пятого и шестого элементов И и седьмого и восьмого элементов И, выход суммы контролируемого сумматора-вычитателя подключен к первому входу второго элемента ИЛИ, выходы заема и переноса подключены к вторым входам соответственно пятого и седьмого элементов И, выходы которых соединены с входами третьего элемента ИЛИ, выходы , шестого и восьмого элементов И соединены с входами второго элемента ИЛИ, отличающееся тем, что, с целью повышения достоверности контроля, в него введены два счетчика, три элемента задержки, причем вход первого элемента задержки соединен с выходом второго элемента И 2, а выход - с вторыми входами четвертого и шестого элементов И, первые входы счетчиков яв.Г1Яются входом сброса устройства, счётный вход первого счетчика соединен с выходом первого элемента ИЛИ, а выходы подключены к первой группе входов схемы сравнения, выход второго элемента ИЛИ гюдключен к счетному входу второго счетчика, выходы которого подключены к второй группе входов схемы сравнения, выход которой является выходом ошибки устройства, вход переноса контродшруемого сумматора-вычитателя соединен с выходом второго элемента задержки, вход которого подключен к выходу третьего элемента ИЛИ и к входу третьего элемента задержки, выход которого подключен к вторым входам третьего и седьмого элементов И.. Источники информаи и, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 684545, кл. G 06 F 11/00, 1977. 2.Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ. М., 1972, с. 127-130 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательного сумматора-вычитателя | 1981 |

|

SU968818A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Устройство для контроля параметров | 1989 |

|

SU1667009A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| Накапливающий сумматор | 1982 |

|

SU1104506A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

Авторы

Даты

1982-05-07—Публикация

1980-06-30—Подача