Изобретение относится к устройствам контроля запоминающих устройст используемых в технологических процессах контроля электрических параметров больших интегральных схем памяти.

Цель изобретения - повьпиение полноты контроля и достоверности.

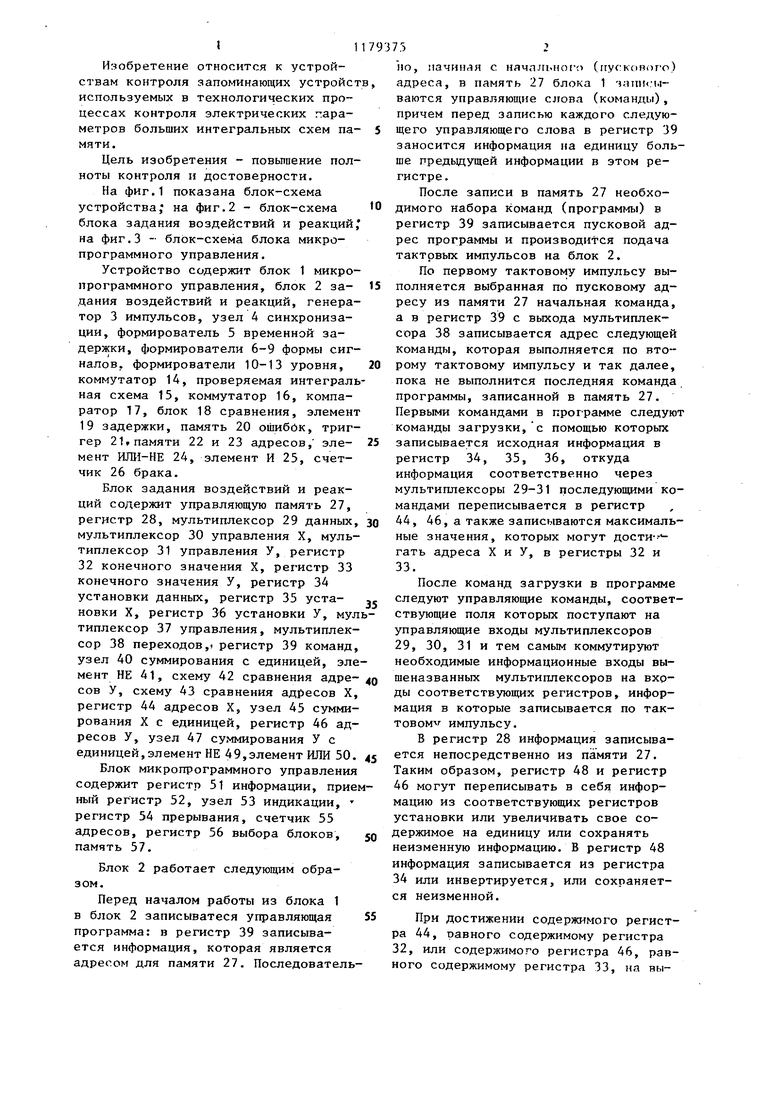

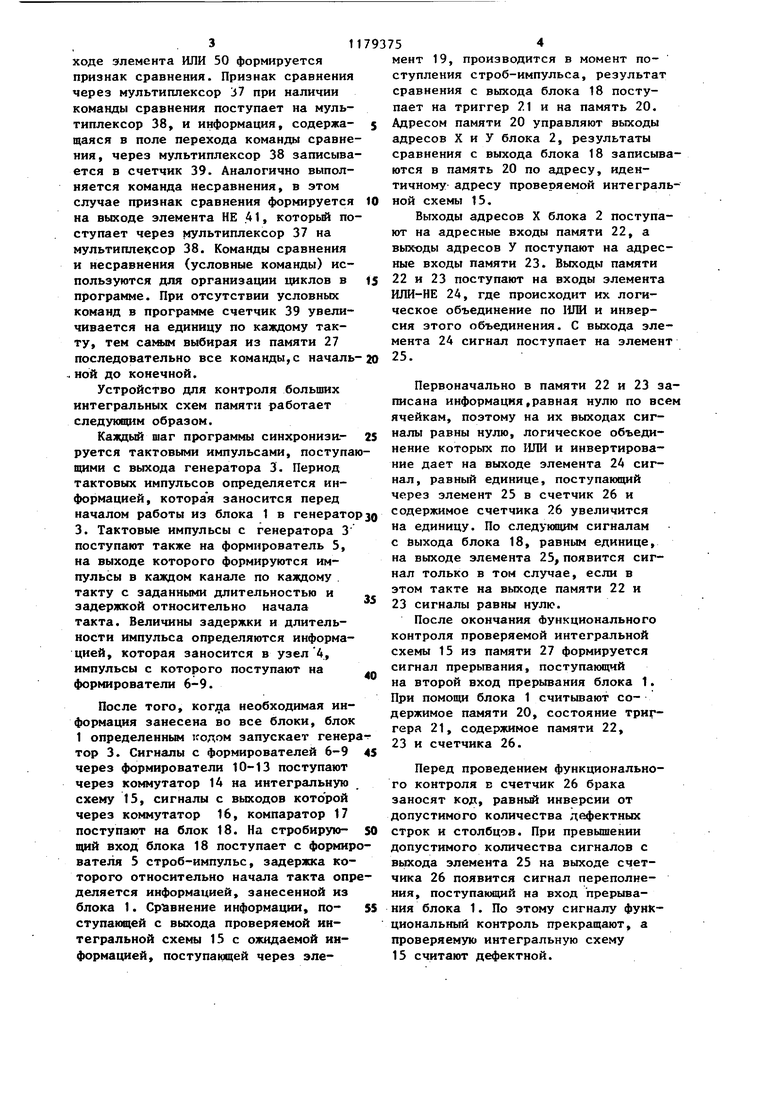

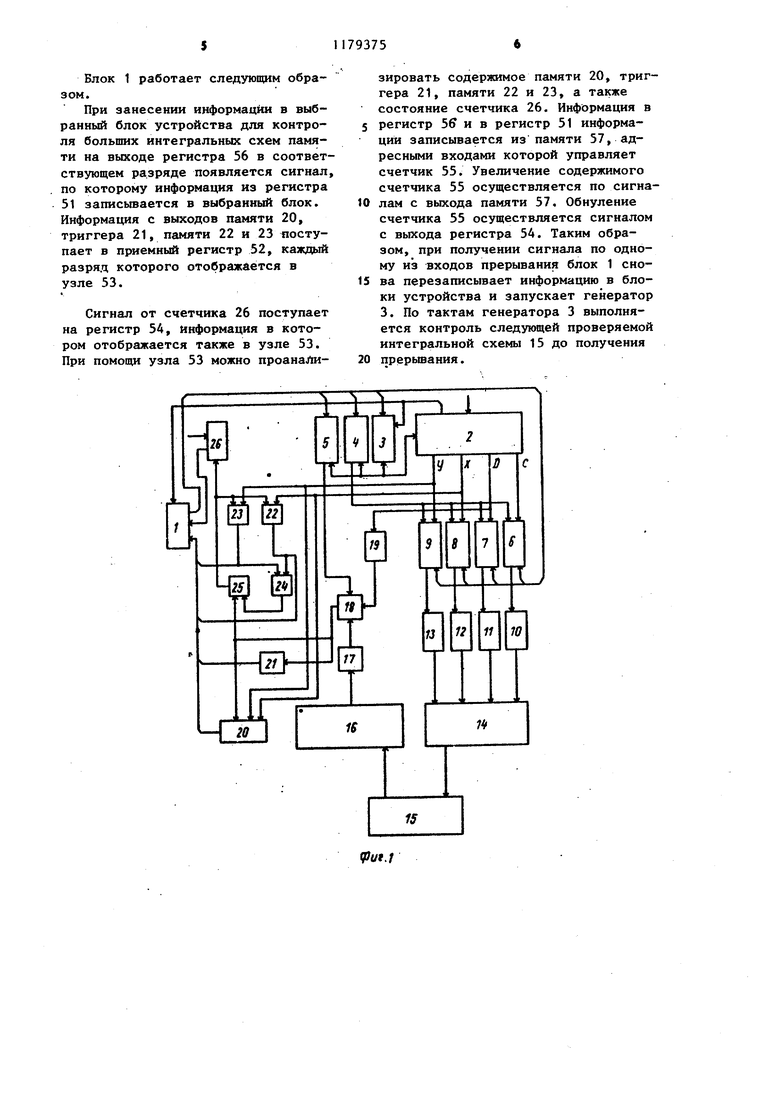

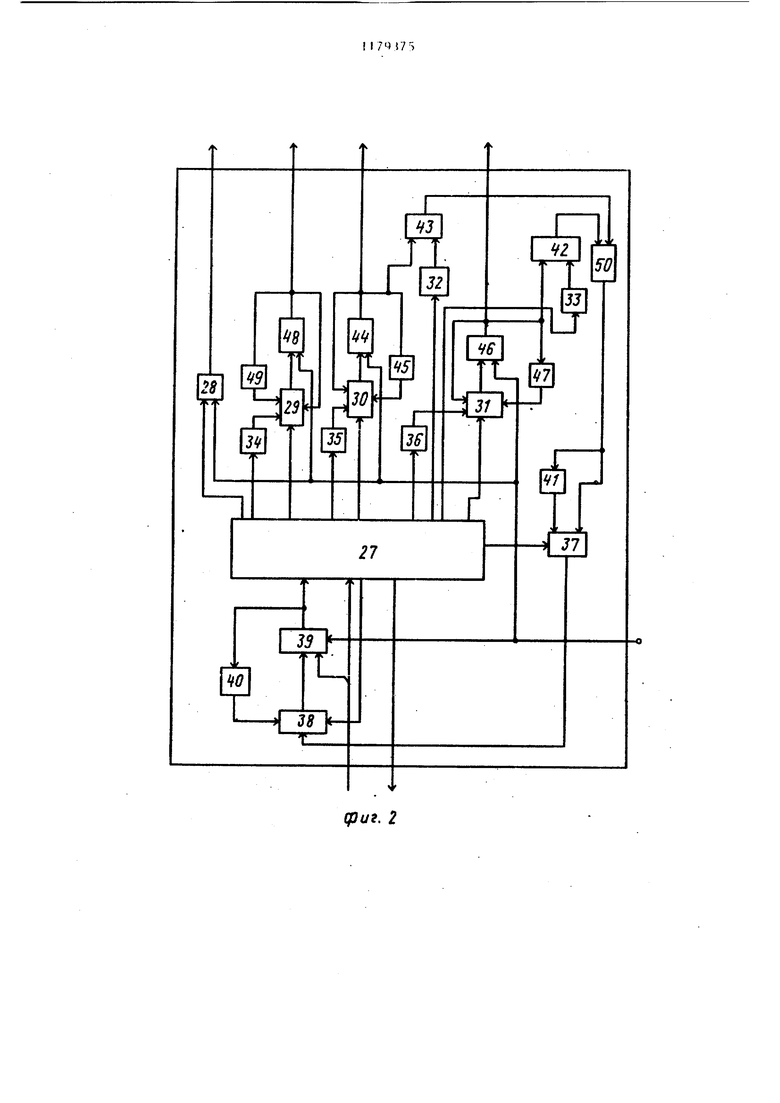

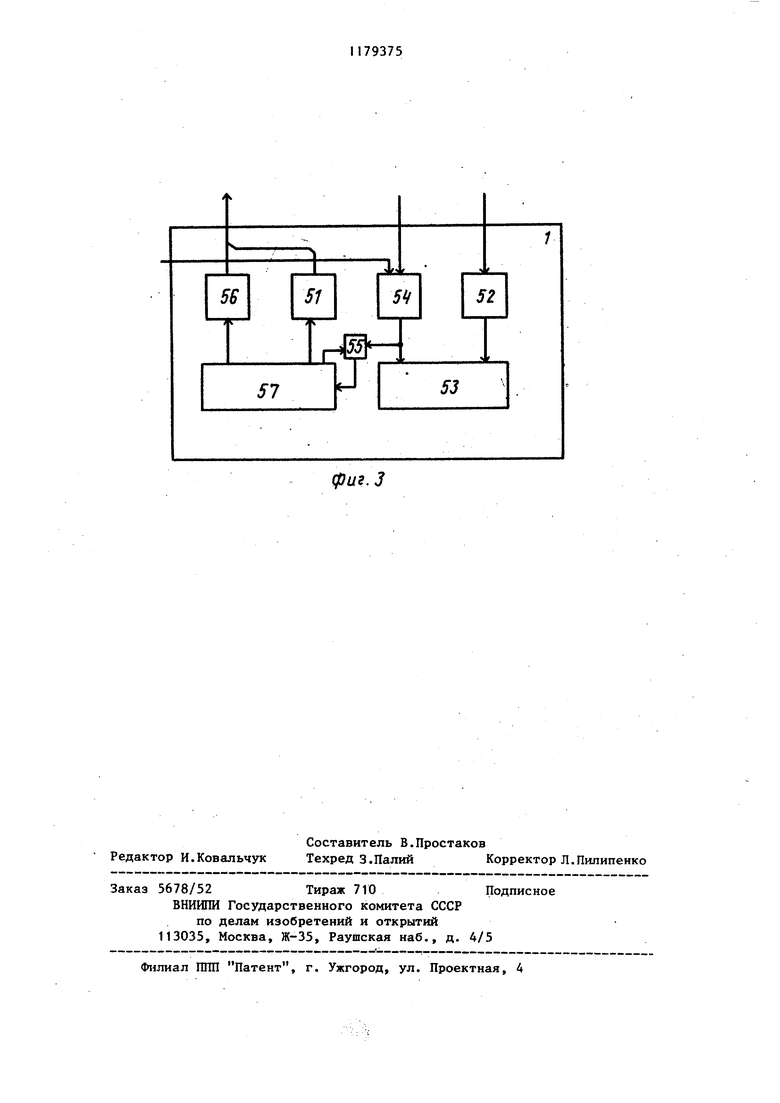

На фиг.1 показана блок-схема устройства; на фиг.2 - блок-схема блока задания воздействий и реакций, на фиг.З - блок-схема блока микропрограммного управления.

Устройство содержит блок 1 микропрограммного управления, блок 2 заДания воздействий и реакций, генератор 3 импульсов, узел 4 синхронизации, формирователь 5 временной задержки, формирователи 6-9 формы сигналов, формирователи 10-13 уровня, коммутатор 14, проверяемая интегральная схема 15, коммутатор 16, компаратор 17, блок 18 сравнения, элемент 19 задержки, память 20 ошибок, триггер 21 f памяти 22 и 23 адресов, элемент HJHi-HE 24, элемент И 25, счетчик 26 брака.

Блок задания воздействий и реакций содержит управляющую память 27, регистр 28, мультиплексор 29 данных, мультиплексор 30 управления X, мультиплексор 31 управления У, регистр 32 конечного значения X, регистр 33 конечного значения У, регистр 34 установки данных, регистр 35 установки X, регистр 36 установки У, мултиплексор 37 управления, мультиплексор 38 переходов,) регистр 39 команд, узел 40 суммирования с единицей, элемент НЕ 41, схему 42 сравнения адресов У, схему 43 сравнения адресов X, регистр 44 адресов X, узел 45 суммирования X с единицей, регистр 46 адресов У, узел 47 суммирования У с единицей,элемент НЕ 49,элемент ИЛИ 50.

Блок микропрограммного управления содержит регистр 51 информации, приеный регистр 52, узел 53 индикации, регистр 54 прерывания, счетчик 55 адресов, регистр 56 выбора блоков, память 57.

Блок 2 работает следующим образом.

Перед началом работы из блока 1 в блок 2 записыватеся управляющая программа: в регистр 39 записывается информация, которая является адресом для памяти 27. Последовательно, начинля с начпльного (пускового) адреса, в память 27 блока 1 чпписываются управляющие слова (команды), причем перед записью каждого следующего управляющего слова в регистр 39 заносится информация на единицу больше предьщущей информации в этом регистре .

После записи в память 27 необходимого набора команд (программы) в регистр 39 записывается пусковой адрес программы и производится подача тактовых импульсов на блок 2.

По первому тактовому импульсу выполняется выбранная по пусковому адресу из памяти 27 начальная команда, а в регистр 39 с выхода мультиплексора 38 записывается адрес следующей команды, которая выполняется по второму тактовому импульсу и так далее, пока не выполнится последняя команда программы, записанной в память 27. Первыми командами в программе следую команды загрузки, с помощью которых записывается исходная информация в регистр 34, 35, 36, откуда информация соответственно через мультиплексоры 29-31 последующими командами переписывается в регистр 44, 46, а также записываются максимальные значения, которых могут дости-.- гать адреса X и У, в регистры 32 и 33.

После команд загрузки в программе следуют управляющие команды, соответствующие поля которых поступают на управляющие входы мультиплексоров 29, 30, 31 и тем самым коммутируют необходимые информационные входы вышеназванных мультиплексоров на входы соответствующих регистров, информация в которые записывается по такTOBOMV импульсу.

в регистр 28 информация записывается непосредственно из памяти 27. Таким образом, регистр 48 и регистр 46 могут переписывать в себя информацию из соответствующих регистров установки или увеличивать свое содержимое на единицу или сохранять неизменную информацию. В регистр 48 информация записывается из регистра 34 или инвертируется, или сохраняется неизменной.

При достижении содержимого регистра 44, равного содержимому регистра 32, или содержимого регистра 46, равного содержимому регистра 33, на выходе элемента ИЛИ 50 формируется признак сравнения. Признак сравнения через мультиплексор 37 при наличии команды сравнения поступает на мультиплексор 38, и информация, содержащаяся в поле перехода команды сравнения, через мультиплексор 38 записывается в счетчик 39. Аналогично выполняется команда несравнения, в этом случае признак сравнения формируется на выходе элемента НЕ 41, который поступает через мультиплексор 37 на мультиплексор 38. Команды сравнения и несравнения (условные команды) используются для организации циклов в программе. При отсутствии условных команд в программе счетчик 39 увеличивается на единицу по каждому такту, тем выбирая из памяти 27 последовательно все команды,с началь.ной до конечной.

Устройство для контроля больших интегральных схем памяти работает следующим образом.

Каждый шаг программы синхронизнруется тактовыми импульсами, поступающими с выхода генератора 3. Период тактовых импульсов определяется информацией, которая заносится перед началом работы из блока 1 в генератор 3. Тактовые импульсы с генератора 3 поступают также на формирователь 5, на выходе которого формируются импульсы в каждом канале по каждому . такту с заданными длительностью и задержкой относительно начала такта. Величины задержки и длительности импульса определяются информацией, которая заносится в узел4, импульсы с которого поступают на формирователи 6-9.

После того, Korflia необходимая информация занесена во все блоки, блок 1 определенным кодом запускает генера тор 3. Сигналы с формирователей 6-9 через формирователи 10-13 поступают через коммутатор 14 на интегральную схему 15, сигналы с выходов которой через коммутатор 16, компаратор 17 поступают на блок 18. На стробирующий вход блока 18 поступает с формирователя 5 строб-импульс, задержка которого относительно начала такта определяется информацией, занесенной из блока 1. Сравнение информации, поступающей с выхода проверяемой интегральной схемы 15 с ожидаемой информацией, поступающей через элемент 19, производится в момент поступления строб-импульса, результа сравнения с выхода блока 18 поступает на триггер . 1 и на память 20. Адресом памяти 20 управляют выходы адресов X и У блока 2, результаты сравнения с выхода блока 18 записывются в память 20 по адресу, идентичному адресу проверяемой интегралной схемы 15.

Выходы адресов X блока 2 поступают на адресные входы памяти 22, а выходы адресов У поступают на адресные входы памяти 23. Выходы памяти

22н 23 поступают на входы элемента ИЛИ-НЕ 24, где происходит их логическое объединение по ИЛИ и инверсия этого объединения. С выхода элемента 24 сигнал поступает на элемен 25.

Первоначально в памяти 22 и 23 зписана информация,равная нулю по вс ячейкам, поэтому на их выходах сигналы равны нулю, логическое объединение которых по ИЛИ и инвертирование дает на выходе элемента 24 сигнал, равный единице, поступающий через элемент 25 в счетчик 26 и содержимое счетчика 26 увеличится на единицу. По следующим сигналам с выхода блока 18, равным единице, на выходе элемента 25,появится сигнал только в том случае, если в этом такте на выходе памяти 22 н

23сигналы равны нулю.

После окончания функционального контроля проверяемой интегральной схемы 15 из памяти 27 формируется сигнал прерывания, поступающий на второй вход прерывания блока 1. При помопщ блока 1 считьшают содержимое памяти 20, состояние триггера 21, содержимое памяти 22, 23 и счетчика 26.

Перед проведением функционального контроля Е счетчик 26 брака заносят код, равный инверсии от допустимого количества дефектных строк и столбцов. При превышении допустимого количества сигналов с выхода элемента 25 на выходе счетчика 26 появится сигнал переполнения, поступаю ций на вход прерывания блока 1. По этому сигналу функциональный контроль прекращают, а проверяемую интегральную схему 15 считают дефектной.

Блок 1 работает следующим образом.

При занесении информации в выбранный блок устройства для контроля больших интегральных схем памяти на выходе регистра 56 в соответствующем разряде появляется сигнал по которому информация из регистра 51 записьтается в выбранный блок. Информация с выходов памяти 20, триггера 21, памяти 22 и 23 поступает в приемный регистр 52, каждый разряд которого отображается в узле 53.

Сигнал от счетчика 26 поступает на регистр 54, информация в котором отображается также в узле 53. При помощи узла 53 можно проанализировать содержимое памяти 20, триггера 21, памяти 22 и 23, а также состояние счетчика 26. Информация в регистр 5в и в регистр 51 информации записывается из памяти 57, адресными входами которой управляет счетчик 55. Увеличение содержимого счетчика 55 осуществляется по сигналам с выхода памяти 57. Обнуление счетчика 55 осуществляется сигналом с выхода регистра 5А. Таким образом, при получении сигнала по одному из входов прерывания блок 1 снова перезаписывает информацию в блоки устройства и запускает генератор 3. По тактам генератора 3 выполняется контроль следующей проверяемой интегральной схемы 15 до получения

прерьшания.

дЭ(/г. 2

51

5S

51

Л г

5

52

53

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для записи и контроля программируемых блоков постоянной памяти | 1978 |

|

SU911613A2 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БОЛЬШИХ ИНТЕГРАЛЬНЫХ СХЕМ ПАМЯТИ, содержащее блок микропрограммного управления, выход которого соединен с управляющими входами генератора импульсов, узла синхронизации, формирователя временной задержки, блока задания воздействия и реакций, группы формирователей формЬ сигналов, задающий выход блока задания воздействий и реакций соединен с управляющим входом блока микропрограммного управления и входом останова генератора импульсов, выход которого соединен с синхронизирующими входами узла синхронизации формирователя временной задержки и блока задания воздействий и реакций, первый и второй адресные, управляющий и информационный выходы которого через соответствующие формирователи формы сигналов соединены с входами соответствующих формирователей -уровня группы, выходы которых через первый коммутатор соединены с выходом устройства, вход которого через соединенные последовательно второй коммутатор и компаратор соединен с первым входом блока сравнения, выход которого соединен с входом триггера, информационный выход блока задания воздействий через элемент задержки соединен с вторым входом блока сравнения, синхронизирующий вход которого соединен с выходом формирователя временной задержки, выход узла синхронизации соединен с синхронизирующими входами формирователей формы сигналов группы, отличающееся i тем, что, с целью повышения полноты контроля и достоверности, в него (Л введены счетчик брака, две памяти адресов, память ошибок, элемент ИЛИ-НЕ, элемент И, причем выход блока микропрограммного управления соединен с установочным входом счетчика брака, выход которого соединен с входом прерывания блока микро J программного управления, первый и второй адресные выходы блока задасо м ния воздействий и реакций соединены с информационными входами памяти ел ошибок и первой и второй памятей адресов, выходы которых через соединенные последовательно элементы ИЛИНЕ и И соединены с управляющими входами счетчика браков и обеих памятей адресов, выход блока сравнения соединен с управляющими входами элемента И и память ошибок, выходы последней, первой и второй памятей адресов и триггера соединены с информационным входом блока микропрограммного управления.

фиг.З

| Устройство для контроля больших интегральных схем памяти | 1980 |

|

SU926727A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Эйдукас Д.Ю., Орлов Б.В | |||

| Измерение параметров цифровых интегральных схем | |||

| М.: Радио и связь, 1982, гл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-08-20—Подача